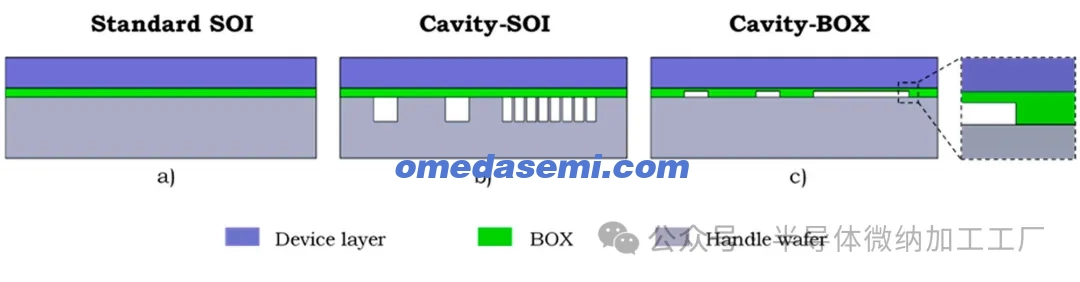

空腔绝缘体上硅(C-SOI)晶圆是一种前沿的绝缘体上硅技术,其衬底晶圆包含预先蚀刻好的空腔。这些空腔(有时也称作图案)通过向内键合的方式,最终在晶圆内部形成掩埋式空腔。它们在微机电系统(MEMS)技术中有诸多应用,并且相较于体硅微加工以及传统的绝缘体上硅技术具备诸多优势。 这项技术的一个主要优势在于,它降低了绝缘体上硅晶圆的器件层与衬底层之间的寄生电容。这将使器件能够更高效地运行。只要对其他变量加以控制,采用更深的空腔以及更小的键合区域能够进一步降低寄生电容。我们常见的键合技术 有硅玻璃键合 金金键合,金锡键合,金硅键合,临时键合等等 。但是当我们遇到一些需要低温键合,或者一些特殊材料时,或者应用场景时,上述键合方式很难满足一些特殊场景的应用,

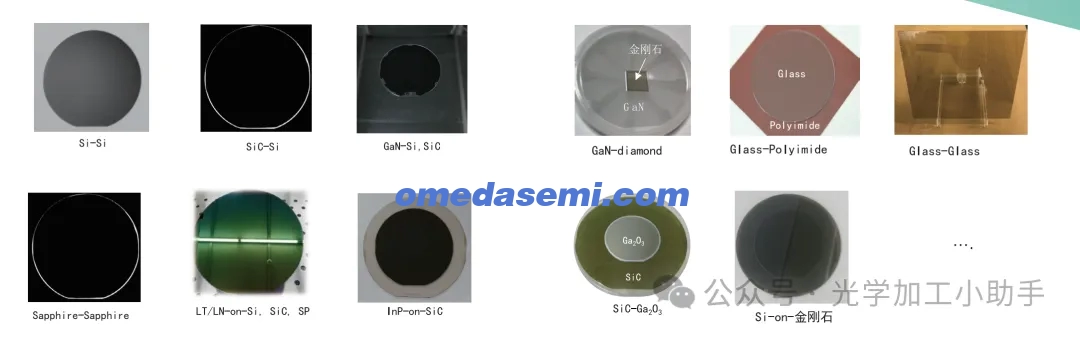

因此科学家提出了表面活化键合技术,这种技术 使键合技术所覆盖的材料范围更加广泛,比如

GaAs-SiC,InP-Diamond, LN-SiC,Si-Si,GaN-Dlamond,Sl-Diamond,蓝宝石-蓝宝石,金刚石-sic, sic-inp,sic-LN, ic-ga2o3,glass--glass,Si-SiC,Si-GaAs、GaAs- SiC、Si–SiC、SiC–SiC、Ge–Ge 、Al 2 O 3 -Al 2 O 3 ,GaP-InP, GaN-Si、LiNbO 3 -Al 2 O 3 、LiTaO 3 -Si and more(晶体,陶瓷,等等)

扩展的多材料的体系,将键合技术扩大了应用范围

*MEMS传感器 *光子集成电路 *半导体激光器

*功率器件 *3D封装 *异质集成

划重点--代工,代工,代工,卖设备

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜方式(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束直写等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

激光器芯片/探测器芯片/PIC芯片封装耦合服务"

请联系小编免费获取原文,也欢迎交流半导体行业,工艺,技术,市场发展

空腔绝缘体上硅(C-SOI)制造工艺: 空腔绝缘体上硅的制造工艺与更为传统的绝缘体上硅制造工艺略有不同,因为空腔的形成会带来不同的优势以及潜在的缺点。这一工艺主要针对微机电系统(MEMS)行业的应用进行了优化,不过它也有潜力在一系列应用中提升器件的性能。 在某些情况下,会在空腔内蚀刻出支柱以改善总厚度偏差(TTV)及器件性能。加入支柱能够制造出更高质量的硅膜(位于空腔上方的硅层),并提升空腔的均匀性,而且更高的纵横比会提高器件性能,同时改善光刻过程中的工艺控制。由于空腔的尺寸会改变器件层减薄的能力,所以加入支柱会影响总厚度偏差(TTV)以及晶圆的完整性。如果这些方面没有明确界定,就会影响共振特性,导致衬底的不同区域以不同幅度振动,进而可能导致非常高的总厚度偏差(TTV)、器件故障以及破损情况的发生。制造过程首先要进行清洁,以去除任何可能在制造过程中产生问题的表面颗粒。 2. 在衬底上应用光刻掩模,清晰地确定将蚀刻到晶圆中的空腔 为了制作图案,会在衬底上涂覆一层等离子聚合物薄膜。在这一步骤中,如果要使用支柱,也会对其进行定义。在许多项目中,使用支柱可以制造出更深的空腔和更高的纵横比,同时还能降低在蚀刻或二次加工过程中出现切口以及其他问题的风险。 3. 深度反应离子蚀刻(DRIE)去除材料以制造空腔,然后去除光刻胶 深度反应离子蚀刻(DRIE)会去除精确数量的硅,从而制造出由光刻掩模确定的空腔。未被光刻掩模覆盖的区域会通过离子轰击进行蚀刻,以制造出所需的空腔。在这一步骤中,会在空腔中切割出支撑支柱。深度反应离子蚀刻(DRIE)是最常用的方法,因为它具有较高的蚀刻速率均匀性和整体的简便性。由于这一过程需要液体蚀刻剂,随着技术的发展,该工艺将不断得到优化。 蚀刻速率根据空腔的宽度和纵横比在0.8μm/分钟到1.25μm/分钟之间变化。在蚀刻完空腔后,光刻掩模会被去除,留下一个带有图案的晶圆。在对晶圆进行蚀刻后,去除任何可能残留的多余硅和光刻胶非常重要,这可以避免在键合过程中出现问题。 热氧化物(或其他替代绝缘体)可以在蚀刻之前或之后进行沉积,在某些情况下,根据项目要求,也可能在这两个阶段都进行沉积。如果在蚀刻之前进行氧化物沉积,那么蚀刻过程将会穿过氧化物层直至衬底,蚀刻可能还会去除部分下方的衬底。根据深度不同,这可能会导致空腔壁上没有任何绝缘体。 当在蚀刻之后生长氧化物层时,空腔的角落处会形成一些小凸起。这些凸起的高度在5 - 20μm之间,会随绝缘膜的厚度变化而变化。由于二氧化硅形成的特性,这还会导致所有角落都略微变圆。为了达到最佳效果,空腔绝缘体上硅(CSOI)晶圆在真空中直接进行键合。这些晶圆使用水或类似的中性材料进行键合,然后在1100°C下退火长达2小时,以使键合更加牢固。退火后,晶圆之间的键合不再依靠胶粘剂。在真空中进行这一操作有助于防止空腔内残留多余空气及其他污染物。这也有助于在减薄盖帽晶圆时保持一致性,因为整个衬底内空腔的压力将会是均匀的。 7. 使用化学机械抛光(CMP)/氢氧化钾(KOH)蚀刻减薄顶部(器件)晶圆 必须将盖帽晶圆减薄至所需的器件层厚度。这是空腔绝缘体上硅(CSOI)制造过程中变数最大的步骤,因为减薄速率和质量在很大程度上取决于键合质量以及空腔的物理特性。在这个阶段,硅膜自然会发生振动,从而在这些区域产生不同的总厚度偏差(TTV)。在真空环境中进行之前的制造步骤有助于预防许多可能出现的此类问题。取决于应用和器件规格 与更传统的绝缘体上硅(SOI)不同,空腔绝缘体上硅(CSOI)晶圆在制造完成后可以进行二次背面加工。这意味着能够制造出极薄的膜、精细的表面结构、金属膜堆叠,并且总体上比传统绝缘体上硅晶圆拥有更多的设计自由度。 在不影响精度或质量的前提下降低器件成本。 减小器件尺寸。空腔的引入使得制造极薄的衬底/埋氧层/器件层成为可能。 对带有图案的晶圆进行键合能够实现绝缘体上硅(SOI)层的双面加工,并在微机械领域开拓了诸多可能性。 应用: 预先蚀刻的绝缘体上硅(SOI)晶圆是适用于各种应用中垂直和水平移动结构的平台,例如电容式惯性传感器、压力传感器、麦克风以及微流体器件等。 虽然目前其大部分用途都集中在微机电系统(MEMS)和传感器应用方面,但这些晶圆能够对任何绝缘体上硅(SOI)晶圆应用起到改进作用。