本文小编分享一篇文章,将双光子打印技术 与 硅光芯片晶圆的 测试结合在一起,通常硅光产品公司会在foundry进行流片,流片直接从封装厂拿晶圆回自己公司做后道加工,比如芯片的测试,切割,镀膜,端面抛光等工艺,这个里面对于硅光芯片的测试就需要用到探针卡,而硅光芯片属于光芯片主要的测试是对硅光波导出光口的光的检测,但是由于波导在侧面,通常先开槽,再测试,这个时候需要一个将光从平行方向上转到垂直方向上的透镜,然后耦合到光纤内,这个时候就需要透镜光纤,但是传统的透镜光纤为熔融,抛光工艺,这种工艺对于曲面的形状等有极大的限制,而双光子3d打印技术就有极大的自由性,欧洲phix公司就是其中代表。

划重点(双光子3D打印代工)

在光纤端面亦或其他基底材料上通过双光子3D打印的方式一直是科研工作者研究的关注点,但是由于高精度双光子3D打印的设备极其昂贵,技术也较为前沿,许多科研工作者乏于寻找可靠的,高效率的加工提供商。。

因此如果您有需求,可以联系小编为您推荐成熟的双光子3D打印企业,加速您的创新。

如果你也爱好 半导体,光学,光纤,硅光集成等技术及应用,可以添加小编,一起畅聊技术,市场和应用。

看原文请联系小编免费领取

光子集成电路的晶圆级探测是先进生产工作流程中可靠过程控制和高效性能评估的关键。近年来,垂直腔激光器、顶照式光电二极管或带有表面发光光栅耦合器的硅光子电路等表面耦合器件的光学探测取得了长足的进步。与此相反,在深蚀刻切割沟槽的侧壁上具有难以接近的垂直刻面的边缘发射器件的晶圆级探测仍然是一个重大挑战。在本文中,我们通过引入一种基于3D打印自由曲面耦合元件的光学探针的新概念来应对这一挑战,这些探针适合晶圆表面的深度蚀刻切割沟槽。利用双光子激光光刻的设计自由度和精度,耦合元件可以适应各种模场尺寸。我们通过实验证明了该方法的可行性,方法是将光耦合到不同集成平台上的边缘发射波导,例如硅光子学(SiP),氮化硅(TriPleX)和磷化铟(InP)。我们认为,3D打印的耦合元件实现了每个耦合接口低至1.9 dB的损耗,代表了边缘耦合光子集成电路的高度可重复晶圆级测试的关键一步。

1. 引言

光子集成电路 (PIC) 的大规模生产需要在制造过程的早期以及进入昂贵且复杂的制造步骤(如芯片分离、抗反射涂层和封装)之前进行高通量晶圆级测试,以表征器件性能。为此,光必须有效地耦合,并在面内波导和面外方向的单模光纤 (SMF) 之间实现高再现性。目前,PIC的光学晶圆级探测主要依赖于通过光栅结构的表面耦合[1,2]。然而,虽然光栅耦合器(GC)已广泛用于绝缘体上硅(SOI)[2]或氮化硅(Si 3 N 4 )[3,4]波导,但它们在其他平台上并不常见,例如磷化铟(InP)或低折射率平面光波电路(PLC)。此外,目前的PIC设计越来越依赖于边缘耦合(EC),在硅光子学[5,6]的情况下也是如此,它提供了较大的传输带宽,并允许基本上平面封装架构。相关的波导面通常是通过晶圆表面的深蚀刻沟槽制备的,因此无法用普通 SMF 访问。为了克服这个问题,提出了基于PLC的光学探针,该探头具有抛光的45°端面,用于将来自面外SMF阵列的光耦合到面内Si 3 N 4 波导阵列[7]。然而,这种方法仅限于相当大的模场直径(MFD),例如10 μm,并导致相对较高的插入损耗,例如每个耦合接口5.7 dB [ 7]。将这一概念应用于具有较小MFD的高折射率对比度波导的测试具有挑战性,因为基于PLC的探头会发射直径大于10μm的发散光束。另一种方法不是在SMF侧使用探针,而是在芯片侧使用重定向镜像[8]。在这个概念中,来自高折射率片上波导的光通过金属涂层的曲面聚合物微镜被重定向到表面法线方向,该微镜使用灰色光刻和电子束蒸发在深蚀刻切割沟内制造[8]。根据这一概念,已经证明了高数值孔径 SMF 和锥形硅光子 (SiP) 波导之间的耦合损耗为 3.2 dB。然而,相关金属涂层微镜的制造复杂、昂贵,并且不可避免地受到结构变化的影响,导致光耦合效率的不确定性,从而掩盖了被测电路的性能。

在本文中,我们展示了一种技术简单且普遍适用的方法,用于边缘耦合光子集成电路的低损耗、高通量光学晶圆级探测。我们的概念依赖于3D打印的自由曲面微光学元件[9],这些元件可以在标准SMF的端面上高精度制造,并且旨在有效地将光耦合到深蚀刻沟槽侧壁的波导面[10]。每个耦合元件都包含一个全内反射 (TIR) 反射镜,用于将光从平面外方向重定向到平面内方向,然后是一个非球面透镜,允许将模式场与相应的波导类型相匹配。利用 3D 打印自由曲面光学元件的巨大设计自由度,我们设计了短焦距镜头,也可用于狭窄的沟槽。我们通过探测Si 3 N 4 波导(Lionix TriPleX,MFD D = 10μm),基于InP的埋藏异质结构分布式反馈(DFB)激光器(MFD D WG,TriPleX WG,InP = 3μm)和SiP电路(MFD D WG,SiP = 2.5μm)来实验证明我们概念的可行性。我们实现了低至2.7dB (TriPleX)、1.9dB (InP)和1.9dB (SiP)的耦合损耗。对于硅光子芯片,我们还研究了18种不同波导面和耦合元件组合的耦合损耗的再现性,发现平均值为2.23dB,标准偏差为0.14dB。

2. 概念

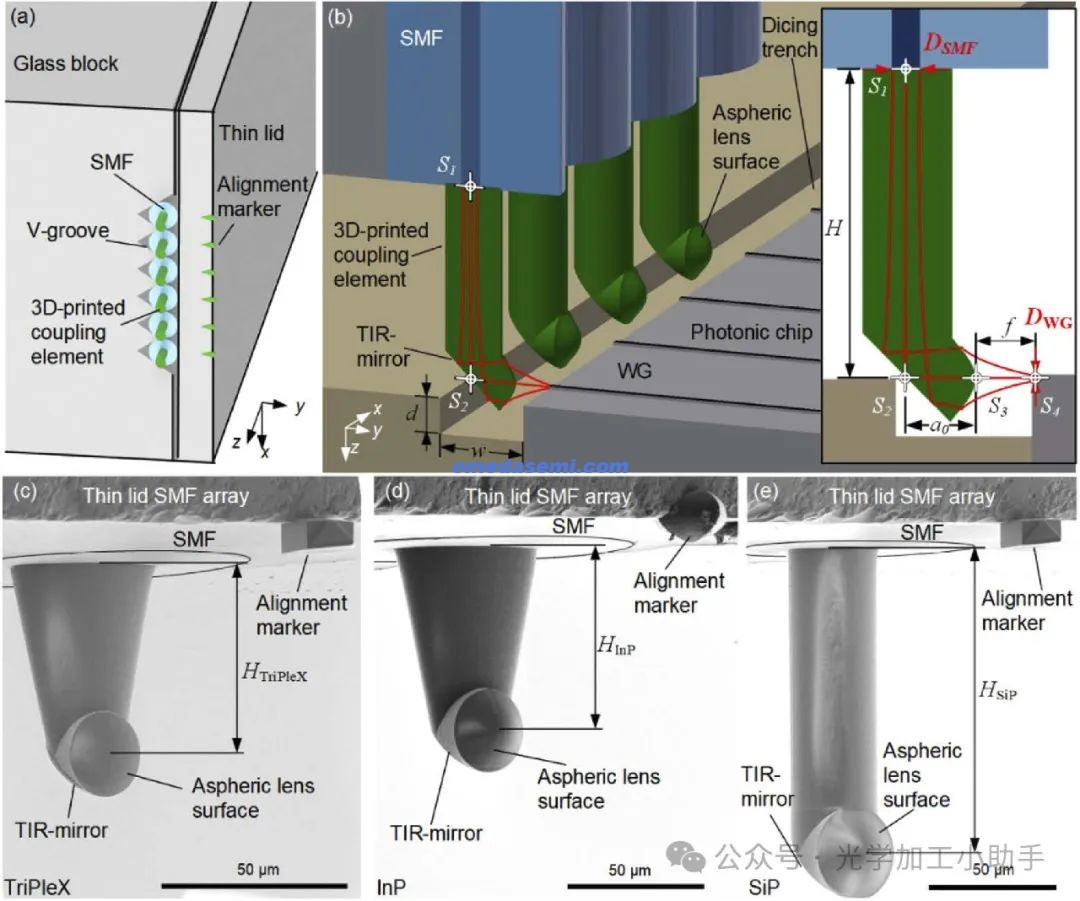

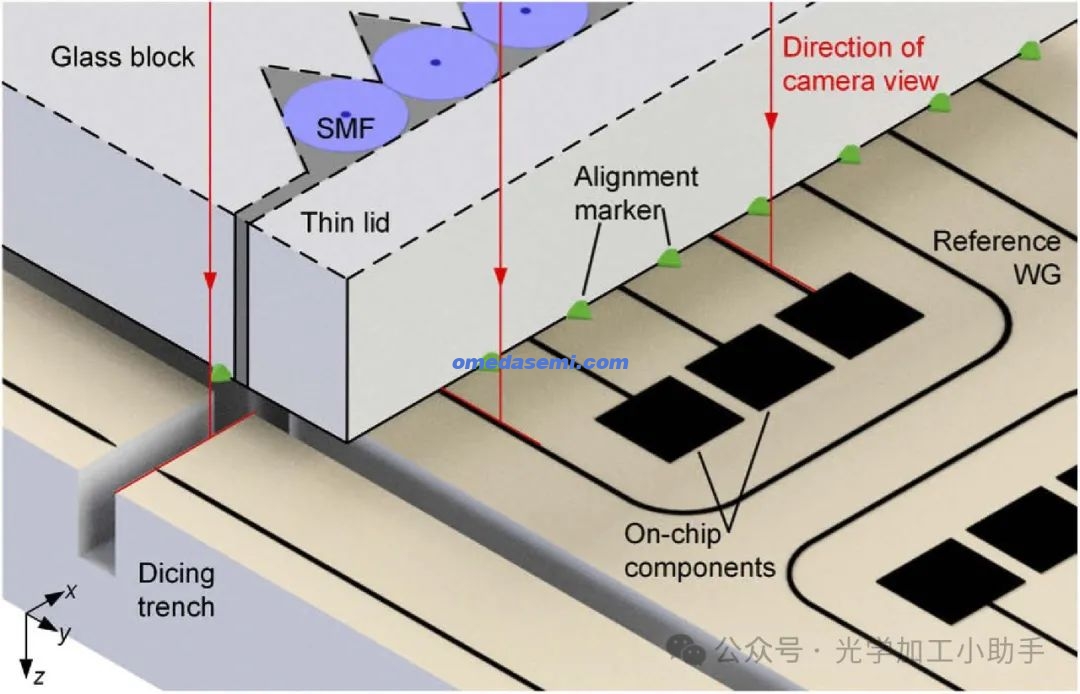

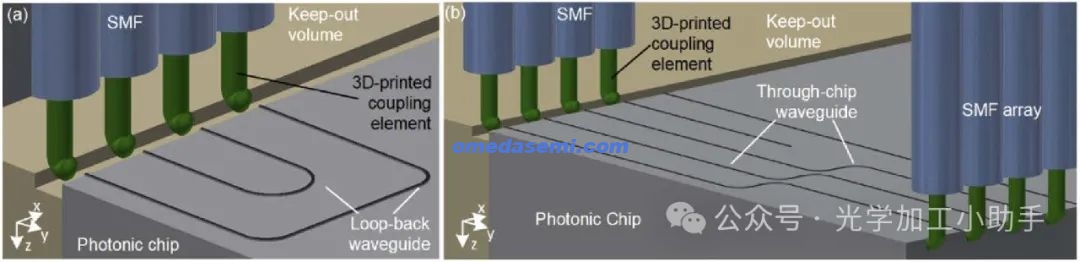

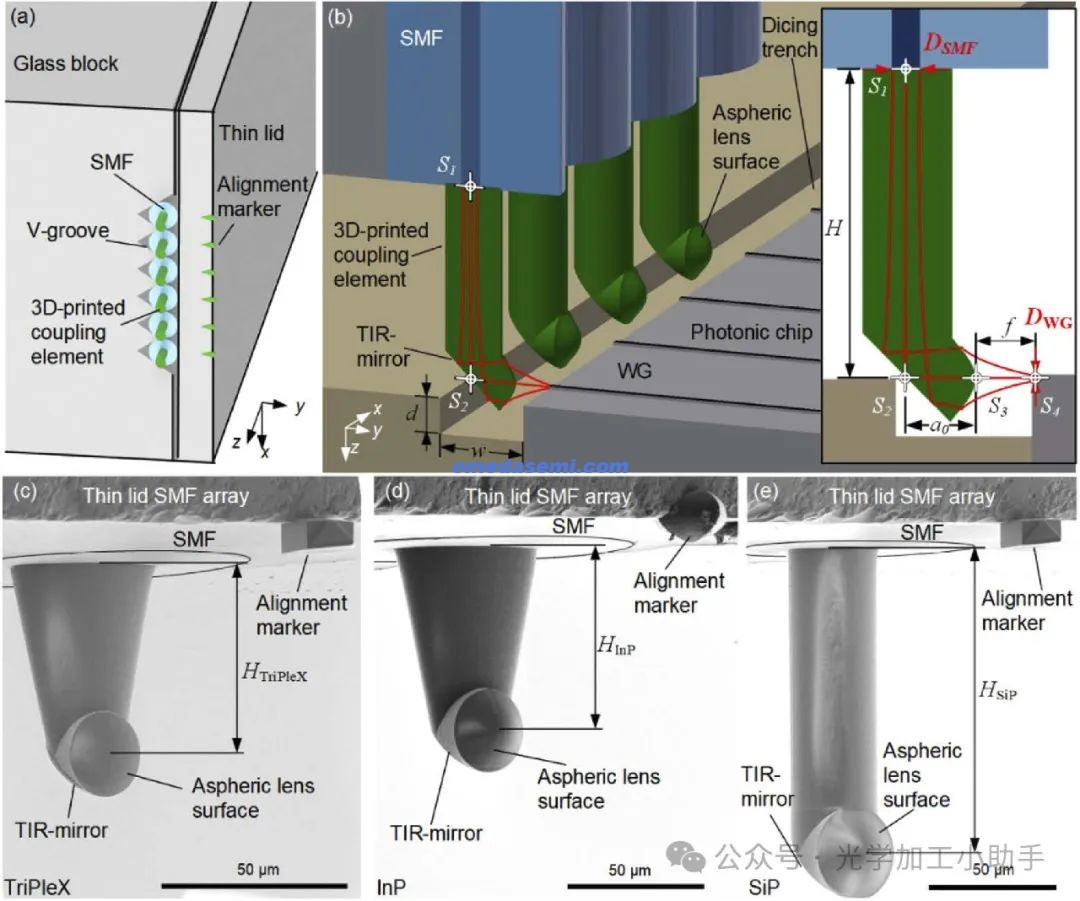

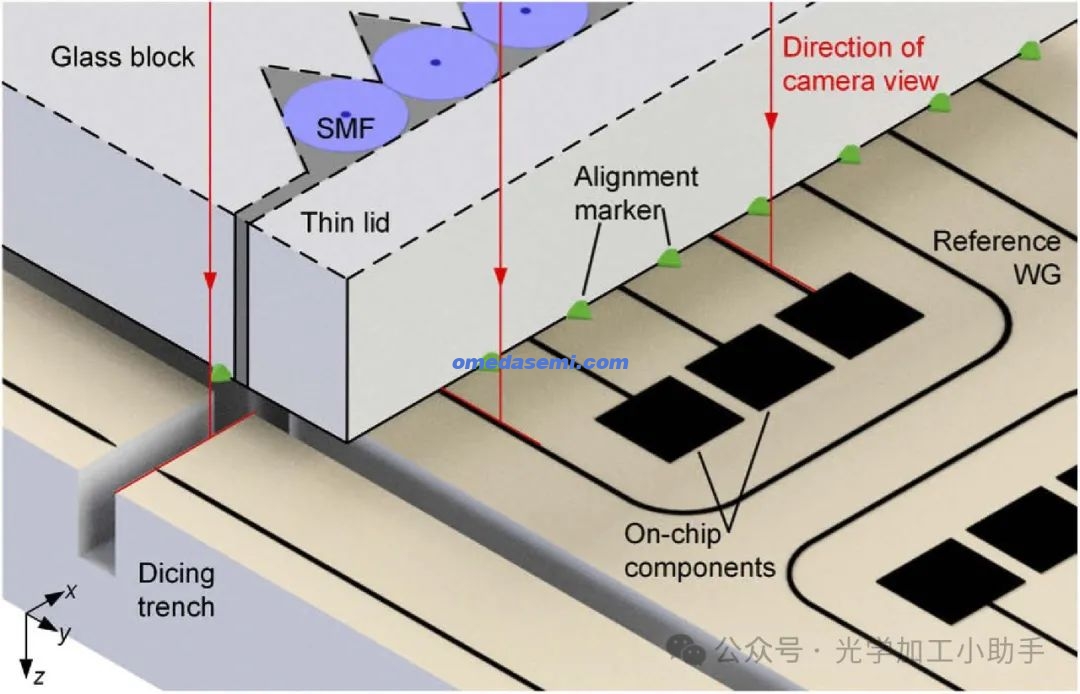

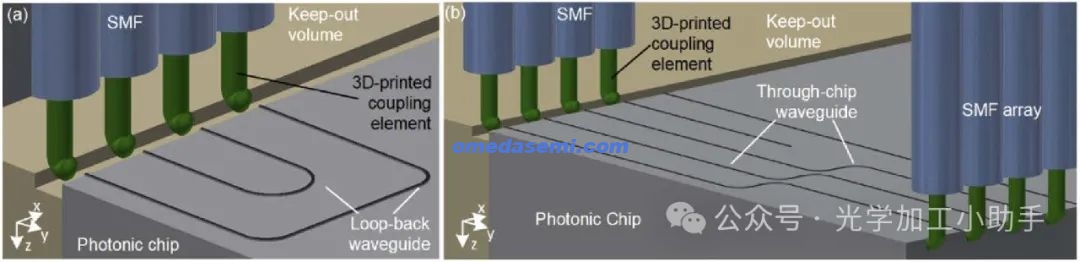

使用 3D 打印光学耦合元件进行晶圆级探测的概念如图 1 所示。自由曲面耦合元件直接打印在标准 SMF 阵列的面上,见图 1(a)。平面全内反射 (TIR) 反射镜将光束从面外方向重定向到面内方向,并使用自由曲面非球面透镜将片上波导面处的光束腰直径与相应的模场尺寸相匹配,如图 1(b) 所示。自由曲面光学耦合元件设计用于将 SMF 面(点 S)处的光束直径 D 转换为波导面(点 S 4 1 )处的直径 D WG SMF ,同时安装在宽度 w ≥ 50 μm 和深度 d ≥ 20 μm 的标准切割沟中。点 S 和 S 2 3 分别表示光束轴与 TIR 反射镜的交点和非球面透镜的顶点。为了实现高效耦合,非球面透镜的光轴 ( 𝑆2𝑆3�2�3 ) 与片上波导对齐。为了防止在对准探头时造成机械损坏,距离 H = |𝑆1𝑆2||�1�2¯| 选择得足够大,通常在 (50...130)μm,见图1(b)。请注意,从 SMF 面发射的发散光束在 3D 打印耦合元件的主体中自由传播,直到到达 TIR 反射镜,因此沿线 𝑆1𝑆2�1�2¯ 的结构的确切外部形状对光学性能没有任何影响。在我们的实验中,我们尝试了不同的几何形状,例如,向SMF面的直径增加,如图1(c)和(d),或由直径恒定的更细长的结构组成,如图1(e),这可以减少写入时间,而不会对光学行为产生任何影响。

图1.使用3D打印耦合元件的晶圆级光学探测的概念。(a) 打印到单模光纤(SMF)阵列端面的3D自由曲面耦合元件(绿色)示意图。SMF 阵列由一个带有 V 形凹槽的玻璃块和一个薄玻璃盖组成。3D打印的自由曲面元件允许光子芯片上的面外光纤和面内波导之间的光有效耦合。对准标记(绿色)印在盖子的前边缘,以方便探头相对于片上波导进行基于视觉的对准,见图2。(b) 光学探头的特写视图,其中3D打印的耦合元件(绿色)插入深蚀刻的切割沟(宽w,深d)。为了说明,省略了图1(a)所示的薄盖,并且沿着第一根光纤的光轴切开探头。从 SMF 发出的光首先以高斯光束(红色)的形式自由传播,腰部直径为 D SMF ,位于每个耦合元件的主体中。全内反射 (TIR) 反射镜将光束重定向,然后由自由曲面非球面透镜聚焦到光束腰部直径 D,该光束腰部直径 D WG 与蚀刻面上集成光学片上波导的模场大小相适应。为了实现高效耦合,非球面透镜的光轴 𝑆2𝑆3�2�3¯ 与片上波导对齐。插图显示了切割-打开耦合元件的放大图,其工作距离 f、距 TIR 反射镜的距离 a 0 以及 SMF 端面与非球面透镜光轴 𝑆2𝑆3�2�3¯ 之间的距离 H。(c)–(d) 设计用于耦合不同距离 H 的 (c) TriPleX、(d) InP 和 (e) SiP 波导的单个耦合元件的扫描电子显微镜 (SEM) 图像。请注意,(c)的比例与(d)和(e)中的比例不同

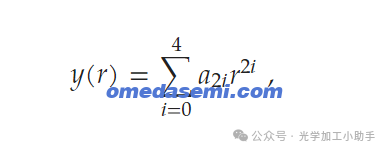

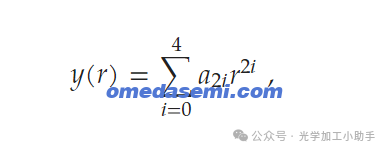

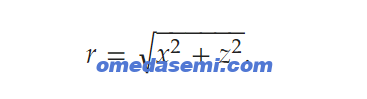

为了优化透镜的折射表面,我们用其轴向位置 y 表示旋转对称的自由曲面,作为到光轴的径向距离 r 的函数,我们用参数 a 2i 的偶多项式表示,i=1,...,4,

其中,与光轴的径向偏移由下式给出

方程中使用的坐标 x、y 和 z。( 1) 和 ( 2) 是相对于其原点位于光束轴和 TIR 反射镜的交点 S 2 的坐标系定义的,见图 1(b) 的插图。x、y 和 z 轴的方向由图 1(b) 左下角的坐标系定义。因此,多项式参数 a = 定义了透镜顶点沿光路的位置,而折射表面的形状由参数 a 、 a 、 6 a 和 a 8 2 4 0 确定。 |𝑆2𝑆3||�2�3¯|

为了对透镜参数进行数值优化,我们假设一个旋转对称的高斯光束轮廓,其腰部位于 SMF 端面上,其中强度分布的

1/𝑒21/�2 直径为 D SMF = 10.4 μm [ 11]。为简单起见,芯片面的目标场也由具有平坦相位前沿的旋转对称高斯近似,其直径 D WG 适用于片上波导的 MFD。请注意,这种方法可以通过扩展方程来扩展到椭圆模场形状。( 1) 和 ( 2) 到非旋转对称的透镜表面。为了优化透镜表面,我们将高斯光束的传播长度 𝐿=𝐻+𝑎0�=�+�0 固定在耦合元件的主体内,并对参数 a 2i , = 1...4,在工作距离f到芯片面的最小值保持20μm的约束下,为了获得最佳耦合效率,从而降低探头对准过程中机械损坏的风险。请注意,对于片上波导的给定模场直径,只有当耦合元件主体内弱发散高斯光束的传播长度 L 选择足够大时,才能满足规定的最小工作距离 f 的要求如果选择的 L 太小,则非球面透镜平面中的光束直径太小, 导致工作距离 f 低于最小规定值。

如果蚀刻波导面处的目标MFD超过5μm,我们可以使用商业设计程序(OpticStudio的物理光学传播模块,Zemax [12])进行透镜优化。对于较小的MFD,我们利用了基于[13]中描述的技术的波传播算法(WPA)的自制实现,并且对于强发散或会聚波束也产生了可靠的结果。对于每个光学集成平台,我们设计了一个专用探头,该探头面向相应片上波导的MFD。使用高斯起始场和靶场,我们根据WPA方法实现了96%(TriPleX,D = 10 μm),94%(InP,D = 3 μm)和89%(SiP,D WG,TriPleX WG,InP WG,SiP = 2.5 μm)的理论耦合效率,不考虑菲涅耳反射。图1(c)-(e)显示了TriPleX、InP和SiP平台的制备耦合元件的扫描电子显微镜(SEM)图像。请注意,即使是理论耦合效率也无法达到 100%。我们将其归因于这样一个事实,即我们的系统仅包含一个经过优化的自由曲面——单曲面设计对于在近轴近似有效范围内传播的高斯光束来说就足够了,但不允许匹配具有小光斑尺寸和非高斯强度分布的强发散光束的振幅和相位分布。在SiP面的情况下, 1/𝑒21/�2 强度分布的半角为22°,这显然超出了通常用于定义近轴近似有效范围的11°极限[14]。我们预计,具有多个形状优化光学表面的更复杂的探针设计,结合更精确的建模工具,以及更准确地表示小平面上的非高斯波导模式场,将进一步提高我们的3D打印耦合元件的理论和实验证明的效率。

为了测试集成波导阵列,可以在光纤阵列 (FA) 上实现 3D 打印的光学探针,其间距为 127 μm 或 250 μm,见图 2。通过使用薄型 SMF [ 15] 或多芯光纤 [ 16] 阵列,纤芯沿光纤端面上的一条线排列,也可以获得较小间距的探头,例如 80 μm 或 35 μm。FA前缘的3D打印对准标记(见图1(a)和图2)可用作参考,以促进基于视觉的耦合元件相对于带有顶视摄像头的晶圆探针器中的片上结构的粗略对准。在(x.y)平面上粗略对准后,探头沿z轴下降,将耦合元件引入沟槽中,并采用主动对准技术细化最佳耦合位置。

图2.通过3D打印的对准标记(绿色)对光学探针相对于片上结构的粗略对准。为了说明,光纤阵列的顶部被切掉了。为了在晶圆探针机的俯视相机中进行粗略定位(观察方向用红线表示),标记物与芯片上的波导和包含波导面的切割沟槽的侧壁对齐。然后通过主动对准技术优化耦合效率。

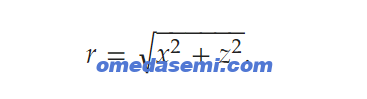

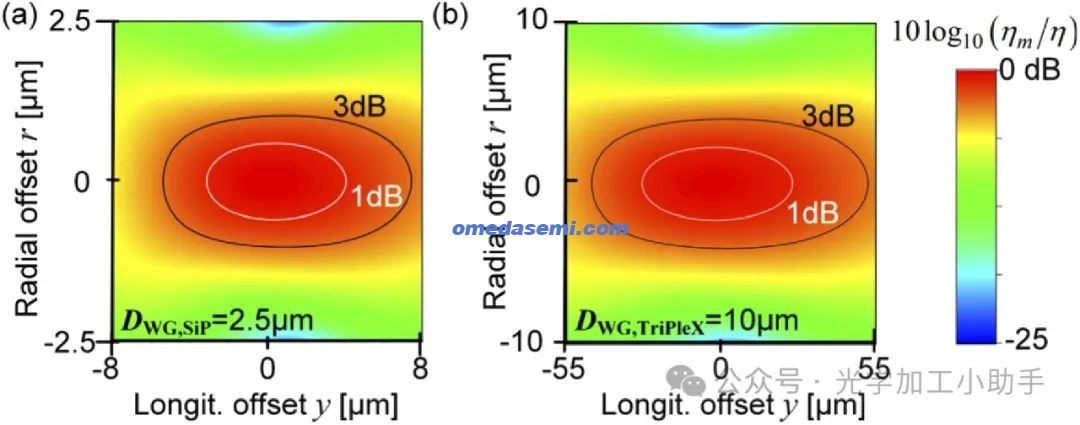

为了估计对准精度对光耦合效率的影响,我们模拟了超额耦合损 10log10(𝜂𝑚/𝜂(𝑟,𝑦))10log10(��/�(�,�)) 耗作为径向偏移和与最大耦合效率 𝜂𝑚=𝜂(0,0)��=�(0,0) 的最佳位置的纵向偏移 𝑟=𝑥2+𝑧2−−−−−−√�=�2+�2 𝑦� 的函数关系。我们假设目标波导的高斯MFD WG,SiP D = 2.5 μm,对应于小型硅光子(SiP)波导,或者,高斯MFD D WG,TriPleX = 10 μm的波导代表大型TriPleX波导。结果如图3所示。相应的工作距离,见图1(b)中的插图,分别为f = 25 μm和f SiP TriPleX = 40 μm。硅光子波和TriPleX波导的仿真最大耦合效率分别为 𝜂𝑚,SiP��,SiP = 0.89(0.50 dB损耗)和 𝜂𝑚,TriPleX��,TriPleX = 0.97(0.13 dB损耗)。对于目标MFD D WG,SiP = 2.5 μm的SiP波导,1 dB (3 dB)超额损耗的可容忍径向偏移量为0.6 μm (1 μm),而相应的纵向偏移容差为−3 μm / +4 μm (−5 μm / +7 μm)。对于TriPleX波导的目标MFD D WG,TriPleX =10 μm,1 dB (3 dB)过量损耗的径向偏移容差为2.2 μm (4 μm),而纵向偏移容差为−28 μm / +25 μm (−46 μm / +52 μm)。主动对准所需的精度非常符合市售光学探测系统规定的100 nm的典型定位步长[17,18]。请注意,对于集成波导阵列的探测,不仅对准台的定位精度,而且光学探针的间距精度和 3D 打印元件的制造公差都可能导致过度的耦合损耗。由于耦合元件在制造过程中与各自的光纤纤芯精确对齐,因此其间距精度主要由底层光纤阵列的间距精度决定,其典型变化± 0.3 μm [ 19]。第 4 节更详细地讨论了这种影响。

图3.对准公差分析。这些图像显示了根据功率耦合效率η(r,y)与最佳耦合位置的径向偏移r和纵向偏移y的函数计算得出的颜色编码的模拟超额耦合损 10log10(𝜂𝑚/𝜂(𝑟,𝑦))10log10(��/�(�,�)) 耗,η实现了最大耦合效率。 m 探针光纤端面的输入高斯模场直径为 D SMF = 10.4 μm。(a) 耦合到小硅光子 (SiP) 片上波导,其模场直径为 D WG,SiP = 2.5 μm。最大耦合效率为η m,SiP = 0.89(0.5 dB损耗)。径向 1 dB (3 dB) 对准容差为 ± 0.6 μm (± 1 μm),纵向 1 dB (3 dB) 容差为 −3 μm / +4 μm (−5 μm / +7 μm)。(b) 耦合到模场直径为 D WG,TriPleX = 10 μm 的 TriPleX 片上波导。最大耦合效率为η m,TriPleX = 0.97(0.13 dB损耗)。径向 1 dB (3 dB) 对准容差为 ± 2.2 μm (± 4.0 μm),纵向 1 dB 偏移容差为 −28 μm / +25 μm (−46 μm / +52 μm)。

3. 制造

使用定制的双光子光刻系统(Nanoscribe Photonic Professional GT,40×物镜,NA = 1.4)将耦合元件打印在标准SMF阵列的面上,并辅以专有控制软件。3D 结构是通过将不同层上的连续线条写入负色调光刻胶来构建的。在我们的实验中,线之间的书写距离(阴影线)和层间距(切片)都设置为 100 nm,以生成 TIR 反射镜和透镜的光滑反射和折射表面。自动检测每个 SMF 的磁芯,并将耦合元件及其关联的对齐标记写入单个写入字段,以避免拼接错误。类似的工艺以前已被用于制造用于芯片-芯片连接的 3D 自由曲面波导,即所谓的光子引线键合 [ 20, 21],或用于光学驱动扫描探针显微镜 (SPM) 引擎的 3D 打印 [ 22]图1(c)、(d)和(e)显示了为SiP、InP和TriPleX波导设计的光耦合元件的SEM图像。对于为SiP波导设计的耦合元件,光束需要聚焦到相当小的MFD D WG,SiP = 2.5 μm。这需要高数值孔径 (NA),结合 f SiP = 25 μm 的工作距离,导致在透镜顶点 S 3 的横截面中具有相当大的 23 μm 光束直径。对于 SMF 表面给定的腰部直径 D SMF ,透镜处的光束直径决定了光束在耦合元件主体内的传播距离,对于 SiP 设计来说,这相当于

𝐿SiP=𝐻SiP+𝑎0,SiP�SiP=�SiP+�0,SiP = 164 μm。对于为TriPleX波导设计的耦合元件,D WG,TriPleX = 10 μm的目标MFD更大,因此耦合元件中的传播距离可以减少到 𝐿TriPleX=𝐻TriPleX+𝑎0,TripLeX�TriPleX=�TriPleX+�0,TripLeX = 90 μm。虽然在片上波导面上较大的MFD D可以减少给定D WG 值所需的耦合元件总长度L SMF ,但另一种可能的解决方案是减少工作距离f,以实现更小的透镜表面光束直径。为了耦合到InP波导的小型MFD D WG,InP = 3 μm,选择工作 InP 距离f = 20 μm,这将耦合元件中的几何传播距离减小到 𝐿InP=𝐻InP+𝑎0,InP�InP=�InP+�0,InP = 95 μm。选择耦合元件的直径是为了给从 SMF 发射的发散光束提供足够的空间,该光束在 3D 打印的耦合元件中自由传播。

4. 实验验证

为了证明我们概念的可行性,我们对在三个不同平台上实现的集成边缘发射波导进行了耦合实验,即在刻面处目标MFD为D = 10 μm的Si 3 N 4 波导(Lionix TriPleX),基于InP的DFB激光器(D = 3 μm)和SiP电路(D WG,TriPleX WG,InP WG,SiP = 2.5μm)。由于缺乏完整的晶圆,我们在深蚀刻沟槽中配备了刻面的切片芯片上进行了这些测量。然而,由于探针的紧凑性,这不应该代表与片上探测的根本区别。为了使耦合元件相对于波导面对齐,我们使用一对六轴定位平台并手动优化以获得最佳耦合效率。

为了耦合到MFD相当大(D WG,TriPleX =10 μm)的TriPleX [ 23]波导,我们使用边缘耦合器之间间距为250 μm的环回波导。波长为 1550 nm 的光的耦合和耦合是通过公共光纤阵列上的不同耦合元件完成的,见图 4(a)。每个耦合测得的损耗为2.7 dB,可以认为这是一个保守的估计值,因为在这种情况下,我们假设使用无损片上波导。作为参考,我们还将来自3D打印耦合元件的光耦合到MFD为10.4 μm的SMF面上,这导致耦合损耗仅为1.6 dB,测得的1 dB横向对准公差为±2.3 μm,与仿真结果非常吻合,见图3(b)。我们将芯片探测实验中略高的耦合损耗归因于TriPleX芯片面的显著粗糙度。尽管如此,测得的耦合损耗仍远小于之前在片上Si 3 N 4 波导和基于PLC的光学探头之间耦合的5.7 dB,这些探头具有抛光的45°端面[7]。在这种情况下,需要注意的是,我们的 3D 打印耦合元件将光聚焦到距离镜头顶点的工作距离 f = 40 μm 的点。如果片上波导的尖端从深蚀刻切割沟的侧壁略微缩回,则相关的焦点甚至可以移动到芯片边缘之外。与我们的布置相反,基于PLC的探头发射的光束的腰部始终位于探头内部或其面,需要靠近波导端面,从而承担损坏探头和/或芯片边缘的风险。

图 4.艺术家对使用 3D 打印耦合元件进行光学探测的设置的印象。(a) 环回波导的测量:为了实现最佳耦合,SMF阵列与3D打印耦合元件的位置和方向在六个自由度上进行调整,包括沿x轴、y轴和z轴的平移和旋转。为了获得更好的可见性,省略了光纤阵列的盖盖。(b) 使用一对带有 3D 打印耦合元件的探头耦合到芯片波导:每个探头在六个自由度上对齐。为了获得更好的可见性,省略了光纤阵列的玻璃块。

对于集成InP波导的耦合实验,我们使用埋藏异质结构DFB激光器(Fraunhofer HHI),发射波长为1590 nm,在器件面测量MFD为3 μm [ 9]。作为参考,我们首先使用积分球测量了DFB激光器发射的功率与泵浦电流(P--曲线)的函数关系,积分球靠近激光面。在优化探头相对于激光面的位置后,再次通过3D打印的耦合元件测量P曲线。作为耦合损耗的参考点,我们选择50 mA的泵浦电流,为此指定了激光器。与积分球测量的功率相比,我们估计3D打印的耦合元件的损耗为1.9 dB。

为了耦合到1550 nm的SiP电路,我们依赖于在比利时大学间微电子中心(IMEC)的标准硅光子学平台上制造的测试芯片,其边缘耦合器的测量MFD为2.5 μm。我们探索了边缘耦合器之间间距为 250 μm、1250 μm 和 1750μm 的环回波导的耦合,其中光的耦合和耦合是通过公共光纤阵列上的不同耦合元件完成的,图 4(a),以及耦合到具有一对独立可移动探头的直通片波导,图 4(b)。对于每种配置,我们使用片上波导和 3D 打印耦合元件的不同组合进行一系列测量。在每次测量中,探头位置和方向都经过单独优化,以实现最大的透射率。片上波导的损耗为0.17 dB/mm,从测量的参考结构中提取出来,并在估算耦合损耗时加以考虑。对于芯片直通波导,我们发现每个接口的耦合损耗为(2.23±0.14)dB,从18次测量中提取。对于环回波导,测得的耦合损耗为(2.43 ± 0.35) dB,从17次测量中提取,边缘耦合器之间具有不同间距的波导。每个耦合接口的最小测量损耗为1.9 dB。请注意,环回结构的平均耦合损耗仅略高于片通波导的平均耦合损耗。这表明探针间距的不准确性或3D打印耦合元件的其他与制造相关的变化并没有起到重要作用。

我们进一步研究了探针间距不准确的影响,当探测具有小模场直径(D WG,SiP = 2.5 μm)的规则间隔SiP波导阵列时,这可能会成为一个突出的损伤。为此,我们使用一个SMF阵列,该阵列具有八个3D打印元件,同时耦合到四个片上环回波导。在第一步中,我们通过最大化通过由第一个和最后一个耦合元件以及最外层环回结构组成的参考通道的传输来优化 SMF 阵列的位置和方向,参见图 4(a) 中只有四个耦合元件的阵列探测实验的图示。然后,我们在x和z方向上转换SMF阵列,即横向到片上波导的光轴,并记录通过所有四个通道的传输,每个通道都包含一个片上环回波导以及相关的一对耦合元件。四个环回通道中每个通道的位置相关传输 𝜂LB�LB 均由具有可变位置、峰值耦合效率和 1/e 2 宽度的高斯拟合。然后,我们提取每个高斯最大值的 (x, z) 位置,对应于相应通道的最佳探针位置。我们发现,对于不同的通道,探针的最佳 z 位置非常相似,标准偏差仅 𝜎pr,𝑧≈0.08𝜇m�pr,�≈0.08�m 为 ,而最佳 x 位置表现出更强的变化,标准偏差为 𝜎pr,𝑥≈0.28𝜇m�pr,�≈0.28�m 。最佳耦合位置的这种变化可以转化为相关耦合元件的位置变化和波导面上产生的相关焦点。通常,输入端和输出端的耦合元件都会受到位置不精确的影响,这可以通过输入端和输出端 Δ𝑥o,Δ𝑧oΔ�o,Δ�o 耦合元件 Δ𝑥i,Δ𝑧iΔ�i,Δ�i 处的横向偏移来表示。对于光纤探头的“中间”横向偏移,通过整个通道实现了最佳传输,为此,输入和输出面处的耦合元件相对于最佳位置具有偏移。因此,探头的最佳横向偏移由两个耦合元件的横向偏移的平均值给出, Δ𝑥pr≈(Δ𝑥i+Δ𝑥o)/2Δ�pr≈(Δ�i+Δ�o)/2 并且 Δ𝑧pr≈(Δ𝑧i+Δ𝑧o)/2Δ�pr≈(Δ�i+Δ�o)/2 。假设 和 方差相同 Δ𝑥2i=Δ𝑥2o=𝜎2ce,𝑥Δ�i2¯=Δ�o2¯=�ce,�2 的高斯分布 Δ𝑥iΔ�i Δ𝑥oΔ�o ,其中 overbaroverbar¯ 表示期望值,我们可以用 Δ𝑥2pr=𝜎2pr,𝑥=𝜎2ce,𝑥/2Δ�pr2¯=�pr,�2=�ce,�2/2 表示水平方向上探针位置 Δ𝑥prΔ�pr 的方差。类似地,探头在 Δ𝑧prΔ�pr 垂直方向上的方差由下式 Δ𝑧2pr=𝜎2pr,𝑧=𝜎2ce,𝑧/2Δ�pr2¯=�pr,�2=�ce,�2/2 给出。因此,根据测量的标准偏差 𝜎pr,𝑥≈0.28𝜇m�pr,�≈0.28�m 和 𝜎pr,𝑧≈0.08𝜇m�pr,�≈0.08�m 最佳探头位置,我们可以估计耦合元件的焦点位置的方差为 𝜎ce,𝑥≈0.40𝜇m�ce,�≈0.40�m 和 𝜎ce,𝑧≈0.11𝜇m�ce,�≈0.11�m 。这符合预期,即激光光刻相当精确,导致焦点沿z的偏移很小,而沿x的耦合元件的定位精度受到光纤阵列不精确的节距的限制,制造商指定了±0.3μm的典型变化[19]。

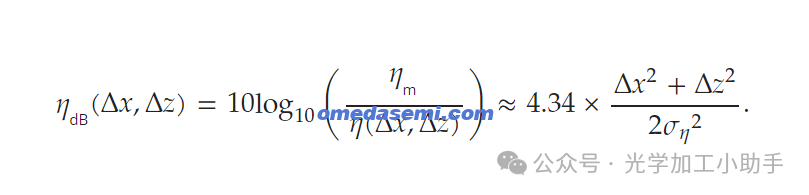

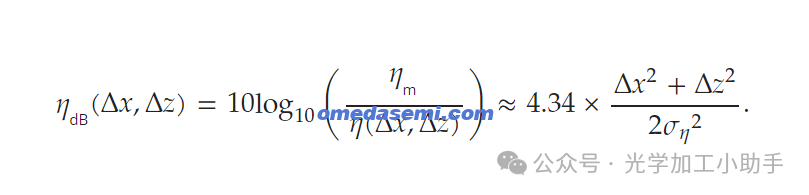

基于这些发现,我们现在可以估计与底层光纤探头的螺距不精确相关的过度耦合损耗。为此,我们首先考虑了图3(a)中单个耦合界面效率 𝜂� 对横向错位的模拟依赖性,并用高斯来描述这种关系。利用耦合元件的横向错位 Δ𝑥Δ� 和 Δ𝑧Δ� 耦合元件的焦点相对于片上波导轴线导致径向偏移 𝑟=Δ𝑥2+Δ𝑧2−−−−−−−−√�=Δ�2+Δ�2 的事实,并考虑到两个具有相同方差的相同高斯模场的耦合 (𝐷WG,SiP/2)2(�WG,SiP/2)2 导致耦合效率与方差的位置依赖性 𝜎2𝜂=2(𝐷WG,SiP/2)2=𝐷2WG,SiP/2��2=2(�WG,SiP/2)2=�WG,SiP2/2 ,这个高斯可以写成

(3)

𝜂(Δ𝑥,Δ𝑧)=𝜂mexp(−Δ𝑥2+Δ𝑧22𝜎𝜂2),�(Δ�,Δ�)=�mexp(−Δ�2+Δ�22��2),

where 𝜎𝜂=1.77𝜇m��=1.77�m is obtained for 𝐷WG,SiP=2.5𝜇m�WG,SiP=2.5�m. This relation may be translated into a dB-value for the coupling loss,

其中 𝜎𝜂=1.77𝜇m��=1.77�m 获取 𝐷WG,SiP=2.5𝜇m�WG,SiP=2.5�m 。这种关系可以转换为耦合损耗的dB值,

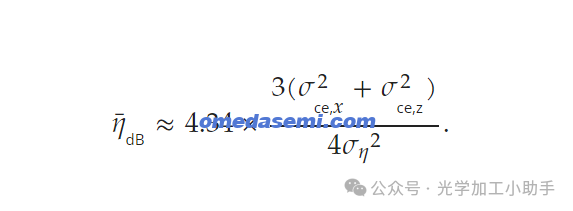

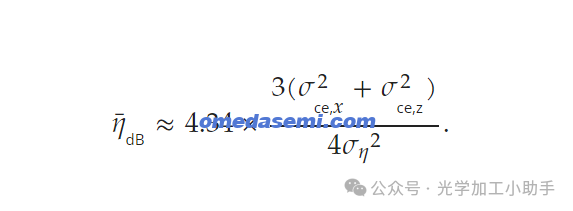

为了量化超额损耗 𝜂dB�dB ,我们接下来估计了在阵列探测场景中耦合元件相对于相应片上波导面的横向错位 Δ𝑥Δ� 和 Δ𝑧Δ� 焦点。为此,我们首先需要考虑这样一个事实,即光纤探头最初是基于参考通道的一对未准确定位的耦合元件对准的。在这个对准步骤中,当探头调整到由 Δ𝑥prΔ�pr 和 给出的“中间”位置时,再次达到最佳耦合效率,其中输入和 Δ𝑧prΔ�pr 输出面的两个耦合元件相对于最佳位置具有相同的偏移量。对于给定的 Δ𝑥2ce=𝜎2ce,𝑥Δ�ce2¯=�ce,�2 方差和 Δ𝑧2ce=𝜎2ce,𝑧Δ�ce2¯=�ce,�2 参考通道中耦合元件的焦点位置,探头位置的方差再次由 Δ𝑥2pr=𝜎2pr,𝑥=𝜎2ce,𝑥/2Δ�pr2¯=�pr,�2=�ce,�2/2 和 Δ𝑧2pr=𝜎2pr,𝑧=𝜎2ce,𝑧/2Δ�pr2¯=�pr,�2=�ce,�2/2 给出。除了定位不正确的探头外,目标耦合界面的效率还受到横向偏移 Δ𝑥ceΔ�ce 和 Δ𝑧ceΔ�ce 相关耦合元件的影响。因此,焦点相对于片上波导光轴的总横向偏移量为 Δ𝑥=Δ𝑥pr+Δ𝑥ceΔ�=Δ�pr+Δ�ce 和 Δ𝑧=Δ𝑧pr+Δ𝑧ceΔ�=Δ�pr+Δ�ce 。假设所有定位不准确在统计上都是独立的,则可以添加相关误差的方差, Δ𝑥2≈Δ𝑥2pr+Δ𝑥2ce=3𝜎2ce,𝑥/2Δ�2¯≈Δ�pr2¯+Δ�ce2¯=3�ce,�2/2 并且 Δ𝑧2≈Δ𝑧2pr+Δ𝑧2ce=3𝜎2ce,𝑧/2Δ�2¯≈Δ�pr2¯+Δ�ce2¯=3�ce,�2/2 。由式(4)可以看出,各种耦合元件的位置不精确所引起的超额损耗的期望值可以写成

(5)

𝜂¯dB≈4.34×3(𝜎2ce,𝑥+𝜎2ce,z)4𝜎𝜂2.�¯dB≈4.34×3(�ce,�2+�ce,z2)4��2.

插入值 𝜎ce,𝑥≈0.40𝜇m�ce,�≈0.40�m 、 𝜎ce,𝑧≈0.11𝜇m�ce,�≈0.11�m 和 𝜎𝜂=1.76𝜇m��=1.76�m ,我们发现由于 3D 打印耦合元件的对准不精确而导致的额外损耗约为 0.18 dB。请注意,该分析基于一个相当小的统计基础,在我们的实验中仅研究了八个耦合元件和四个传输通道。尽管如此,它仍然可以对3D打印耦合元件的间距不准确性的影响给出一个近似的定量指示,基于此,我们认为光纤间距的不准确性并不是一个根本的限制,即使对于探测具有小横截面的SiP波导阵列也是如此。

需要注意的是,上述SiP波导测得的1.9 dB耦合损耗与模拟损耗0.50 dB明显偏差。实验中发现的超额损失可归因于多种效应。首先,我们所有的测量都依赖于手动优化探头在六个自由度上的位置和方向。这些优化中的每一个都需要多次迭代,因为定位阶段的枢轴点与耦合元件的焦点不重合。我们预计,具有适当枢轴点校准的全自动主动对准程序可以进一步降低耦合损耗并提高可重复性,特别是对于波导阵列的耦合,如SiP环回波导所示。其次,我们对光耦合元件的仿真和优化依赖于理想高斯光束的假设,该光束仅近似地反映了真实的光束形状。此外,该模拟未考虑透镜-空气界面处 4% 的反射。第三,由于离散打印层导致的表面粗糙度会导致 TIR 反射镜和透镜表面的散射损耗。此外,制造工艺的缺陷可能会造成额外的损失:激光功率波动可能导致折射率或透镜表面位置偏离其目标值,不必要的收缩可能会进一步损害结构的几何形状。这两种效应都会影响发射光束的形状,从而影响测量的耦合效率。因此,虽然我们的概念验证实验证明了用于晶圆级探测的3D打印耦合元件的多功能性和性能,但我们希望通过优化耦合元件的设计、制造和定位,可以进一步提高耦合效率。请注意,由于透镜表面的强曲率,折射率差异引起的菲涅耳反射不一定会导致光过度反向反射到探测波导中——即使没有 AR 镀膜。因此,正确设计的3D打印耦合元件也可能适用于探测对杂散背反射敏感的器件,例如半导体光放大器(SOA)。

5. 总结

我们引入并实验演示了一种用于边缘耦合光子集成电路 (PIC) 的光学晶圆级探测的新方法。该概念依赖于紧凑的3D打印耦合元件,这些元件可以插入蚀刻在晶圆表面的标准切割沟中。利用双光子激光光刻的设计自由度和精度,耦合元件可以适应各种模场尺寸。在我们的实验中,我们展示了当耦合到氮化硅(TriPleX,D = 10 μm)片上波导、基于InP的有源光学元件(InP,D WG,TriPleX = 3 μm)和硅光子(SiP,D WG,InP WG,SiP = 2.5 μm)片上波导时,损耗分别低至2.7 dB、1.9 dB和1.9 dB。该技术非常适合通过单模光纤阵列对多个光端口进行并行探测,每个光纤阵列都配备了专用的耦合元件。我们相信,3D打印光学探针有可能彻底改变先进光子集成电路的晶圆级测试。