本文分享一篇老文章,2014年,但是作为一篇宏观的文章简要介绍了几种键合方式 ,Chip-wafer,Surface active bonding 在集成光子学中的应用,及其前景。同时十分有幸的是,小编提供 C2W和SAB键合代工

遇到的问题

硅光子异质集成最近引起了广泛关注。尽管人们集中精力将 III-V 族元素直接生长到硅上,但位错很难控制。

解决方案

晶圆键合为这个问题提供了理想的解决方案。直接晶圆键合工艺可将高质量化合物半导体薄膜转移到任何基板上。通过这种方式,可以堆叠不同的半导体层,使单个晶圆上具有不同的功能。光子集成电路或异质集成的先进键合技术通常可以为设备制造和生产成本带来巨大好处。特别是,晶圆熔融键合的等离子体活化可实现低温工艺,从而避免高键合温度并减少热应力或排气问题。

晶圆级芯片到晶圆键合(如 AC2W 工艺所示)是拥有成本模型的重大进步。与其他方法(如仅倒装芯片键合机或晶圆到晶圆键合)相比,它在高产量和高吞吐量下消耗的材料更少,因此最适合大批量芯片到晶圆生产。

我们常见的键合技术 有硅玻璃键合 金金键合,金锡键合,金硅键合,临时键合等等 。但是当我们遇到一些需要低温键合,或者一些特殊材料时,或者应用场景时,上述键合方式很难满足一些特殊场景的应用,

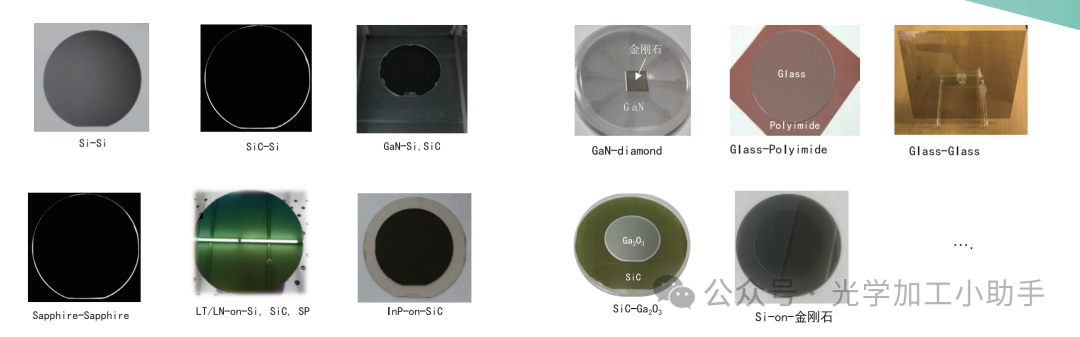

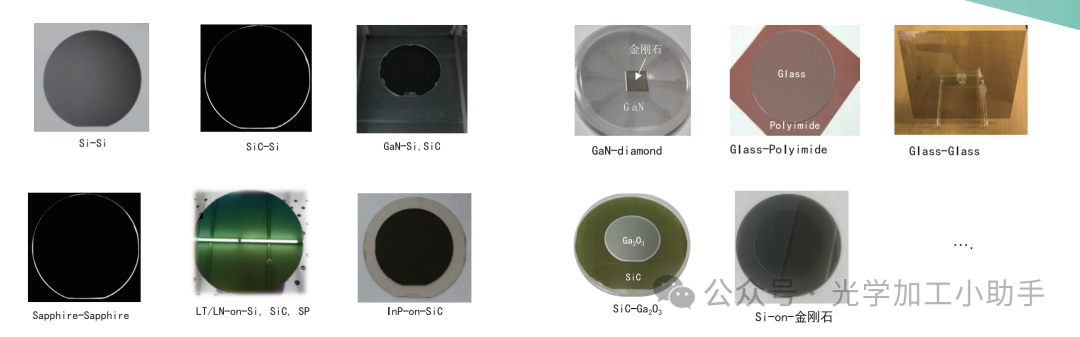

因此科学家提出了表面活化键合技术,这种技术 使键合技术所覆盖的材料范围更加广泛,比如

GaAs-SiC,InP-Diamond, LN-SiC,Si-Si,GaN-Dlamond,Sl-Diamond,蓝宝石-蓝宝石,金刚石-sic, sic-inp,sic-LN, ic-ga2o3,glass--glass,Si-SiC,Si-GaAs、GaAs- SiC、Si–SiC、SiC–SiC、Ge–Ge 、Al 2 O 3 -Al 2 O 3 ,GaP-InP, GaN-Si、LiNbO 3 -Al 2 O 3 、LiTaO 3 -Si and more(晶体,陶瓷,等等)

扩展的多材料的体系,将键合技术扩大了应用范围

*MEMS传感器 *光子集成电路 *半导体激光器

*功率器件 *3D封装 *异质集成

划重点--代工,代工,代工,卖设备

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜方式(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束直写等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

激光器芯片/探测器芯片/PIC芯片封装耦合服务"

请联系小编免费获取原文,也欢迎交流半导体行业,工艺,技术,市场发展

摘要

数据量的增加与摩尔定律大致相同,从而导致当今网络出现瓶颈。虽然在城域网和长途网络中光通信已经建立多年,但光学在短距离中变得越来越必不可少。为了实现机架到机架或最终芯片到芯片应用的光数据传输,硅光子学将成为核心技术。硅光子学可以结合成熟的硅技术的优势和 III-V 材料的卓越光学特性。为了实现这样的设备,硅上化合物半导体的异质集成是一个关键因素。虽然到目前为止,在硅上生长 III-V 族化合物的成功率有限,而且让有源区足够靠近硅波导也具有挑战性,但晶圆键合克服了这些挑战。

因此,晶圆键合是首选解决方案,因为它允许在 SOI 平台上集成无缺陷结构和最高性能。具有光学透明界面的晶圆键合是将 III-V 材料与硅连接起来的技术,即使在大批量生产中也能在单个芯片上实现光数据传输。

简介

当今的大多数应用都依赖于硅。然而,硅也有其局限性。特别是在光电子或高频应用方面,硅具有固有的材料限制。研究人员想出了很棒的新材料和设备组合。然而,主要的障碍仍然是如何以足够低的成本让每个人都能使用这项技术。在这里,硅技术再次发挥了重要作用,产量高,制造工艺得到极大优化。一种解决方案是通过材料工程在基板级别启用功能。这些所谓的工程基板通过新材料或不同材料的组合实现了新功能和异质集成,从而优化了设备性能。在一个芯片上融合不同的功能是工程基板的中心主题。

复合半导体的晶圆到晶圆或芯片到晶圆键合允许在低成本硅平台上实现高性能设备。这在电子、光电子、自旋电子学、生物传感和光伏等多种领域引起了广泛关注。

专注于基于 SOI 制造基础设施的光子集成电路 (PIC),III-V 材料(如磷化铟 (InP))的异质集成可以实现低成本和大批量的高性能设备。SOI 平台与 CMOS 技术兼容,因此具有高度准确性和成熟度,从而实现了稳健、高产量和可重复的技术,从而具有良好的性能。异质集成使该平台能够访问高速高效的 III/V 基光子元件 [1]。

通过这种方式,混合硅平台通过分子晶圆键合在 SOI 平台上异质集成了 III/V 功能。特别是,融合晶圆键合已被证明能够实现充分的键合,而不会降低 III-V 材料的光学性能,并实现与 SOI 波导的有效光学耦合。

熔融晶圆键合

直接晶圆键合是一种将两种具有不同结构特性的基板材料连接在一起的技术。此外,两个晶圆表面的等离子活化可用于改变两种材料的表面化学性质,从而降低键合温度。通过这种方式,可以将支持高晶体质量的复合半导体材料与考虑热膨胀差异的载体连接在一起。通过这种方式,可以在 III-V 激光二极管旁边安装基于 Si 的波导和调制器。

与在硅上直接生长 III-V 族元素相比,直接晶圆键合具有许多优势。在许多情况下,融合晶圆键合使用二氧化硅 (SiO2) 膜在两个晶圆上进行键合工艺。氧化膜可以是图案化的或覆盖式的。融合键合需要表面粗糙度小于 1nm 的平坦晶圆,这完全在当今 CMP 设备的能力范围内。SiO2 是一种已知的 CMOS 兼容材料,氧化物沉积和 CMP 几乎可以在所有晶圆上进行。由此产生的键合界面并不意味着对进一步的下游处理有任何限制,即进一步的处理步骤可以在高真空或高于键合温度的温度下进行。

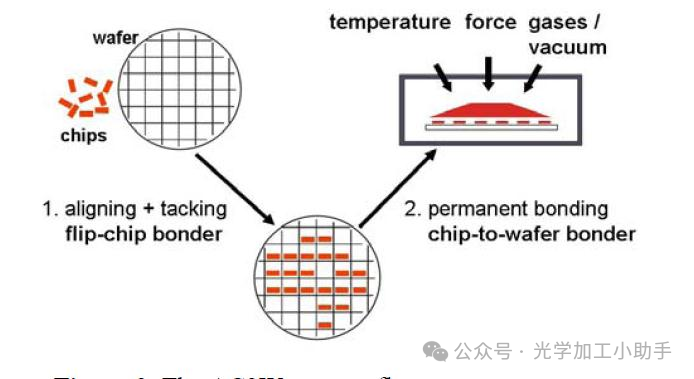

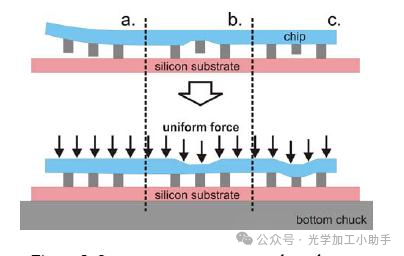

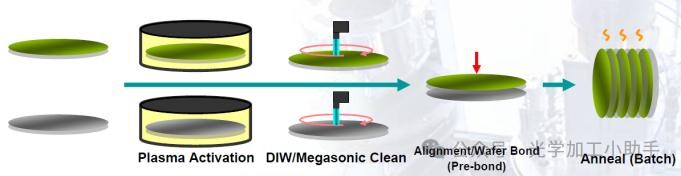

图 1:融合晶圆键合工艺流程

融合晶圆键合是一个两步工艺,包括室温预键合和退火步骤。为 SOI 晶圆制造开发的传统退火工艺要求退火温度为 1100°C。这些所需的热退火温度对于 CMOS 和 III-V 技术来说太高了,在这些技术中,主要的温度限制是由金属温度限制或相互扩散(400°C 或 450°C 的极短时间,在几分钟的范围内)造成的。晶圆表面等离子活化的发展是一项技术突破,使 CMOS 和 III-V 器件的融合键合得以广泛使用。

等离子活化

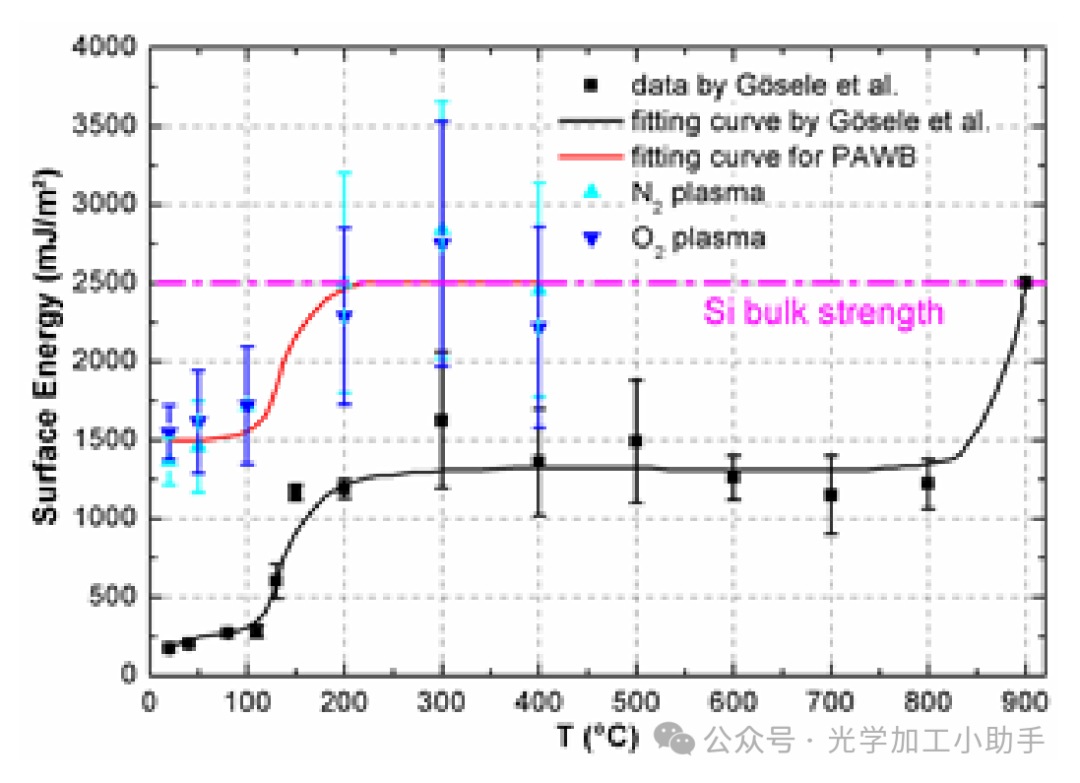

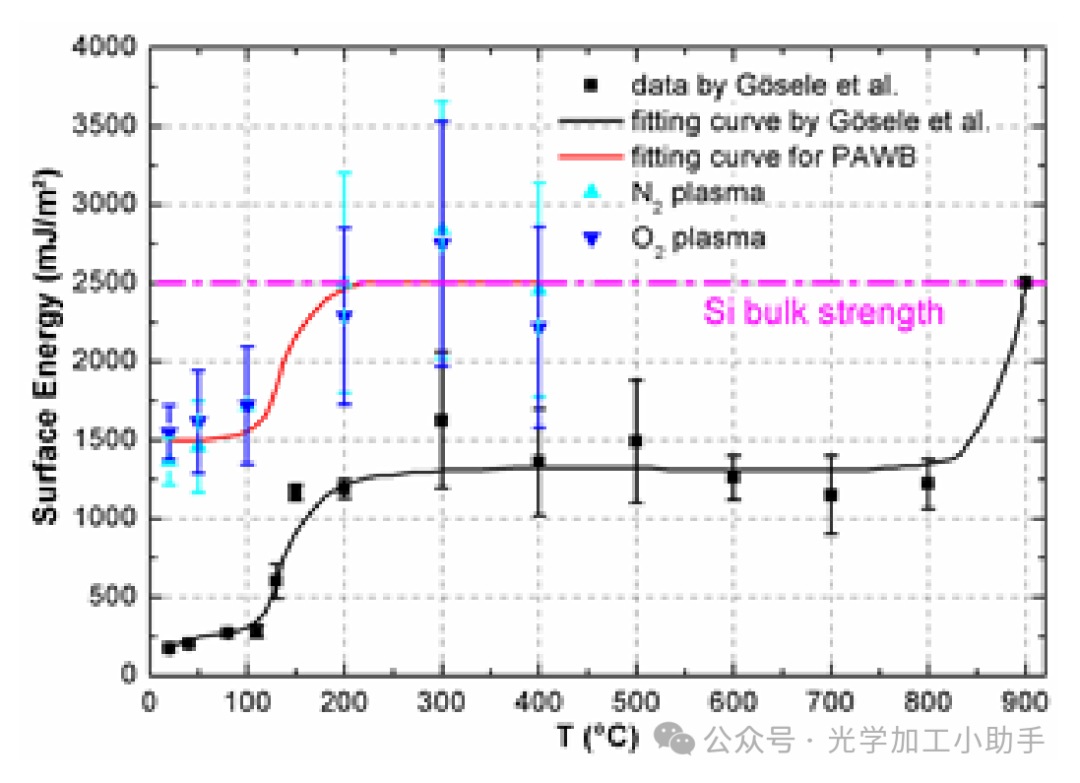

低温等离子活化直接晶圆键合是一种降低达到高键合强度所需的退火温度的工艺。这种改进的一个例子是一对天然氧化物 - 热氧化物晶片,通过在键合之前对晶片进行等离子激活,然后在 300°C 下进行短时间(0.5 - 1 小时)退火,可以实现体强度。图 2 显示了在熔融键合之前进行和未进行等离子激活的 Si/SiO2 晶片对的表面能(键合强度)特性与退火温度的关系。Plach 等人对此进行了更详细的说明。[2]

这使得熔融晶圆键合与完全处理的 CMOS 晶圆兼容。这种熔融键合工艺可轻松用于顶部预沉积 SiO2 层的化合物半导体。与其他键合技术相比,熔融晶圆键合具有多项优势,这使其特别适用于 PIC。预键合在室温下进行,因此晶圆不会发生热膨胀,并且 SiO2 界面与所需的光学元件兼容。预键合过程本身非常快,目前每个晶圆键合系统每小时可生产高达 15 个晶圆。预键合后,可以检查晶圆堆栈的键合缺陷和对准精度。如果任何参数超出规格,则只需将 2 个晶圆分离、清洁并再次键合即可。没有其他晶圆键合技术可以实现如此简单的返工程序。

最后,由于退火是批量处理的,因此熔融键合的总拥有成本 (TCO) 明显优于其他键合方法 [3]。

图 2:在不同温度下退火的键合 Si/SiO2 晶片对的表面能,用于高温氧化物键合和分别使用 N2 和 O2 等离子体的等离子激活晶片键合。虚线水平线表示最大键合强度 2.5J/m²。高温工艺的数据取自参考文献 [4]。

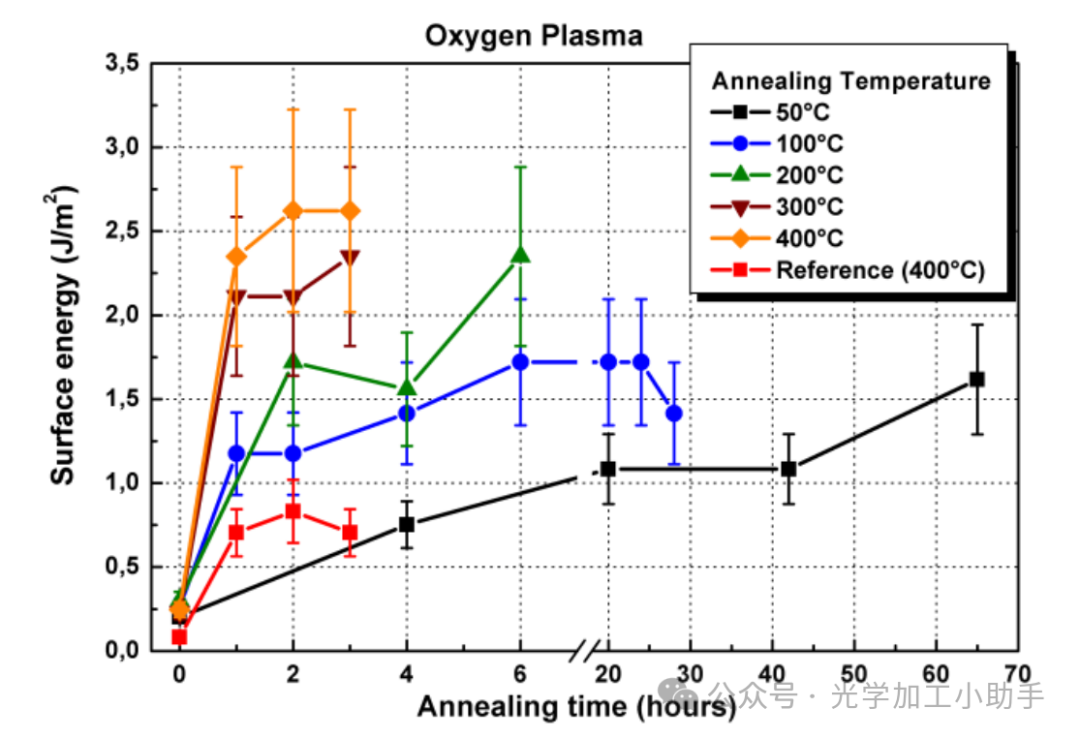

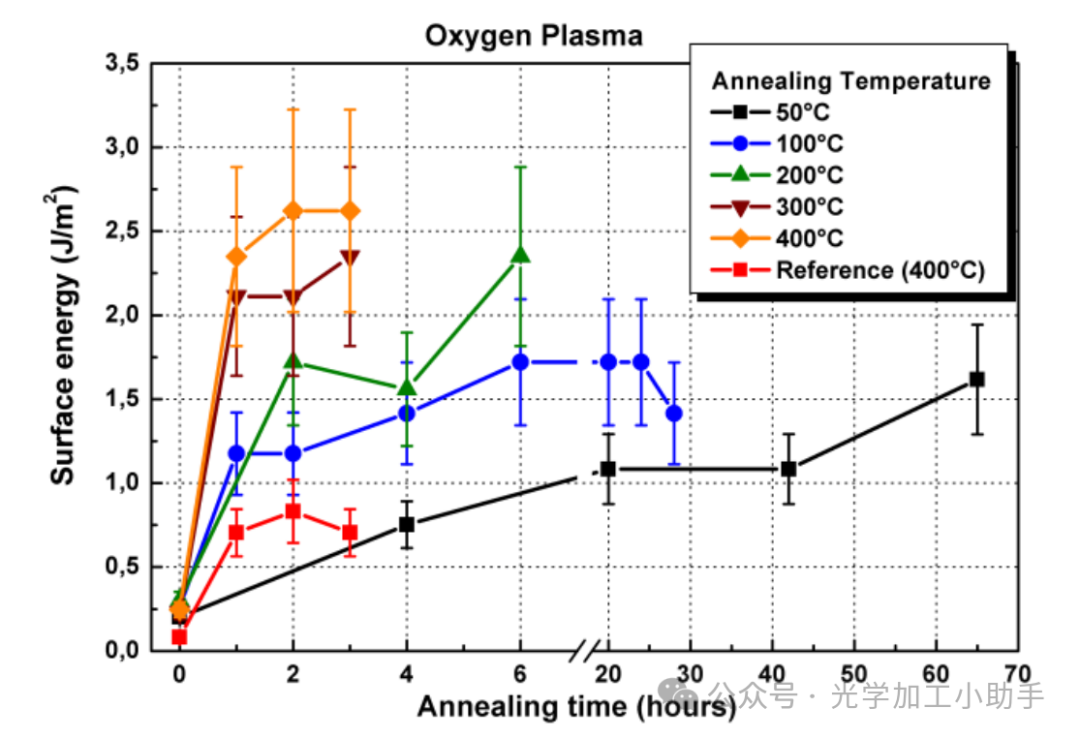

图 3 清楚地表明,通过氧等离子体激活可实现高表面能,因此具有良好的键合强度。针对不同的退火温度研究了该工艺的优化。此外,还表明可以通过延长退火时间来抵消较低的退火温度。因此,通过实施薄 SiO2 中间层,等离子体激活可以实现具有不同热膨胀系数的不同材料的异质集成,例如 Si 上的磷化铟 (InP) 或 Si 上的砷化镓 (GaAs)。

图 3:使用氧等离子体的 LowTemp™ 等离子体激活可在中等退火温度下实现高

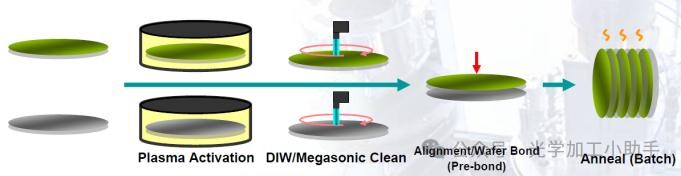

键合强度。由于许多 PIC 设计只需要在 SOI 晶圆的一小部分上进行异质集成,因此通过芯片到晶圆的方法可以显着降低成本。通过采用晶圆级方法应用先进的芯片到晶圆 (AC2W) 键合技术,甚至可以进一步降低成本。与晶圆到晶圆融合键合相比,对于芯片到晶圆异质集成,除了等离子体激活之外,还需要键合力和高温来获得足够的键合强度和高产量。

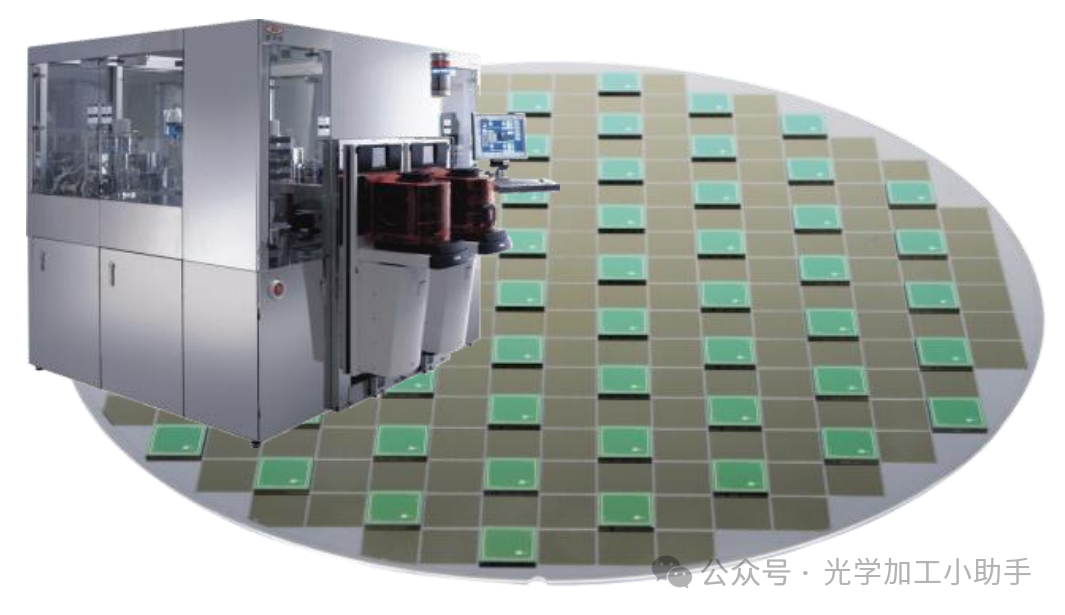

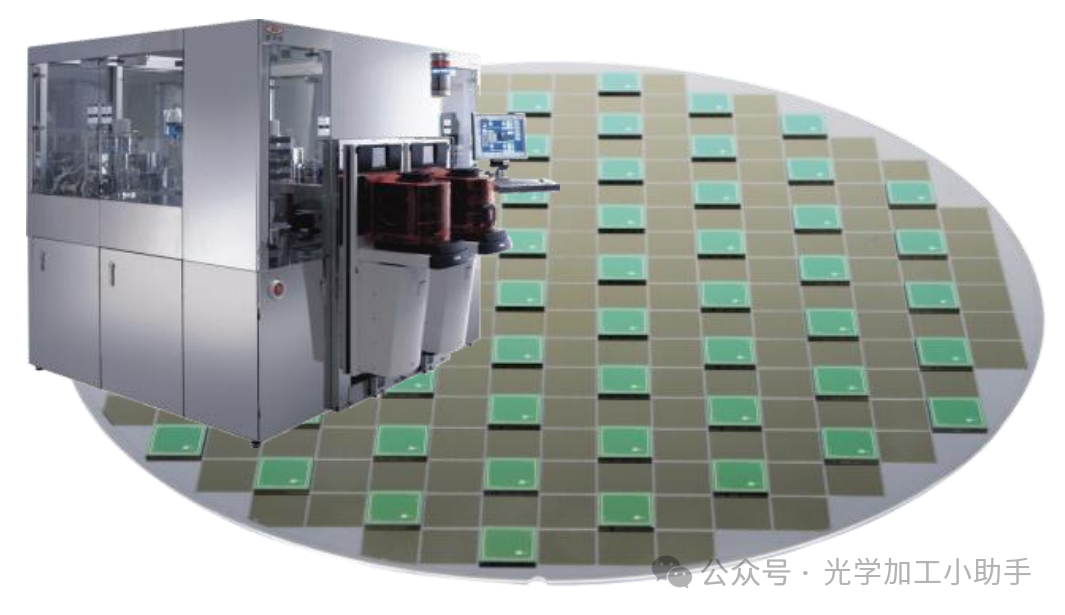

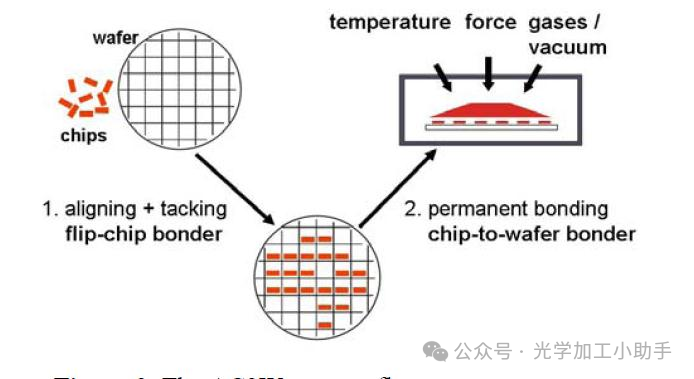

图 4:AC2W 工艺流程

AC2W 键合工艺是一种芯片到晶圆键合的工艺流程,专门设计用于施加力和温度,同时以适合批量生产的吞吐量形成键合。分离对准基板然后将基板彼此键合的概念是众所周知的,并广泛用于晶圆到晶圆键合。在 AC2W 键合工艺中,相同的概念适用于芯片到晶圆键合。

AC2W 工艺是一个两步工艺,如图 3 所示。首先,所有芯片对齐并固定在晶圆上,然后所有芯片同时并行永久键合到晶圆上 [5]。

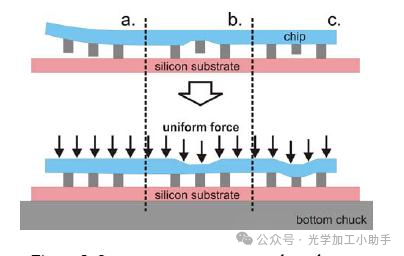

永久键合工艺需要在每个芯片上施加受控的均匀力。为了实现这一点,压板配备了一个柔性的柔顺层,当通过活塞和压板施加键合力时,它可以补偿顶部芯片之间的任何厚度变化。

如图 4 所示,柔顺层可以补偿由芯片或目标晶圆变化引起的可能的压力不均匀性。芯片的厚度变化是一个需要解决的重要问题,因为当芯片来自不同的源晶圆时,它们会定期发生。变化通常在微米或以下的范围内。使用柔顺层,可以显著减少由芯片到芯片或目标晶圆变化引起的产量问题。

图 5:如果不进行补偿,可能会出现未粘合区域,例如 a. 弯曲或翘曲,b. 基板不平整,c. 芯片高度变化(顶部)。这些问题可以通过使用柔顺层在芯片背面均匀施加力来克服

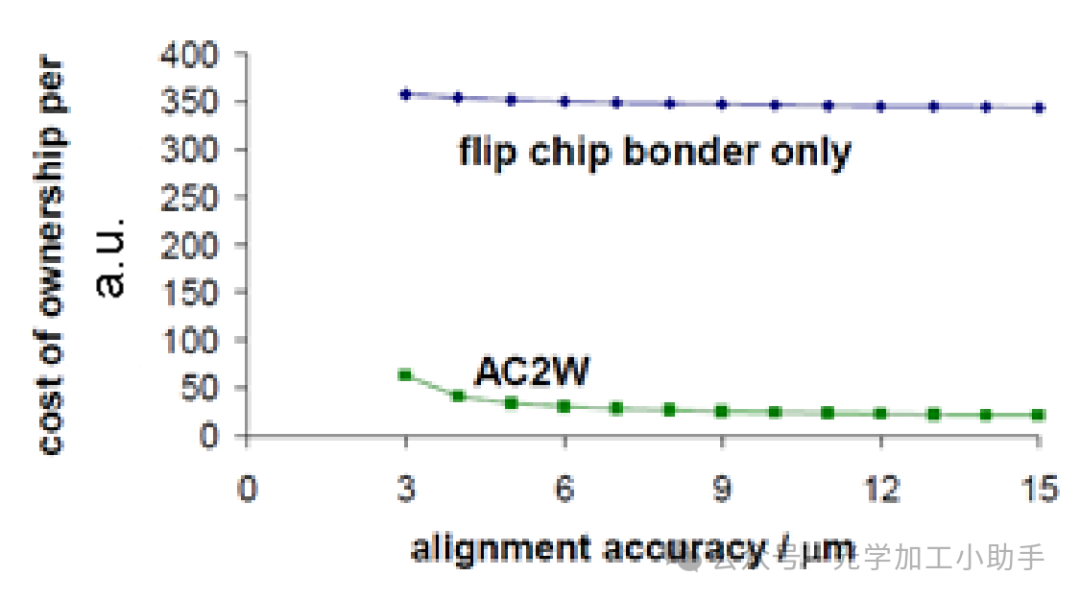

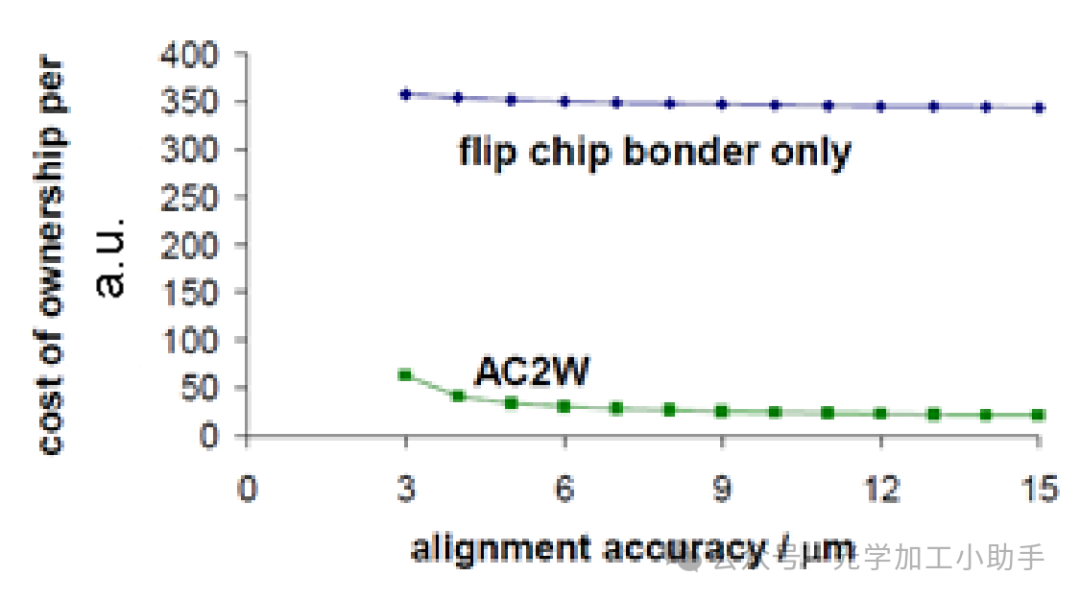

拥有成本

晶圆对晶圆 (W2W) 键合是一种广泛使用的工艺方法,用于连接和堆叠器件。W2W 键合的主要优势是可实现亚微米范围内的极高对准精度和高吞吐量。

在倒装芯片键合机中,吞吐量在很大程度上取决于目标对准精度。因此,当目标精度低于 2 微米时,AC2W 第一步的吞吐量会下降,而在 W2W 中,吞吐量几乎保持不变。在 AC2W 的第二步,W2W 键合的高吞吐量也得以实现,因为它与 W2W 键合非常相似,因为也有多个芯片同时键合到目标晶圆上。此外,工艺时间和工艺配方也完全相同。

图 5:仅使用倒装芯片键合机和 AC2W 键合工艺的拥有成本比较。

为了更好地理解,这里将给出一个例子。假设 2641 个尺寸为 5 x 5 mm² 的芯片键合到 300 毫米晶圆上。

假设键合的互连时间为 20 秒,而倒装芯片上的额外对准时间约为 0.5 秒。必须提到的是,对于异构集成,键合时间可能会长得多。这意味着在仅使用倒装芯片键合机的工艺中,每个单独的芯片需要 (20 秒 + 0.5 秒 =) 20.5 秒才能键合到晶圆上,从而产生每小时约 175 个芯片或每小时 0.066 个晶圆的吞吐量。

在 AC2W 工艺中,必须分别评估这两个步骤的吞吐量。在第一个 AC2W 步骤中,产量由倒装芯片接合器对准时间 (0.5 秒) 决定,因此每小时约 7200 个芯片或 2.73 个晶圆。除了产量之外,还有几个变量会影响 AC2W 工艺的拥有成本,例如芯片尺寸、晶圆尺寸、接合工艺和对准精度。对于给定的示例,计算了拥有成本 (CoO),如图 5 所示,它显示了一个数量级的成本优势。

图 6:200 毫米晶圆上的先进芯片到晶圆键合芯片。

总结

硅光子异质集成最近引起了广泛关注。尽管人们集中精力将 III-V 族元素直接生长到硅上,但位错很难控制。晶圆键合为这个问题提供了理想的解决方案。直接晶圆键合工艺可将高质量化合物半导体薄膜转移到任何基板上。通过这种方式,可以堆叠不同的半导体层,使单个晶圆上具有不同的功能。光子集成电路或异质集成的先进键合技术通常可以为设备制造和生产成本带来巨大好处。特别是,晶圆熔融键合的等离子体活化可实现低温工艺,从而避免高键合温度并减少热应力或排气问题。

晶圆级芯片到晶圆键合(如 AC2W 工艺所示)是拥有成本模型的重大进步。与其他方法(如仅倒装芯片键合机或晶圆到晶圆键合)相比,它在高产量和高吞吐量下消耗的材料更少,因此最适合大批量芯片到晶圆生产。