本文小编要分享的是用于碳化硅集成光子学的高品质碳化硅薄膜的制备和损耗测量。

前文我们介绍了碳化硅薄膜在集成光子学的优势和应用前景。

SIC+PIC--碳化硅集成光子学研究进展及其应用

而作为碳化硅材料光电平台的基础,高质量的碳化硅薄膜的制备,十分重要。

本文作者主要介绍了三种制备方案

直接外延生长的碳化硅薄膜(3c-sic)

通过键合sic和离子注入剥离获取碳化硅薄膜(4h-sic)

通过键合sic和多次抛光,退火,离子束抛光获取碳化硅薄膜(4h-sic)

最终可以看到,键合然后研磨抛光获取高质量薄膜的方式可以得到较高质量的薄膜

联系小编,获取pvd sic薄膜和 市场标准4寸半绝缘透明sic的折射率数据和透过率数据

a.薄膜快速表征服务,测粗糙度,折射率,吸收系数,透过率,四大光学指标,同时针对大家常用的光学材料,小编均已整理和测量了其折射率,需要折射率数据麻烦找小编获取。

b.🔥🔥6寸150nm微纳结构加工*🔥🔥

6寸 150nm线宽微纳结构(超结构,光栅,光波导,其他微纳结构)加工(光刻,镀膜,刻蚀,多材料(tio2,gan,inp,si3n4,gaas,hfo2,ta2o5,w,及其他更多材料))

一次出一个6寸晶圆高产出,低成本X万元,高效率2-3周,掩模版为一次投入,后续反复使用,一个晶圆可以设计多种结构验证,一次设计,多个方案同时验证。

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜方式(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束直写等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

激光器芯片/探测器芯片/PIC芯片封装耦合服务"芯片类型:激光器/探测器/PIC芯片(硅光,铌酸锂,氮化硅)"封装形式:TO封装/BOX封装/蝶形封装/COB封装/PIC芯片封装"应用市场:光通信/激光雷达/量子通信/陀螺仪/生物传感/量子计算等其他,独特优势:封装技术人员具有10+年的封装经验,具有成熟的封装研发及量产经验,参与过多款铌酸锂、硅光,窄线宽激光器等产品的量产同时能够提供热仿真,光学仿真等技术支持,提供全套的封装解决方案。同时基于我们在业内10+年的行业经验,对于供应链,原材料(热沉,透镜棱镜,光纤阵列,陶瓷管壳等)的选型,采购,使用,具有极其成熟的经验,可以有效地解决封装过程中遇到的各种问题,大大降低试错成本。

请联系小编免费获取原文,也欢迎交流半导体行业,工艺,技术,市场发展!

2 绝缘体上碳化硅薄膜制备及其光学损耗表征

碳化硅是一种丰富多晶型的宽禁带半导体。到目 前为止,已发现碳化硅存在超过 250 种晶型,其中 3C-、4H- 和 6H-碳化硅晶型因能够稳定生长而得到广泛使 用。早期碳化硅光子学的研究集中在同质外延的4H-碳化硅薄膜[30]或异质外延的 3C-碳化硅薄膜[31],在这 两种平台中,由于碳化硅外延层通常生长在高折射率 硅或者碳化硅材料上,光场的局域需要通过悬空工艺 使得碳化硅与衬底层隔离,从而使得制备的集成光子 器件可靠性和可集成性不足。解决这一问题的途径是发展类似 SOI 和 LNOI 的碳化硅薄膜光子学材料平 台,即在氧化硅层上制备碳化硅,形成绝缘体上碳化硅 (SiCOI)薄膜[32- 34]。由于氧化硅和碳化硅间存在较高 折射率差(约 1. 13),所以光场无需悬空工艺就可以被 很好地约束在碳化硅层内。

2. 1 硅基 3C-SiCOI 薄膜制备技术

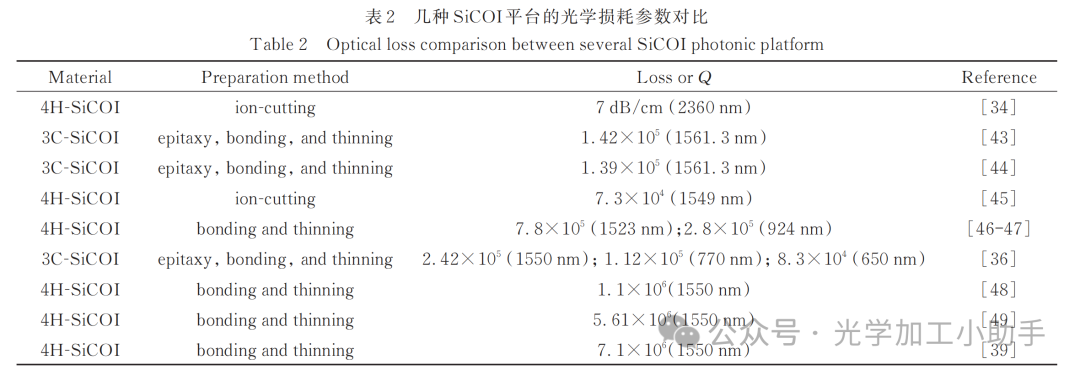

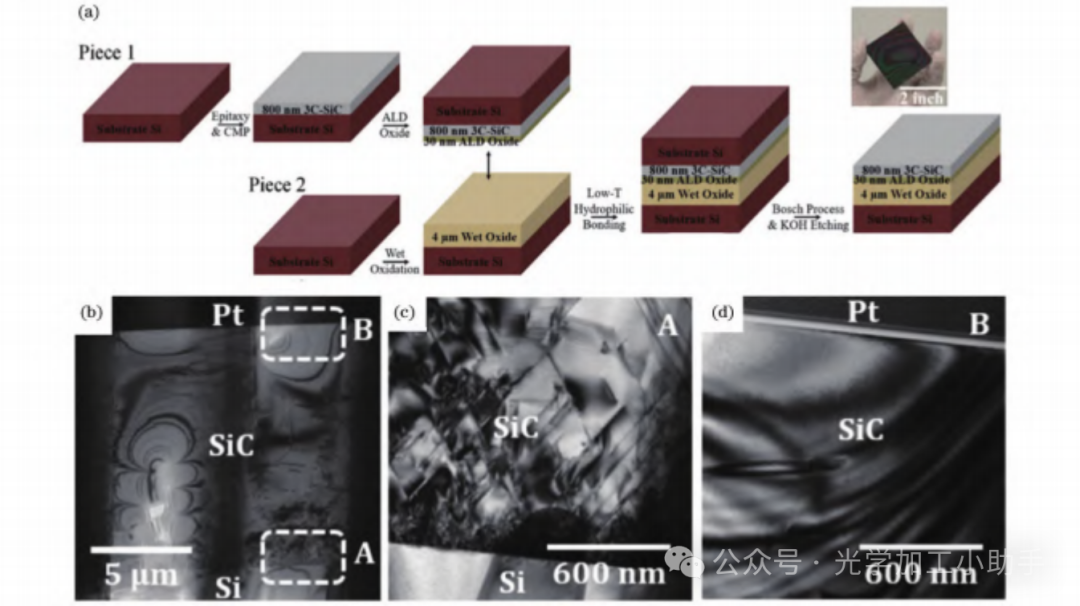

3C-碳化硅具有立方晶向,可以通过异质外延的方法直接在硅衬底上生长。然而 由于晶格常数失配,异 质外延生长的 3C-碳化硅薄膜中尤其在界面处存在大 量的晶格缺陷且无法形成绝缘体上薄膜的结构,因此具有较大的光学损耗。2018年,美国佐治亚理工大学 Fan 等[35]发展了一种结合异质外延、晶 圆键合和研磨 减薄的方法,将 3C-碳化硅薄膜制备在绝缘体衬底上,如图 1(a)所示 。整个制备过程始于在 Si基底上外延 生长出 3C-碳化硅层;然后利用化学机械抛光(CMP)工艺对其进行抛光和减薄,以获得所需厚度的 3C-碳 化硅薄膜;之后使用原子层沉积的方法在抛光的 3C- 碳化硅薄膜上沉积厚度为 30nm 的氧化硅层,以提供 具有较低粗糙度和更高结合强度的亲水性结合界面;此外,利用湿氧化法在另外一片硅晶圆上生长了 4μm 厚的氧化硅绝缘层,并利用低温(300℃)的亲水性晶

圆 键合工艺对 3C-碳化硅和氧化硅进行键合;最后将键合结构顶部的硅和一部分 3C-碳化硅通过机械研磨的 方式去除 。图 1(a)显示 了利用该方法制备 的一片 面积为 2cm×2cm 的 3C-SiCOI薄膜。为解决在外延初始阶段晶格失配大量产生的问题,该方法巧妙地利用键合将外延初始界面的薄膜翻转至上层,再利用研磨减薄将其去除 。图 1(b)和 图 1(c)为扫描 电子显微 镜(EM)和透射 电子显微镜(TEM)照片,展示了这种 方法对晶格缺陷的有效控制效果。该方法制备的微环谐振腔的最高 Q值为 2. 42×105,该值还远未达到碳化硅的本征损耗值,故其损耗的进一步降低仍需依赖于对制备方法中晶格缺陷的控制[30]。在该课题组后续的研究 中,发现将图 1(a)制备流程 中外延层厚度设置为5μm 以上即可得到极少外延缺陷的顶层碳化硅薄膜,但其光学损耗仍然有待验证。

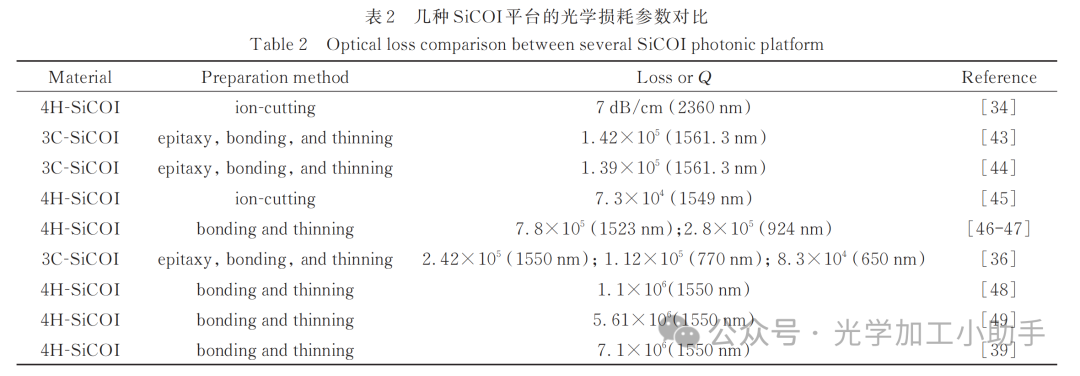

图 1 基于异质外延、晶圆键合和研磨减薄技术制备 3C-SiCOI[35- 36]。(a)制备流程;(b)3C-SiCOI各层的 SEM图;(c)SEM图中 A 区域的TEM图,在外延初始界面处显示有较多的晶格缺陷;(d)SEM图中B 区域的TEM图,在键合界面处显示晶格完好

2. 2 基 于 离 子 注入 剥 离 与转移 的 4H-SiCOI 薄膜 制 备技术

相 比 于 3C- 碳化硅,4H- 碳化硅具有更大 的折射率,并且 4H-碳化硅因更大的带隙而在功率 电子领域被广泛采用,目前其具有非常成熟的晶圆生长和加工基础 。然而需要注意的是,4H-碳化硅具有超高的生长温度(超过 1350 °C),故难以在硅基底上直接外延生长 4H-碳化硅薄膜。目前,一种可行的制备硅基底上的4H-碳化硅单 晶 薄膜 材料方法是借鉴 在SOI 和 LNOI制备中所采用的离子束剥离和衬底转移技术。

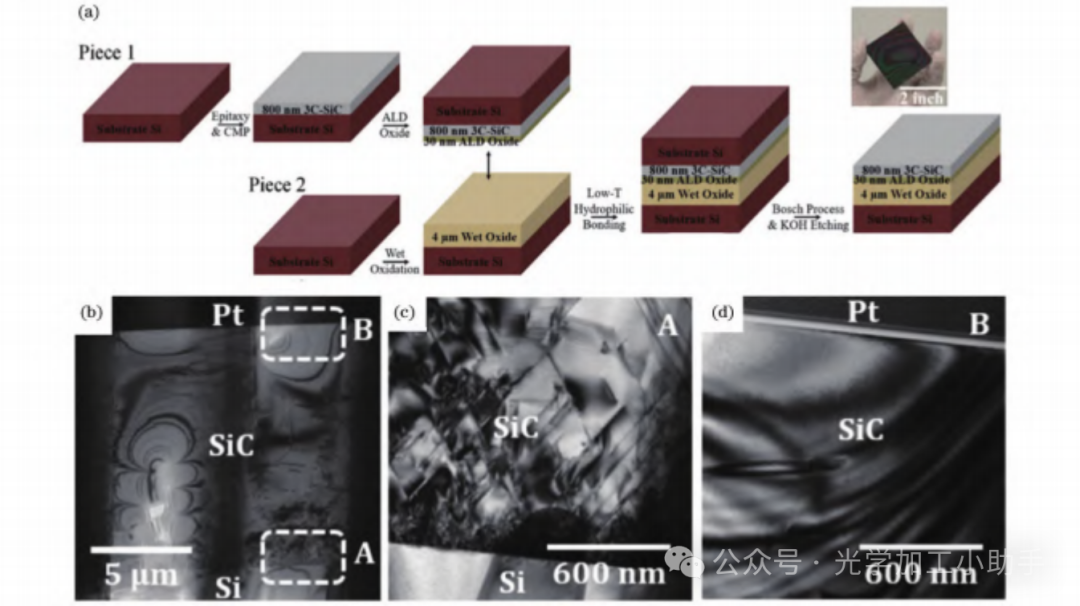

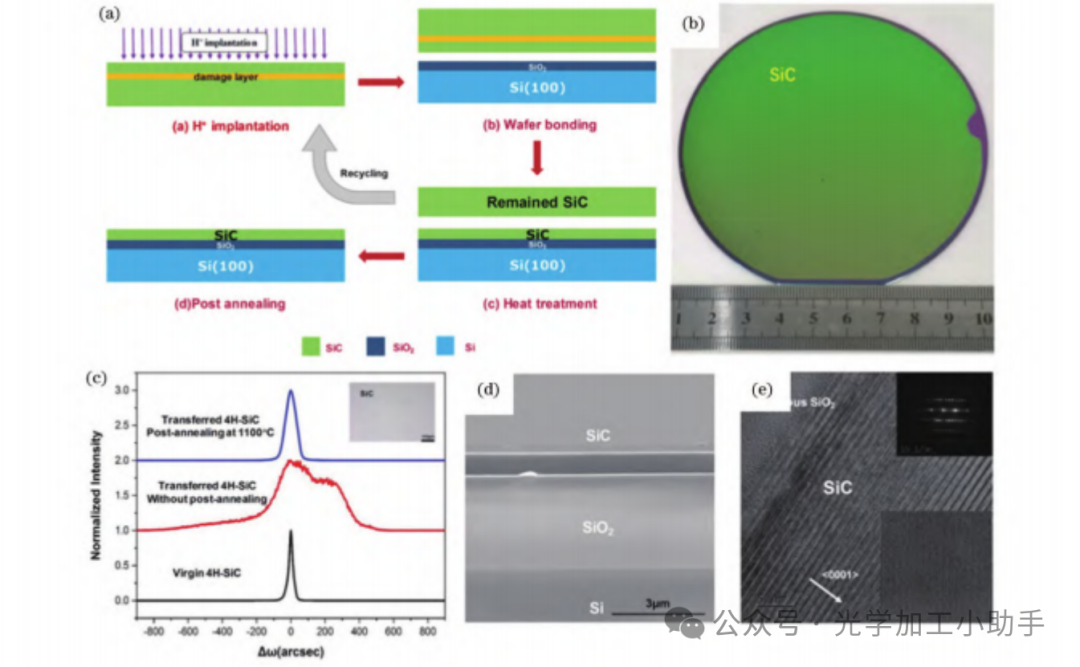

离子束剥离和衬底转移技术通常利用离子注入在 晶格中形成的剥离缺陷层进行薄膜的转移,该方法可以将薄膜转移在多种衬底上,同时制备的薄膜具有高均匀性和低成本,故其已经在硅光子学和铌酸锂光子学中取得了巨大的成功。上海微系统与信息技术研究所和美国哥伦比亚大学的研究团队分别报道过采用该方法制备 4H-SiCOI 薄膜的工作[32,34,37]。如图 2(a)所 示,采用离子束剥离和衬底转移技术制备 4H-SiCOI 薄膜的基本物理原理是:在单晶 4H-碳化硅上直接注入H/He等轻元素离子,从而在4H-碳化硅一定深度处埋入富含离子的气泡和孔洞,形成宏观的剥离缺陷层;之后再通过晶圆键合技术,将具有剥离缺陷层的 4H- 碳化硅转移到硅基衬底(通常为 SiO2-Si)上,并将 SiC- SiO2-Si键合晶圆在一定温度下退火,此时聚集离子的 膨胀作用将使表层 4H- 碳化硅 的薄膜转移到 SiO2-Si 衬底上,即形成 了完整 的 4H-SiCOI 结构 的制备 。由于经过离子注入的 4H-碳化硅薄膜存在一定的晶格损 伤,转移之后的薄膜还需要进行 1100℃后退火处理,这种处理一方面可以增强键合强度,另一方面可以恢复材料晶格质量。此外,后处理工艺需要对碳化硅薄膜进行进一步的减薄和抛光,采用的减薄技术可以为氧化工艺和干法刻蚀工艺。2020年,上海微系统与信 息技术研究所的研究组采用离子束剥离和衬底转移技术制备的 4H-SiCOI薄膜厚度偏差小于 0. 2%,表面粗糙 度小于 0. 5nm,转移面积可 以高于 95%,X 射线衍射(XRD)的半峰全宽为 75.6′′,如 图 2(c)和 图 2(d)所示。该方法所制备的 16. 5μm半径的碳化硅微环谐振器件的最高Q值为 7. 3×104。由于离子注入导致的本征材料吸收损耗难以被消除,基于离子注入剥离 4H- SiCOI材料的微环谐振器性能的进一步提升存在较大挑战。

图 2 基于离子注入剥离与转移技术制备 4H-SiCOI[37]。(a)制备流程;(b)所制备的 4H-SiCOI 的照片;(c)利用退火工艺对碳化硅层的晶格进行恢复的情况;(d)4H-SiCOI各层的SEM图;(e)4H-SiCOI的TEM图

2. 3 基于研磨减薄的 4H-SiCOI 薄膜制备技术

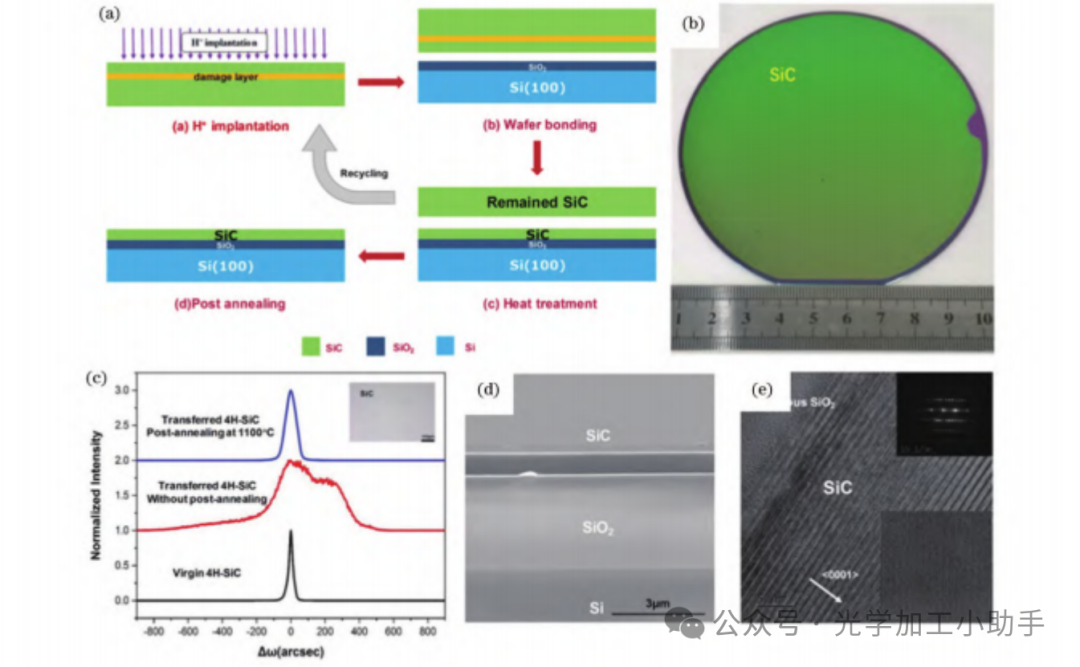

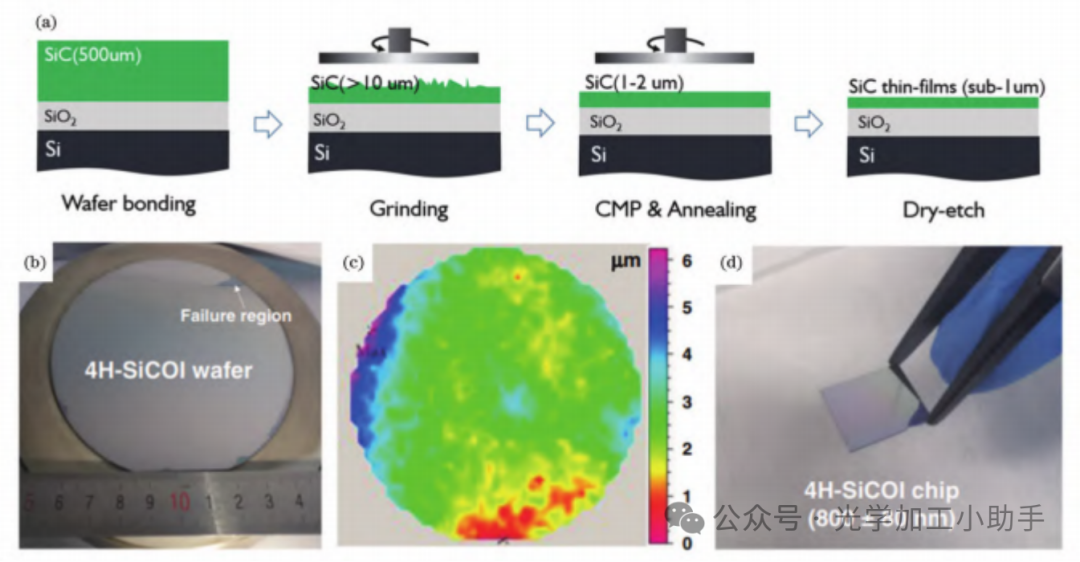

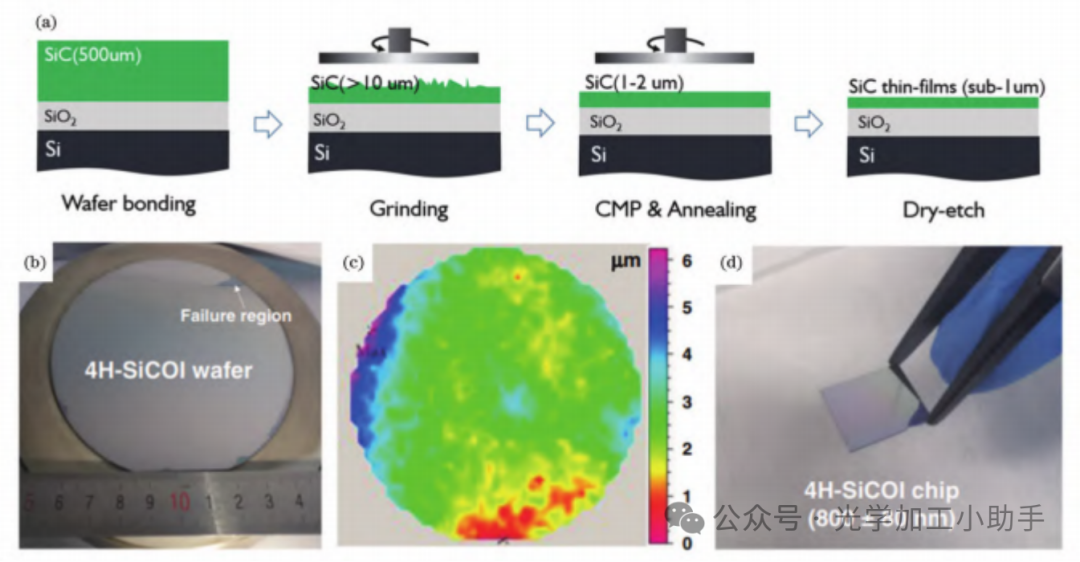

为了避免离子注入带来的光学损耗 ,一种采用直接键合体块碳化硅单晶后再进行机械研磨减薄碳化硅晶 圆的方法(后文简称为“研磨减薄”方法)被提出[38]。在半导体加工和封装领域,研磨减薄方法是获得晶体薄膜的常见工艺,如对硅晶圆的研磨减薄工艺已经发展为一种通用的工艺,在集成芯片封装等领域有着广泛的应用 。然而,4H-碳化硅具有仅次于金刚石的莫 氏硬度(4H-碳化硅为 9. 2,金刚石为10),如何对4H-碳化硅进行高效的减薄以及在减薄过程中保持厚度的均匀性和薄膜的完整性是研磨减薄工艺流程的两大挑战 。如 图 3(a)所示,研磨减薄制备 4H-SiCOI的流程始于在室温下直接键合 4H- 碳化硅 晶 圆和氧化硅衬 底。碳化硅晶圆初始厚度一般为 500μm,然后利用研 磨工艺将碳化硅晶圆厚度减薄至 10μm 以下。由于研磨工艺对表面会造成 1μm左右的划痕,并且有可能使晶圆发生解键合 ,因此需采用化学机械抛光工艺去除研磨的划痕,最终 4H-碳化硅层的精确厚度可以 由干法刻蚀工艺和碳化硅 的氧化工艺来确定 。图 3(b)为研磨减薄工艺制备 的 4H-SiCOI 单 晶薄膜,碳化硅薄膜厚度分布如 图 3(c)所示 。通过对各个步骤 的严格 控制,整个 4H-SiCOI 晶 圆大部分区域厚度不均匀性小 于1μm。图3(d)展示 的是1cm×1. 2cm大小 的4H-SiCOI衬底材料,实验测量 的平均厚度为(800±80)nm,该均匀性可满足大多数碳化硅集成光子学性能的实验室验证阶段的要求。对于需要更高均匀性的应用,如实现大量的光电器件晶圆级流片或者需求设计 的高重复性,则需要进一步采用离子束研磨(ionbeamtrimming)工艺。

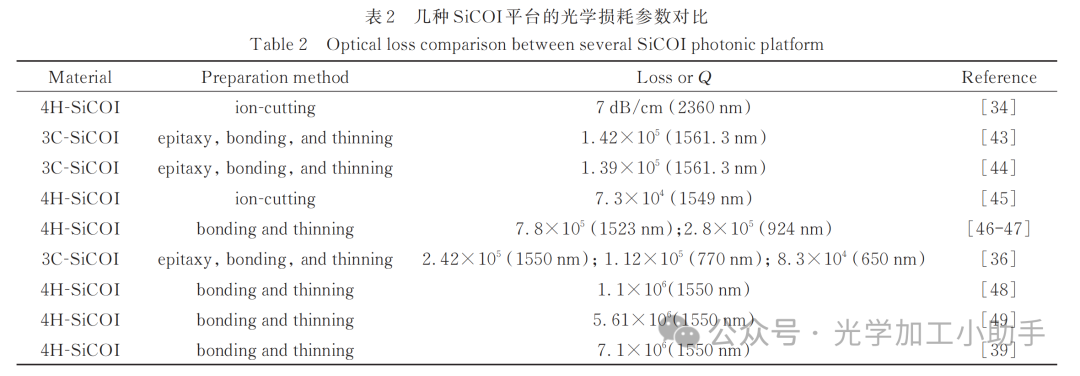

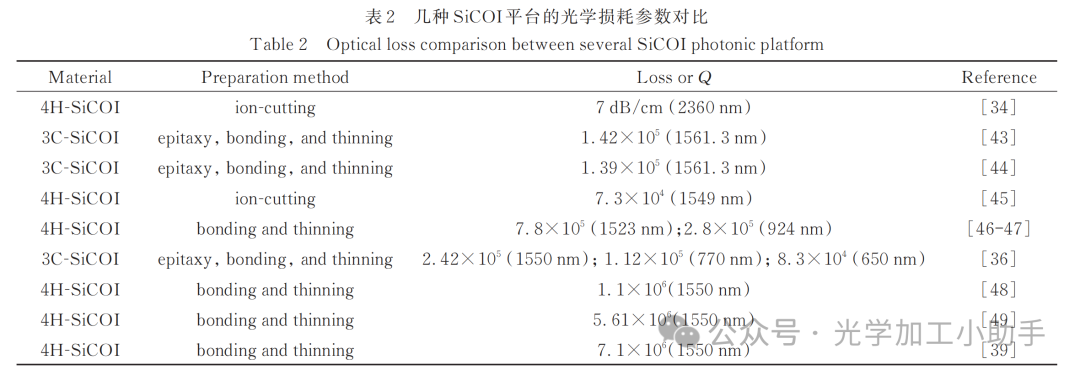

基 于研磨减薄制备的 4H-SiCOI薄膜保持了和利用升华法生长出的碳化硅体块单晶相同的晶体质量,而体块 4H-碳化硅单晶的本征吸收损耗在 1550 nm通信波段约为 0. 02dB/cm[40],所 以该方法制备 的 4H- SiCOI 薄膜具有极低的光学损耗。基于该方法,Song等[38]在 4H-SiCOI上验证了 Q 值高达 6. 3×105的光子晶体微腔。在此之后,上海微系统与信息技术研究所课题组[39]、美国卡耐基梅隆大学 Cai等[41]、斯坦福大学Lukin 等[42]在相似的薄膜制备技术路线上持续地将碳化硅光子学平台的光学损耗降低。2021 年,在研磨减薄 制备的 4H-SiCOI薄膜上验证的微盘谐振器最高 Q值可达 7.1×106,该数值更进一步地接近体块 4H-碳化硅单晶所对应的本征吸收损耗[39]。表 2列出了所介 的主要几种 SiCOI薄膜的光子器件的损耗对 比,可以看出,研磨减薄制备的 4H-SiCOI薄膜在制备极低损耗的光子器件方面具有显著的优越性。

图 3 基于研磨减薄技术制备 4H-SiCOI[39]。( a)制备流程;(b)所制备的 4H-SiCOI 的照片;( c)4H-SiCOI 薄膜均匀性表征;(d)所制备的面积为 10 mm×12 mm 的 4H-SiCOI 照片