文章名:“”Hypermultiplexed integrated photonics–based optical tensor processor“”

Shaoyuan Ou1, Kaiwen Xue1,2, Lian Zhou1,2, Chun-ho Lee1,2, Alexander Sludds3, Ryan Hamerly3,4,

Ke Zhang5, Hanke Feng5, Yue Yu1,2, Reshma Kopparapu1,2, Eric Zhong1, Cheng Wang5,

Dirk Englund3, Mengjie Yu1,2, Zaijun Chen1,2,6*

单位:

outhern California, Los Angeles, CA 90089, USA. 2Department of Electrical Engineering and Computer Science, University of California, Berkeley, CA 94720, USA. 3Research Laboratory of Electronics, MIT, Cambridge, MA 02139, USA. 4PHI Laboratories, NTT Research Inc., 940 Stewart Drive, Sunnyvale, CA 94085, USA. 5Department of Electrical Engineering & State Key Laboratory of Terahertz and Millimeter Waves, City University of Hong Kong, Kowloon, Hong Kong, China. 6Opticore Inc., Berkeley, CA 94705, USA

随着人工智能(AI)、物联网(IoT)和5G/6G移动网络的快速扩展,数据量和复杂性急剧增加,迫切需要高效、可扩展的计算硬件。在这里,我们展示了一种超多重复用张量光学处理器,它可以利用时空波长三维光学并行性每秒执行万亿次操作,使每个时钟周期实现O(N²)操作,并使用O(N)调制器设备。该系统由晶圆制造的III/V微米尺度激光器和高速薄膜铌酸锂电光器件组成,能够在每个符号上进行几十飞焦耳的编码。激光阈值结合了模拟直通整流器(ReLU)非线性,以实现低延迟的激活。系统的可扩展性通过包含40.5万个参数的机器学习模型得到了验证。高时钟速率、能效处理和可编程性相结合,释放了光在低能AI加速器中的潜力,适用于从大型AI模型训练到边缘部署中的实时决策等应用。

#6英寸蓝宝石晶圆,高品质,可以直接用于膜层生长和键合

#离子注入铒代工

#6寸DUV步进式光刻代工,最小线宽180nm,超高性价比,可以只曝光

#提供8寸 8umSiO2热氧片

ALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆;--超低损耗氮化硅薄膜晶圆,

SICOI晶圆;新型量子光学平台

6寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶圆

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

引言

张量处理器凭借其在数据密集型算法中的独特优势,已成为现代高性能计算(HPC)和人工智能(AI)中的重要计算模块,引领了深度学习(1)在语言处理(2)、图像分析(3)、自动化(4)、NP难优化(5)在调度、路线规划和资源分配方面的科学技术创新,以及迭代求解器(6)在多物理仿真(7)和加密货币(8)中的应用(图1A)。特别是,最近在大型语言模型(LLMs)(9)方面的成功,使得AI在我们的日常生活中得以应用,提升了工作效率和便利性(10)。通常,拥有多达万亿参数的大型语言模型(如2023年的GPT-4(11))是通过数万亿个输入符号(文本或代码)进行训练,每个符号与模型参数进行计算,从而对计算硬件、能耗和训练时间提出了严苛要求[训练时间长达几个月(11)]。计算能力的需求已经成为AI模型进一步发展和部署的根本瓶颈。

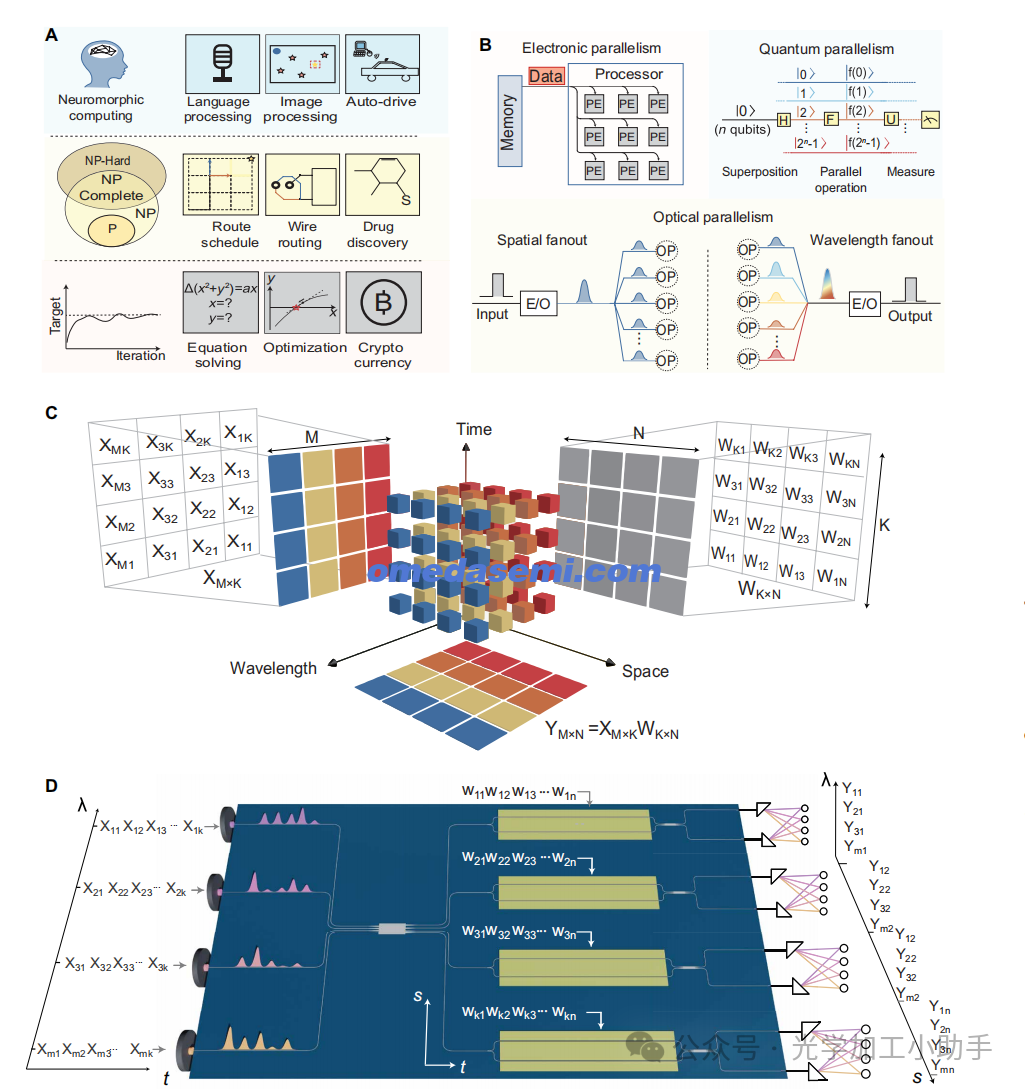

图1. HITOP的概念

(A) 用于神经形态计算、NP难问题求解器和迭代求解器的高性能计算(HPC)中的张量处理。

(B) 各种新兴计算平台的比较,使用数据并行性、量子并行性和光学并行性。PE,处理单元;H,Hadamard门;F,操作函数;U,单位算符;OP,操作。

(C) 基于空间、时间和波长三维数据编码的HITOP数据格式。输入矩阵 XM×KX_{M \times K}XM×K 在时间-波长维度中进行编码,数据在空间中分发;权重矩阵在时间-空间维度中进行编码,波长上分发。重叠元素的点积在时间轴上进行积分,将MMM结果按波长-空间维度排列。

(D) HITOP基于芯片的架构,显示了用于输入矩阵 XM×KX_{M \times K}XM×K 编码的4微米尺度激光波长通道和四个用于加权的空间TFLN调制器。

由于张量处理(12)中巨大的内存接口要求,传统的冯·诺依曼架构在执行这些任务时效率较低。新的计算范式(图1B)正在积极开发,利用各种类型的固有并行性。优化的主要指标包括(F1)计算能力——每秒的操作次数,(F2)能效——每次操作的能量消耗,(F3)计算密度——每秒每芯片区域的操作数,(F4)模型可扩展性——光学系统支持的参数数量,以及(F5)具有紧凑占地、低能耗和低延迟的非线性。

互补金属氧化物半导体(CMOS)电路,如图形处理单元(GPU)(13)、张量处理单元(TPU)(14)和应用特定集成电路(ASIC)(15),是当前高性能计算(HPC)的工作主力。CMOS处理器的高性能来自于小的特征尺寸和为内存通信量身定制的系统,例如,通过电子电缆将每个输入数据传递给N个处理单元(PEs)以提高数据带宽(图1B);然而,由于电缆电容(Ew ∝ CV²),能效和时钟速率与PE数量成反比,这已经成为CMOS电子的根本瓶颈(16)。量子并行性(17)是另一种有吸引力的平台,在计算速度上有指数级的加速,但这些系统非常依赖于某些问题,其实现和可扩展性一直是长期的障碍。

光学由于其光传播的超低损耗(例如,在我们的设备中为0.1 dB/cm)和大光学带宽,正在崭露头角,承诺能将计算指标提高几个数量级。最近的进展显示,使用Mach-Zehnder干涉仪网格(18-20)、相变材料(PCM)交叉条(21,22)或空间光调制器(23-25)进行矩阵-向量乘法(MVMs)具有光速计算(23,26,27)、自由空间数据处理(24,25,28,29)和片上集成(18-21,30,31)的潜力。然而,从架构层面来看,现有的基于波长或空间复用的技术需要(i)O(N²)的调制器设备,因为每个矩阵元素映射一个调制器,(ii)用于读取的高速模拟-数字转换器(ADC),这些都非常耗能,和(iii)高光学功率,用于在每个短的读取时间内积累光子电荷。最近,基于时间复用的方法显示出可扩展计算的潜力,例如大规模矩阵乘法(29)和水库计算(32)。然而,现有的基于光学干涉的演示(28,33)存在幅度-相位耦合和干涉波动的问题,限制了计算精度和可扩展性。从器件层面来看,数字存储器与高速、低电压、低损耗的光学发射器之间的接口是必要的,但由于现有技术(如基于微环的硅调制器)需要复杂的波长调谐和有限的光学带宽,而宽带调制器在带宽、损耗和Vπ等方面存在权衡限制,无法满足这些要求(34)。从架构到器件平台的创新是实现光学优势以进行高效可扩展计算的关键。

在此,我们提出并展示了一种超多重复用集成光子学的张量光学处理器(HITOP)。通过时间数据映射,HITOP通过空间光束路由和波长分复用(WDM)(图1C)建立神经连接性,促进了高密度的片上集成(图1D)。与最先进的光学计算系统相比,HITOP具有以下优势:(i)通过使用O(N)的调制器设备实现O(N²)的吞吐量,从而具备可扩展性;(ii)能效高的高速光子材料平台,配有紧凑可扩展的激光调制器和宽带薄膜铌酸锂(TFLN)光子学,用于电光(EO)转换(每次编码在几十飞焦耳范围内);(iii)基于时间数据映射的高模型可扩展性(每个设备每秒激活100亿个参数);(iv)时间积分接收器,允许低光功率和可扩展的读取电子学;(v)使用激光阈值进行延迟减少的在线光电子模拟非线性。所有这些优势对于可扩展、高效的AI计算至关重要,通过近50万个参数的模型进行基准测试,并具有260万亿次操作每秒(TOPS)/瓦的潜在全系统能效,这将比最先进的数字系统(如NVIDIA H100(35))提高超过100倍。

结果

HITOP架构

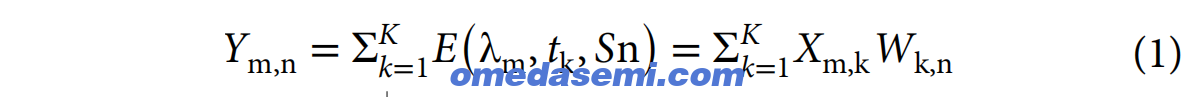

HITOP是一个混合光电子系统,用于执行通用张量处理 Y(M×N)=X(M×K)W(K×N)Y(M \times N) = X(M \times K)W(K \times N)Y(M×N)=X(M×K)W(K×N)(图1,C和D),其中M、K和N表示矩阵的尺寸(m、k和n是矩阵的索引)。在这里,输入矩阵 X(M×K)X(M \times K)X(M×K) 被映射到波长-时间基上,其中第m个向量(大小:1 x K)在第m个激光波长下进行幅度编码,具有K个时间步骤,E(λm,tk)=Xm,kE(\lambda_m, t_k) = X_{m,k}E(λm,tk)=Xm,k。这种波长-时间编码格式已在我们之前的工作中用于边缘计算(36)中的网络模型传输。在这里,针对片上张量处理,我们通过宽带多模干涉仪(MMIs)或波长分复用器将总共M个波长通道组合。组合后的光束通过片上光束路由分发到N个空间副本。在第Sn个通道,光束通过一个宽带光调制器,使用K个时间步骤对签名权重向量 WnW_nWn 进行编码,E(tk,Sn)=Wk,nE(t_k, S_n) = W_{k,n}E(tk,Sn)=Wk,n,并传输到所有M个波长。级联调制导致激光强度上的乘法 E(λm,tk,Sn)=Xm,kWk,nE(\lambda_m, t_k, S_n) = X_{m,k} W_{k,n}E(λm,tk,Sn)=Xm,kWk,n。

在接收端,每个Sn通道的光束在M个差分光电探测器上进行波长解复用,每个探测器减去两条光路的输出强度,用于操作正负权值(方法)。通过电荷积分放大器对结果的光电流在K个时间步骤内进行积累,最终得到

在第m个波长的第n个空间输出处, 这里,当数据 Wk,nW_{k,n}Wk,n 被编码到调制器时,乘法 Xm,kWk,nX_{m,k} W_{k,n}Xm,kWk,n 会在每个时钟周期发生,计算结果会转换为光电流,并在光电探测器上生成,随后通过电容器积累电荷以进行实时求和。每次乘加(MAC)操作在每个编码时钟周期内完成 [例如,R = 10吉符号(GS)/秒],并且以高速率进行,因此吞吐量随 T = 2 x M x N x R 线性扩展,其中 R 独立于积分时钟频率。

HITOP 的高可扩展性得益于系统的简洁性和低能耗。矩阵-矩阵乘法通常需要 O(N³) 的 MAC 操作,而 HITOP 使用 O(M) 的波长、O(N) 的调制器和 O(K) 的时间步骤进行计算,其中光学调制器的数量与 N + M 成线性关系。这样的简洁性得益于高度的并行性,其中每个输入激光波长被空间分配到所有调制器,以实现同时加权,每个权重编码通过宽带调制器应用于所有波长。与其他基于器件的计算方案类似,HITOP 每个时钟周期计算 O(N²) 的 MAC,但它仅在通过 K(≈1000)个时间步骤集成了 MAC 产品后进行读取,这大大减少了所需的光功率(方法),同时降低了高速读取电子学所需的电子功率。

HITOP器件平台

Here is the Chinese translation of the provided text:

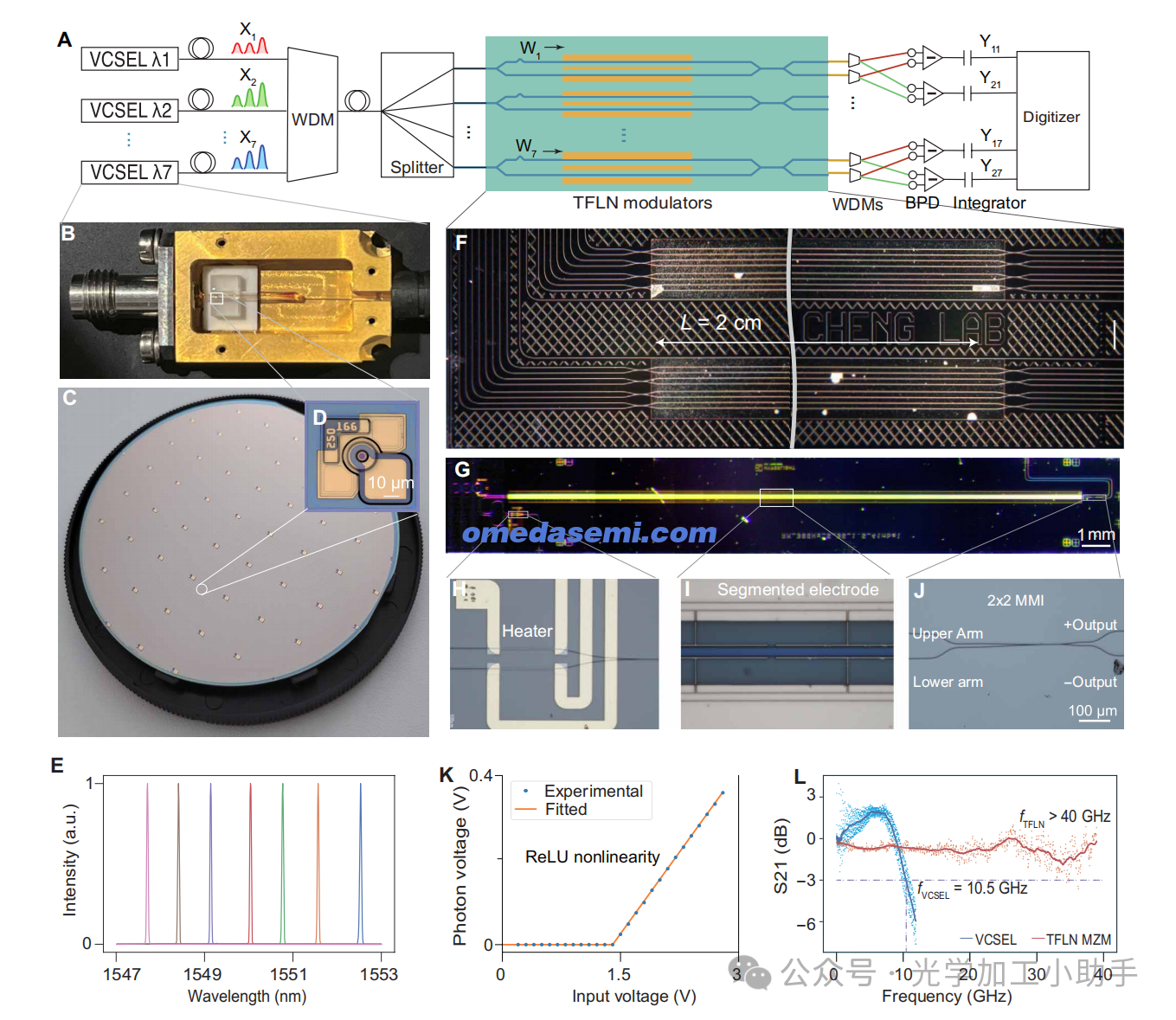

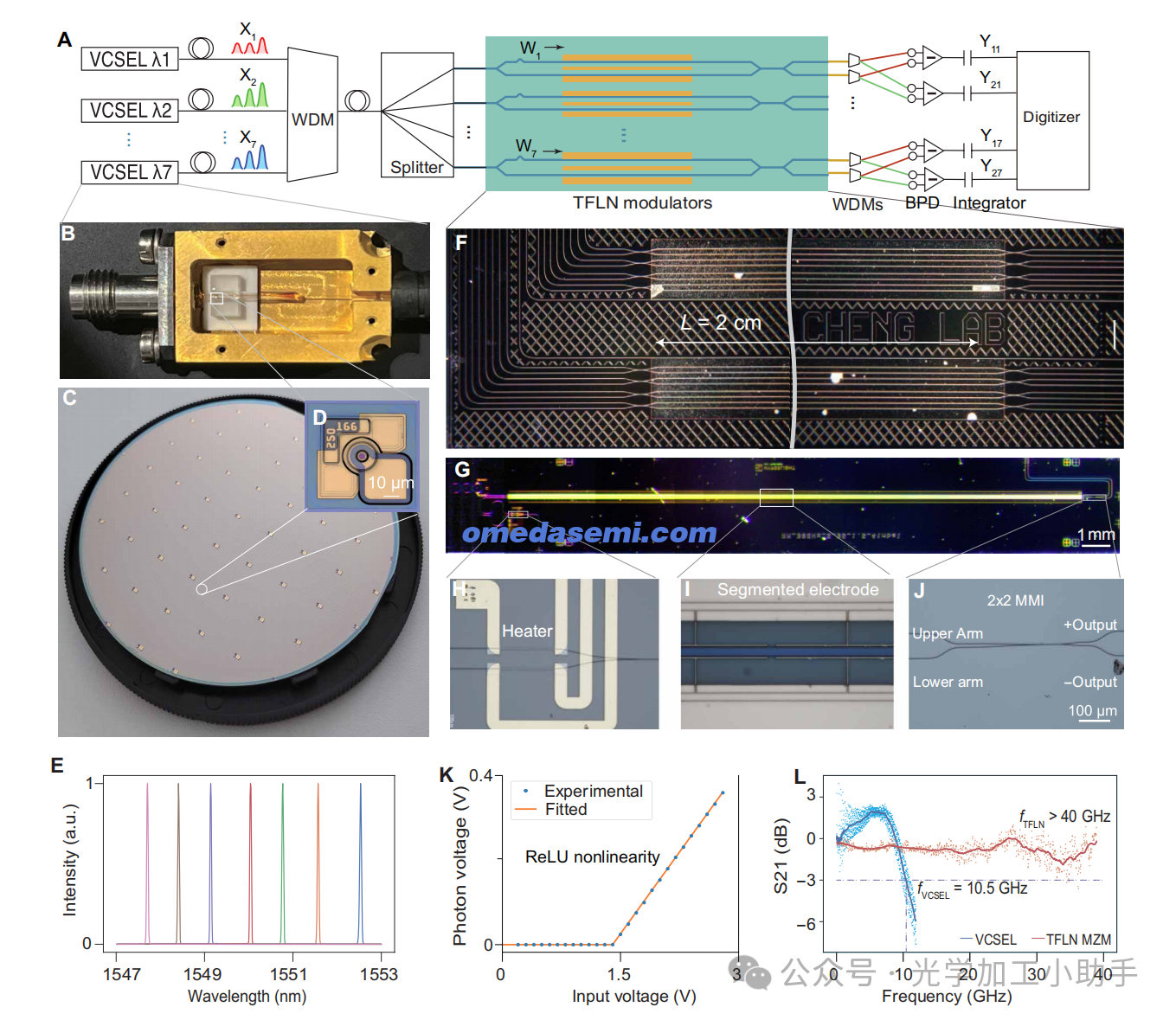

图2. HITOP实验设置和器件平台

(A) 实验设置。七个波长的VCSEL被组合在一个8通道基于光纤的WDM中,并通过一个8通道光纤功率分配器进行分配。每个副本通过TFLN调制器传输后在光纤WDM上解复用,并通过现成的平衡检测器进行检测。两个VCSEL和两个调制器同时驱动。

(B) 包装的VCSEL,带有电线键合和光纤耦合。

(C) 晶圆级制造的VCSEL。一个3英寸晶圆(VI系统,德国),上面有超过100,000个单模VCSEL发射器,每个VCSEL的3 dB带宽超过10.5 GHz。

(D) HITOP中使用的七个VCSEL波长的光谱,跨越5 nm(0.7 THz)。

(E) 制造的TFLN芯片的暗视图,包含八个双端口电光强度调制器(其中一个调制器不可用),每个调制器具有两个输入端口和两个输出端口。光束耦合到两个输入端口之一,两个输出光束进行相减以编码带符号的权重。a.u.,任意单位。

(F) 2厘米TFLN双输出电光强度调制器的示例。

(G) 用于设置操作偏置的加热器放大视图。

(H) 用于匹配微波折射率和光学折射率的分段电极(57)。

(I) 双端口输出。

(J) 用于神经网络层之间ReLU非线性激活的VCSEL阈值效应。数据通过带有TIA的光电探测器测量。对实验数据的线性拟合结果显示统计误差为0.26%。

(K 和 L) TFLN调制器的射频响应,3 dB带宽超过40 GHz,VCSEL的带宽为10.5 GHz。

我们探索了 III/V 半导体垂直腔面发射激光器(VCSEL)发射器(图2B)用于波长复用,原因在于其可扩展性、高传输速度(可见光中 >45 GHz(37),1550 nm 时 >10 GHz)和功率效率[壁插效率(WPE)可见光 VCSEL 为 >57%(38),本研究为20%]。与用于波长过滤和编码的 WDM 微环阵列(30)相比,VCSEL 既用于激光生成又用于数据传输,其中腔体共振和激光波长自然对齐,无需复杂的偏置控制和对环境噪声敏感的稳定化。我们的 VCSEL 在 VI Systems GmbH(德国柏林)制造,使用 InAlGaAs/InP 多层量子阱作为活性增益介质,发射波长约为1550 nm(39,40)。图2A 显示了由 100,000 个 VCSEL 组成的 300 毫米晶圆,晶圆的间距为 250 μm。每个 VCSEL 配有电子导线,连接到外部驱动器进行数据调制,输出与单模光纤耦合,用于 WDM 和边缘耦合到 TFLN 芯片。VCSEL 设计为在室温下发射在 1545、1550 和 1555 nm 附近的不同中心波长,具有 ±2 nm 的热调谐范围,覆盖 >10 nm 的整个光谱。七个 VCSEL 被调谐以匹配标准的电信 WDM 网格(图2D),总光学带宽为 6 nm(0.7 THz),范围从 1547 到 1553 nm。激光阈值电压为 1.2 V,每个 VCSEL 的光功率超过 1 mW,WPE 为 20%。每个 VCSEL 的 3 dB 信号调制带宽超过 10 GHz(图2K)。我们通过编码一个具有正态分布数据的向量验证了 VCSEL 数据调制的准确性。记录的响应与其真实值进行了比较,显示在 100百万符号(MS)/秒下编码误差小于 0.3%,相当于 8~9 位精度(图S4)。由于阻抗不匹配,精度在 10 GS/s 时降至 6 位,这可以通过定制的驱动电路设计解决。

我们开发了一个 TFLN 调制器平台(图2E),用于加权流和时间方向上的点积,同时支持宽波长范围。TFLN 光子学作为光学发射器的实用解决方案,克服了硅光子学中的当前限制,并结合了出色的 Pockels 性质和下一代集成光电子电路中的可扩展制造能力(41)。与大体积 EO 调制器相比,基于 EO 的 Pockels 调制器具有更低的开关电压和光学损耗(我们制造的 TFLN 调制器达到 0.1 dB/cm),更高的消光比和 EO 带宽,以及更好的线性度,这些对 HITOP 器件至关重要,有助于降低能耗,提高吞吐量和精度(34)。此外,薄膜平台可以通过微波电极设计来支持超宽光学带宽(>500 nm,模拟和实验证明见图S11到S13),得益于紧凑的波导、精确的纳米光刻和与大体积 EO 调制器相比更紧凑的器件尺寸。我们的 TFLN 调制器采用行波导设计,通过光学和微波折射率匹配提供 >40 GHz 的电光带宽,Vπ = 1.3 V(2 厘米长度)。这些调制器略微不平衡,具有 >150 nm 的自由光谱范围,适合通过波长调谐进行偏置(图S3)。我们观察到偏置在数据采集过程中稳定,且长期的偏移可以通过使用 TFLN 中的光致反射效应或热电效应进行可编程修整来补偿(42)。

一个实现并行处理的关键要求是设计双端口 TFLN 调制器,并配合差分检测以操作正负权重值(方法),这是 AI 计算中至关重要的。 由于用光强编码符号值并不直接可行,现有的解决方案(23、25、43)通常需要分别在两个时间步骤计算正负值,这导致计算开销(在速度、复杂性和延迟上),且无法同时处理多个向量(方法)。在 HITOP 中,每个 TFLN 调制器都以正交偏置工作,两个输出臂上具有相等的功率,通过差分检测抵消(对应于零值)。数据调制通过将光功率从一个臂转移到另一个臂,生成与编码电压成比例的正/负光子电流。我们输入的权重数据峰峰电压为 0.6 V,对应约 90 飞焦耳每符号(方法),并且低电压操作保持调制器在准线性区域,在该区域我们达到了 <0.4% 的数据编码误差,对应于 8 位精度(图 S4)。

HITOP 基准测试

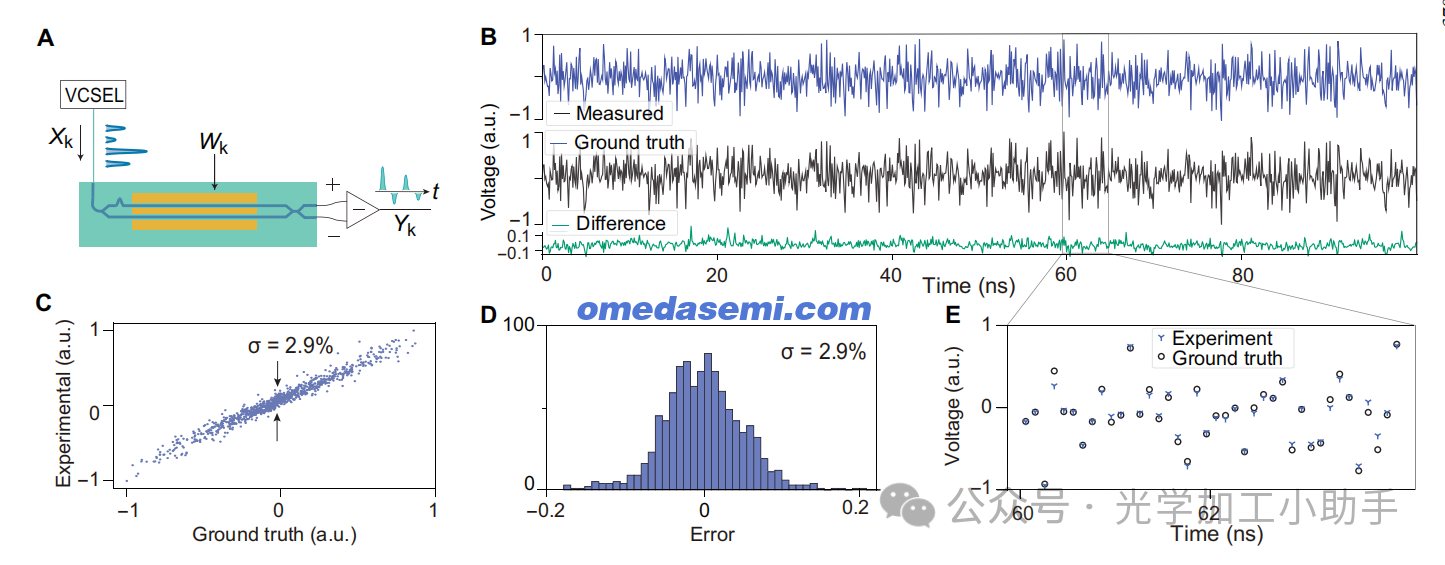

图3. 在10 GS/s下HITOP计算精度的实验验证

(A) 向量计算单元,由VCSEL和调制器组成,用于级联调制。

(B) 随机数乘法的实验结果与真实值的比较。

(C) 实验结果与真实值的相关性,显示在10 GS/s下计算误差为2.9%。

(D) 误差分布的直方图。

(E) 实验与真实值比较的放大视图。

我们构建了一个计算系统,包含七个 WDM VCSEL 和七个宽带 TFLN 调制器,这些调制器被集成在一个制造的 TFLN 芯片上(方法)。HITOP 的计算精度通过向 VCSEL 和 TFLN 调制器发送两组数据(每组包含 1000 个正态分布的随机值)来验证(图 3A)。需要注意的是,为了在 10 GS/s 时实现 6 位操作,X 和 W 同步脉冲列之间的延迟应控制在 τ = 100 ps/26 = 1.56 ps 内,这通过在差分探测器前匹配电子驱动器延迟线和光学延迟线实现。由于我们的发射器具有高线性度,通过级联调制进行带符号权重的幅度乘法能够在不需要任何校准的情况下实现良好的一致性。测量值和真实值之间的误差在 10 GS/s 时显示标准差为 2.9%(图 3B 到 3D),在 100 MS/s 时为 1.5%(图 S8),对应于 56 位的计算精度。我们将 10 GS/s 时的 1 位精度下降归因于电子失真和测量电路中的定时不匹配。这个实现的精度对于大多数 AI 应用来说已经足够(44)。需要注意的是,在器件层面,最近的级联 TFLN 调制器在 60 GS/s 时达到了 56 位的精度(参考文献 45)。

HITOP计算精度、可编程性和可扩展性

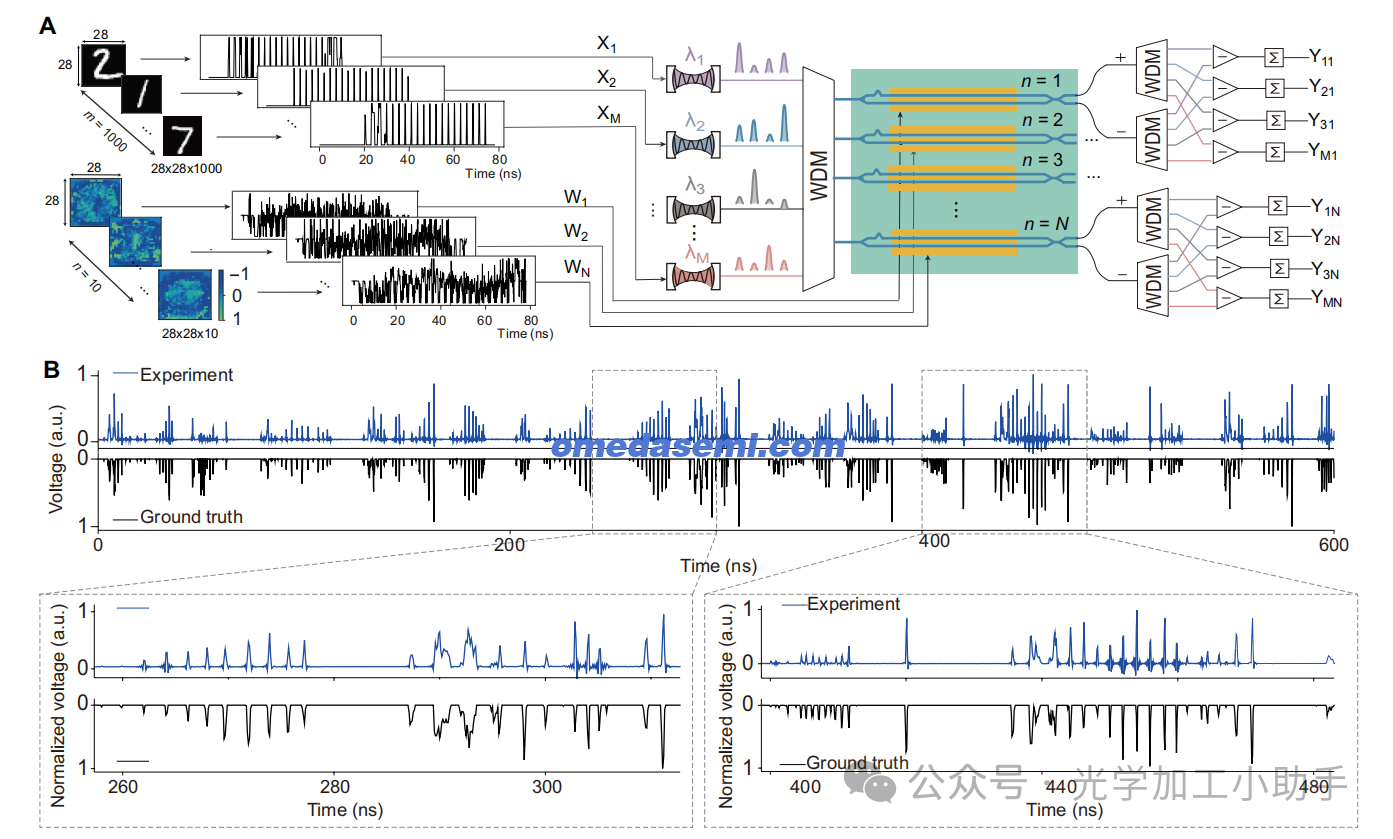

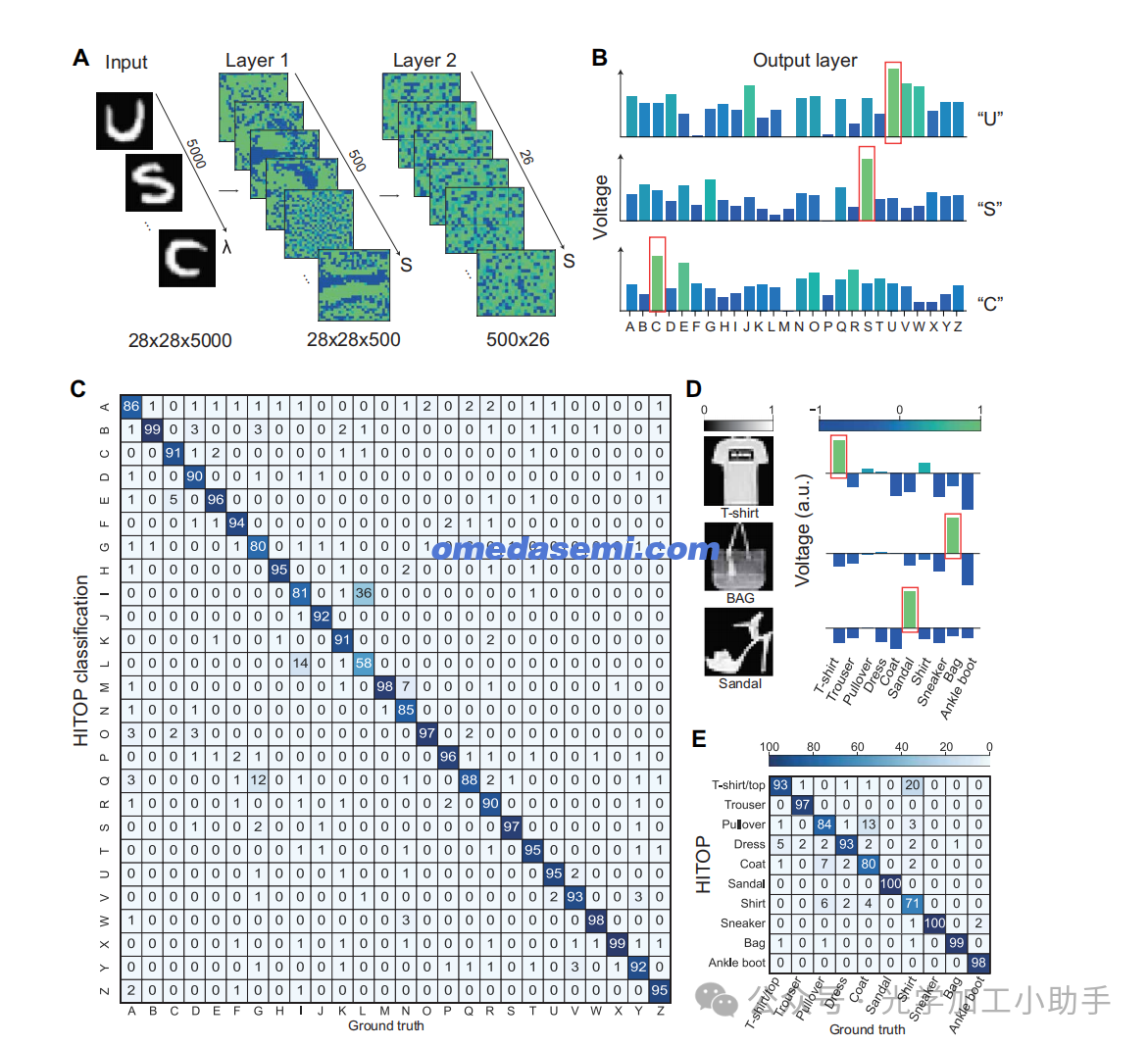

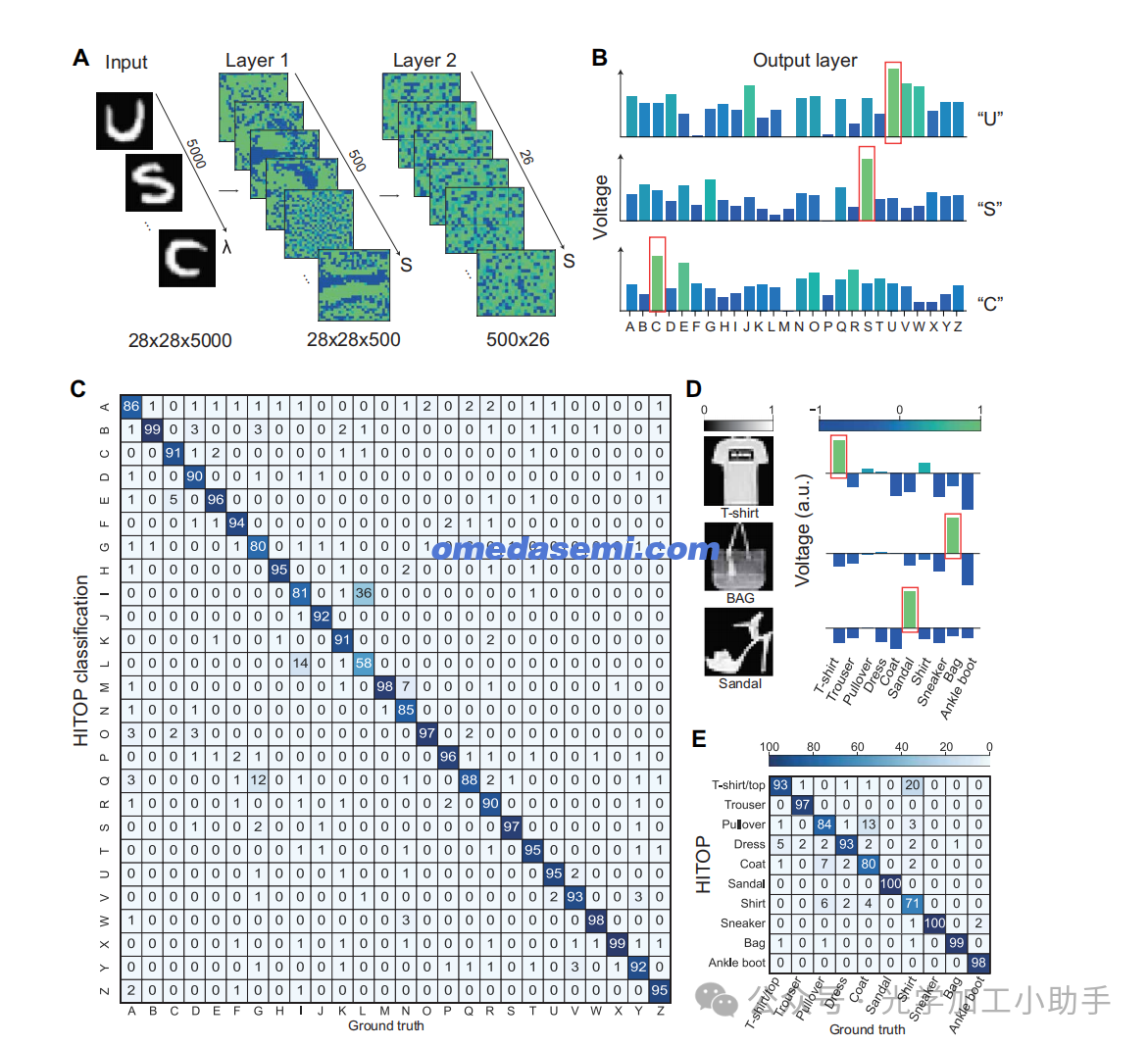

图4. 使用MNIST手写数字分类的HITOP基准测试

(A) 单层预训练神经网络模型的实现。10个权重向量被展平并流式传输到TFLN调制器上。图像被编码到VCSEL发射器中。

(B) 10 GS/s数据速率下的数字分类时间轨迹乘法结果;放大的图形显示时间轨迹与数字乘法具有高度一致性。

(C) 在10个空间模式输出的三个波长通道的时间积分电压。

(D) 和 (E) 七个不同波长通道的MNIST数字分类混淆矩阵,显示与数字模型相同的良好分类准确性(数字模型的数字见补充材料)。

HITOP的计算精度、可编程性和可扩展性通过AI推理任务中的图像分类进行了展示,使用修改版的国家标准与技术研究院(MNIST)数据集进行手写数字、字母和时尚识别。通过超多重操作,一批M个输入图像可以与N个权重向量同时相乘(图4A)。预训练的AI模型需要4到5位精度以实现最佳分类精度(图S9)。在实验实现中,每个28 x 28像素的图像被展平并转换为调制VCSEL输出强度的电压。使用一个单层网络(28 x 28 → 10),其中10个权重向量通过TFLN调制器进行编码。我们在每个光接收器处实现了一个积分电荷放大器(方法),以积累每个向量乘法生成的电流。数字的分类结果由输出最高积分电压的空间通道决定。以10 GS/s的数据速率(图4B),每个图像在78.4 ns内处理完毕,分类结果列在图4D中。为了验证消除的通道串扰,我们通过在100 MS/s下同时运行两个调制器和两个相邻的VCSEL,从七个波长和七个调制器收集数据;通过在所有波长通道收集数据,我们在七个波长通道中实现了高分类精度,数字准确率约为97%(图4,C到E)。实验条件总结在表S5中。我们通过结合高速度(10 GS/s时1 x 1同步通道)和低速度(相邻波长通道之间的2 x 2通道)验证了系统功能。我们重新编程了HITOP,进行更复杂的并行处理任务,并结合了激光阈值ReLU内联非线性。VCSEL偏置低于阈值以激活ReLU非线性功能(隐藏层),这可能允许级联多个模拟层,而无需将部分和转换为数字存储器(图S1)。我们通过在低于阈值的VCSEL偏置下验证了激光阈值ReLU非线性,通过随机数据编码,实现了(图S5到S7)在10 GS/s时2.78%的误差,未观察到由于跨越VCSEL阈值而导致的带宽减少。我们在100 MS/s下同时操作两个VCSEL和两个TFLN调制器通道,并通过切换通道,允许我们从所有七个设备通道收集数据。我们开发了一个三层网络模型(尺寸:28 x 28 → 100 → 10),用于识别带有ReLU函数隐藏层的时尚图像。

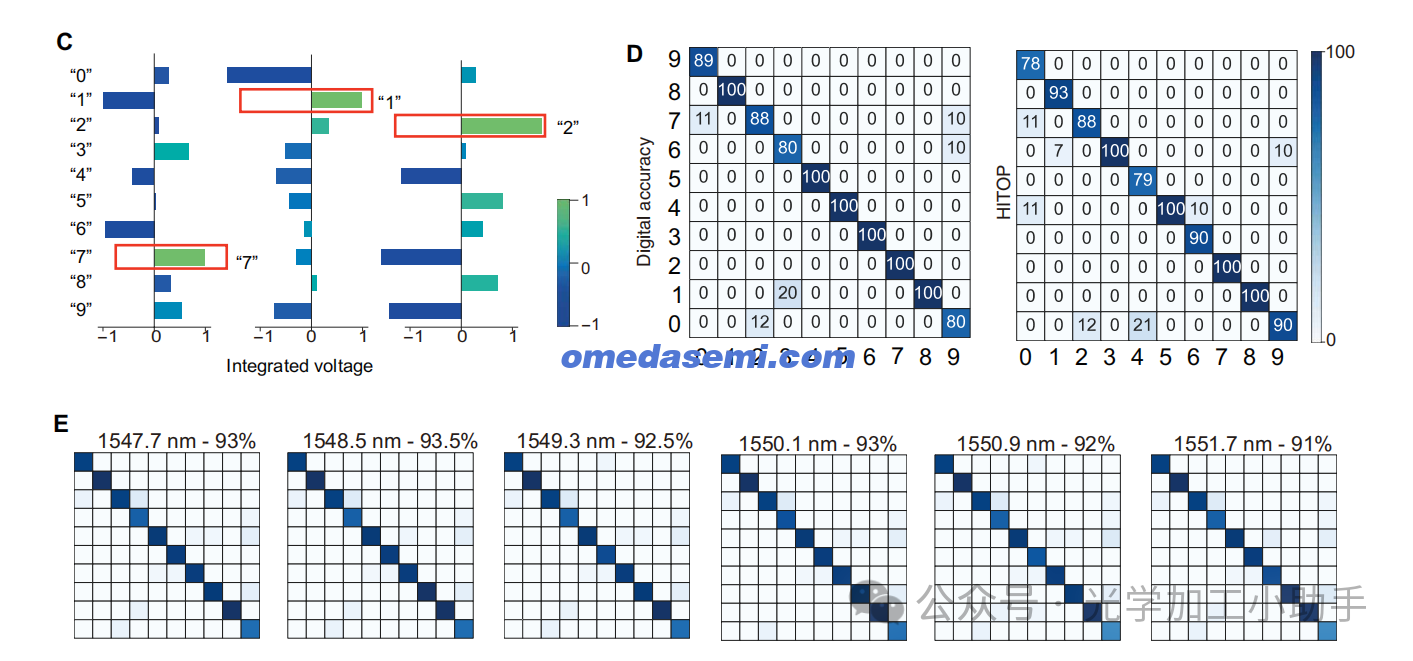

图5. HITOP在不同图像分类任务中的实验基准测试

(A) 用于EMNIST字母分类的两个隐藏层,网络大小为28 x 28 → 500 → 26。

(B) 来自HITOP输出层的读取电压,对于字母“U”、“S”和“C”显示高电压。

(C) EMNIST字母分类的混淆矩阵,测试集包含5000张图像,分类准确率为93.1%。

(D) 时尚MNIST分类,网络大小为28 x 28 → 100 → 26。三个示例图像的实验结果。

(E) 对1000张时尚MNIST测试图像的混淆矩阵,实验准确率为91.8%。

HITOP对1000个随机时尚图像样本中的91.8%进行了分类(图5),这一结果与数字准确率(94.3%)的统计误差相符。此外,HITOP的可扩展性通过EMNIST字母数据集(26个分类级别,模型大小为28 x 28 → 500 → 26)进行了基准测试。HITOP在5000个图像中实现了93.1%的分类准确性,总共进行了4,050,000,000次操作,展示了出色的系统稳定性。需要注意的是,模型包含405,000个参数,比之前的集成光学系统多25,000个(18-22, 46)(表S4)。

系统性能

HITOP为具有超维度并行性的可扩展光学计算提供了一个路径。其关键优势通过计算指标以及未来扩展潜力进行了说明。

(F1) 吞吐量(T)按照 T=2⋅M⋅N⋅R=0.98T = 2·M·N·R = 0.98T=2⋅M⋅N⋅R=0.98 TOPS 扩展,其中M = 7个VCSEL波长通道,N = 7个TFLN调制器,R = 10 GS/s。尽管所有通道的同时操作受限于现有驱动器,但通过100 MS/s下的多个通道操作和10 GS/s下的单通道操作验证了这一能力。需要注意的是,每个时钟周期的吞吐量按 O(M⋅N)O(M·N)O(M⋅N) 扩展,并且使用 O(N+M)O(N+M)O(N+M) 的调制器有效简化了系统以实现未来的扩展。

(F2) 光学加速器的能量成本包括光功率和电子-光学-电子(E-O-E)转换。HITOP通过集成接收器在实验中实现了18飞焦耳每操作(OP)的高光学功率效率(方法)。光功率的基本要求由目标计算精度设定,其中每次操作小于<1阿焦耳可能足以达到7到8位的精度,处于标准热噪声区(图S2),而这种低光功率已通过实验进行了小于1个光子每操作的基准(36)。这是实现高光功率扩展的关键,因为高芯片光功率由于材料击穿和激光功率的限制已成为光学系统的最终限制。

对于输入E-O转换,VCSEL和TFLN调制器分别以7飞焦耳和90飞焦耳每符号编码数据(方法),通过并行处理与N = 7个空间通道和M = 7个波长通道将其进一步摊销到几飞焦耳区域。对于输出O-E转换,积分读取减少了使用高速ADC(如CMOS光子传感器(47,48))的复杂性,这些传感器在数十百万符号/秒下每次读取消耗小于1皮焦耳。除此之外,每次读取包括2K(K = 28 x 28)MAC操作,这将有效读取能量转换为每操作的飞焦耳。因此,使用适当的驱动电路,整个系统的能量成本可达到~25飞焦耳每操作(=40 TOPS/W)(方法)。数字-模拟转换器(DACs)所需的额外能量成本用于驱动光学调制器,现有的CMOS技术在10 GS/s下每符号约为1皮焦耳[使用180纳米CMOS工艺(49)],这导致N = M = 7个通道的总功率成本为160毫瓦,整个系统的能效为160飞焦耳每操作,比最先进的CMOS GPU稍好(35)。通过采用更精细的特征尺寸或共同封装的光电子DAC(50,51),DAC功率效率可得到改善。

(F3) 芯片区域密度,σ=2×M×R/A2=17.5\sigma = 2 \times M \times R / A^2 = 17.5σ=2×M×R/A2=17.5 GOPS/mm²,目前受TFLN宽带调制器尺寸(20 mm x 0.4 mm)(方法)的限制,因为VCSEL调制器在相同调制速度下更为紧凑,光电探测器专门用于低速积分接收器,例如成像传感器中的数千万像素。通过为TFLN调制器增加更多波长以提高并行性和紧凑的器件设计,计算密度可以得到提高。

(F5) 非线性与延迟。VCSEL阈值下的ReLU非线性基于模拟E-O-E转换。在没有数字化的情况下,延迟由电荷放大器中的时间积分主导,在 K/R≈100K/R \approx 100K/R≈100 纳秒(在R = 10 GS/s和K = 1000时),对于AI训练来说这几乎可以忽略不计,并且足够用于大多数推理任务,这些任务需要实时决策。

讨论

我们探索了HITOP的可扩展性、可编程性和能效,针对基于芯片的平面AI处理。时间脉冲的数据映射减少了编码器设备的数量,并使未来的全系统性能扩展成为可能,例如,使用总共600个调制器(即M = 300个VCSEL和N = 300个TFLN调制器),HITOP可以支持M × N = 300 x 300个并行通道,吞吐量为 T∝2×N×M×R=1.8T \propto 2 \times N \times M \times R = 1.8T∝2×N×M×R=1.8 POPS,否则需要90,000个调制器和设备映射方案[例如Mach-Zehnder干涉仪(MZIs)(18)、光衰减器(46)或微环权重库(30)]。这一高通道数可能通过现有技术实现,因为基于InP的VCSEL覆盖从1.3到2μm的宽频率范围(52),而TFLN设备[具有350到5200 nm的透明窗口(34,53-55)],带宽超过500 nm(图S11到S13)以及用于复用和解复用的微环滤波器(56),如图S14所示。进一步的扩展可能受到VCSEL功率(~6 mW每设备)和WDM通道的光损耗(使用微环时每波长0.02 dB(56))(表S1)的限制。吞吐量T = 1.8 POPS与最先进的电子系统(35)相当,而整个系统的能效可能达到每操作fJ(257 TOPS/W)(表S2),高出100倍。能量成本主要由DAC转换主导,DAC功率效率可以通过共同封装的光电子DAC进一步提高,这些DAC已在硅光子学(51)和最近的TFLN平台(50)上得到了展示。

低能耗和可扩展计算的HITOP将开启各种领域的可能性和变革性应用。基于具有动态可编程性的三维数据流,HITOP适用于低能耗训练具有万亿参数的模型。这可能为语言处理和机器视觉中的更大AI模型提供支持,并为自动驾驶汽车和机器人中的智能传感器提供低延迟、高效能的解决方案,从而提高边缘张量处理器的处理能力,实时决策能力。超越AI应用,计算能力将加速复杂物理和生物系统(例如气候变化和分子动力学)的仿真和建模,以准确预测环境挑战以及药物发现和医疗保健。