摘要

由于其稳定性和可扩展性,光子集成电路 (PIC) 有望在正在进行的第二次量子革命中发挥重要作用。然而,现有的 PIC 平台仍需要进行重大升级,以满足量子设备的苛刻要求。在本文中,我们回顾了我们最近在升级非常规硅光子平台以实现这一目标方面取得的进展,包括超低传播损耗、低光纤耦合损耗、超导元件集成、法拉第旋转器、快速高效的探测器以及低损耗和/或低能耗的相位调制器。我们在两个主要应用中展示了我们的发展和愿景的相关性:量子密钥分发——实现显著更高的密钥速率和大规模部署——以及低温量子计算机——用光纤取代与低温恒温器的电连接。关键词:硅光子学、量子密钥分发、量子计算机、低温光子学、超导纳米线单光子探测器、量子技术、超导量子比特、硅量子比特

1. 简介

我们目前正在经历所谓的第二次量子革命,其焦点已从纯科学转向技术和应用1。光子技术有望发挥重要作用,不仅在量子应用中,而且在支持固态量子系统的经典配置中也是如此。特别是,光子集成电路 (PIC) 为不同的量子技术提供了独特的机会,可以扩大系统复杂性和集成密度,同时提供无与伦比的性能和稳定性2–6。在这方面,微米级硅光子平台7 带来了一组独特的属性和构建块。这包括低传播损耗(迄今为止已证明低至 3 dB/m8,9)、宽带和低损耗光纤耦合(≈ 0.5 dB)、快速(> 40 GHz)和响应迅速(≈ 1 A/W)集成锗光电探测器10、用于宽带和低损耗耦合到探测器阵列的上反射镜、实现高集成密度的紧弯曲11、高效移相器、低损耗马赫-曾德尔干涉仪、数百万个 Q 环谐振器9,12、偏振不敏感操作以及偏振分束器13 和旋转器,包括全硅法拉第旋转器14。一个相关的示例应用是大规模部署量子密钥分发 (QKD),为此我们正在开发高效的多路复用接收器。第二个有趣的案例是利用我们的光子集成技术通过经典光学链路控制和读取低温恒温器中的量子比特来扩大超导量子计算机的规模。在这种情况下,主要的挑战是开发在低温下工作的合适的电-光和光电转换器。

在下文中,我们将介绍这些正在进行的开发,展示我们最近的成果以及我们进一步开发该平台的计划。在第 2 节中,我们将首先概述厚硅光子学平台,特别关注与量子技术最相关的特性。在第 3 节和第 4 节中,我们将介绍 QKD 和量子计算机的持续发展,然后在第 5 节中总结并简要提及其他有希望的未来发展和应用。

2. VTT 厚 SOI 平台概述

我们可以将平台的构建块分为两大类:无源器件和有源器件。在此上下文中,“有源”是指需要电控制(如热光移相器和电光调制器)或电读出(如光电二极管)的任何东西。图 1 概述了平台上可用的主要构建块,但基于 PIN 二极管的相位调制器除外,这将在 §2.2 中详细说明。我们在直径为 150 毫米的绝缘体上硅 (SOI) 晶圆(即将升级到 200 毫米)上制造 PIC,器件层厚度为 3 µm(± 100 nm 均匀性),使用 UV 步进机(365 nm 波长)和改进的 Bosch 工艺 15,16 蚀刻波导。

图 1. 厚 SOI 平台上可用的主要构建块的草图。器件层的典型厚度为 3 µm,而埋层氧化物 (BOX) 厚度可以从 400 nm 到 3 µm 不等。我们将“有源”构建块定义为需要电焊盘进行控制或读出的构建块。

2.1 无源构建块

波导类型

平台上可用的五种主要波导类型是:肋状波导、条状波导、下锥形条状波导、带薄基座的条状波导和带薄基座的下锥形条状波导(后者是图 1 中唯一缺少的类型)。对于肋状波导,在波导的两侧都部分蚀刻沟槽(通常蚀刻深度为 1.2 µm)。通过选择合适的肋宽度 17(通常 ≤ 3 µm),可以实现横电 (TE) 和横磁 (TM) 极化的单模操作。相反,所有四种可能的条带波导横截面本质上都是多模的。尽管如此,我们还是精心设计了光学电路,使得连接波导中的高阶模式 (HOM) 的激励始终可以忽略不计,从而确保整个电路的有效单模操作。

I/O 耦合

我们首先蚀刻硅面,然后沉积合适的抗反射涂层,以晶圆级制造 PIC 的垂直波导面,该涂层可以由单个介电层或多个层制成。

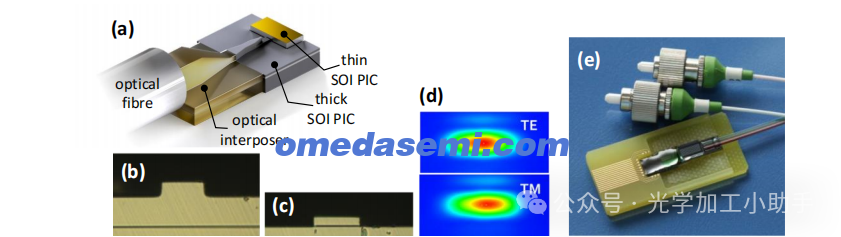

图 2. (a) 使用在 12 µm 厚 SOI 上制作的光学中介层,从 SMF 耦合到厚 SOI PIC 的 3 µm 厚波导开始的不同模式尺寸转换的示意图。该示意图还显示了如何进一步减小模式尺寸,甚至将光耦合到可以通过合适的倒装芯片粘合 PIC 上的亚微米波导,该波导可以通过合适的倒装芯片粘合 PIC 进行衰减耦合;(b) 制作的光学中介层的 12 µm 厚肋形波导的显微照片和 (c) 在相对面上抛光至约 3 µm 厚度的条形波导的显微照片;(d) 中介层输出面的 TE 和 TM 模式的近场图像(红外摄像机)(如图 (c) 所示);(e) 封装的 3 µm 厚 SOI PIC 通过光学中介层耦合到光纤阵列。

如果模场直径约为 2.5 µm,则光纤的耦合损耗可低至 0.5 dB,这可通过带透镜(或锥形)光纤或具有高数值孔径的小芯光纤实现。在 PIC 具有多个输入和输出的配置中,必须改用光纤阵列。鉴于光纤阵列的组装精度有限,并且考虑到对错位的容忍度与模式尺寸成反比,只有通过模式直径约为 10 µm 的标准单模光纤 (SMF) 阵列才能确保低损耗耦合。这需要合适的模式尺寸转换器,如图 2 所示,通过在具有 12 µm 厚的器件层的 SOI 晶片上蚀刻 12 µm 宽的肋形和条形波导阵列来制造,然后通过抛光每个光学中介层芯片将输出条形波导的厚度减小到 3 µm。我们目前正在努力通过实施 3D 打印透镜 18(以晶圆级方式直接打印在波导面上)进一步将耦合损耗降低至 0.5 dB 以下。这样,我们的目标是将 PIC 直接耦合到 SMF 和光纤阵列,实现超低损耗和宽松的对准公差 19。

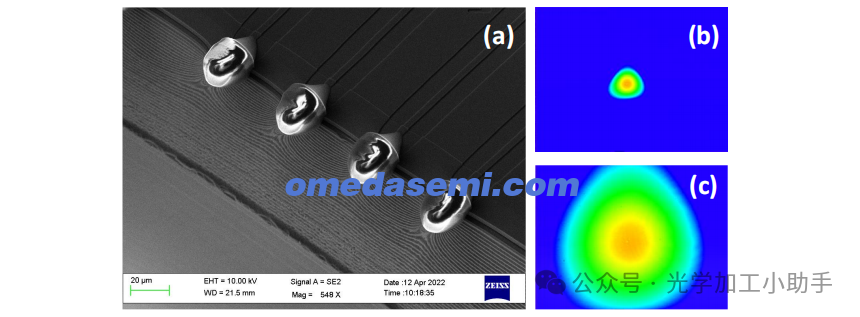

图 3. a) 在四个肋形波导端面前 3D 打印的聚合物透镜的 SEM 图像;b) 用红外摄像机拍摄的肋形波导输出模式的近场图片;c) 带透镜的肋形波导输出的近场图片(与 b) 相同的比例)。

光也可以从上反射镜(URM,见图 1 和图 4)垂直耦合到 PIC,这些镜以负角度湿蚀刻。它们的工作原理是全内反射,耦合损耗实际上与垂直面相同。URM 的防反射涂层与垂直面相同。湿法蚀刻过程沿晶面进行,这意味着只能沿米勒指数为 110、1̅10、11̅0 和 1̅1̅0 的四个正交晶面制造镜子。URM 的优点之一是可以使用它们在晶圆级上测试制造的 PIC。

图 4. (a) 制备的 URM 的显微照片和 (b) 通过聚焦离子束显微镜观察的 URM 垂直横截面的侧视图

与通常用于亚微米波导的光栅耦合器相比,URM 支持 TE 和 TM 极化,且极化相关损耗可忽略不计,并且可在硅的整个透明度范围内工作,波长范围从 1.2 µm 到 7 µm。我们在此还强调,厚 SOI PIC 可在硅的整个透明度范围内工作。特别是,可以设计一个肋形波导,使其在该宽光谱范围内的所有波长上都是单模的,跨越几个倍频程17。我们必须强调的是,在 3 µm 波长以上,二氧化硅包层(包括埋层氧化物和顶部包层,见图 1)中的吸收会导致传播损耗。然而,由于厚硅芯的强约束,传播损耗在波长约 4 µm 时仍保持在 1 dB/cm 以下,通过选择性地去除波导周围的二氧化硅包层 20,可以实现波长高达 7 µm 的低传播损耗。这与基于薄 SOI 的 Si 光子平台形成了鲜明对比,在这些平台上,即使在电信波长 20 下,传播损耗通常也高于 1 dB/cm,因为与侧壁粗糙度的相互作用更强。此外,亚微米波导模式的包层中的功率分数与厚 SOI 波导相比要大几个数量级,这意味着二氧化硅包层 21 中的吸收在波长超过 2.5 µm 时就已经变得难以忍受。中红外操作对于许多气体传感应用22(包括量子传感23)至关重要,并且还可以利用硅的强三阶非线性,此外,厚SOI中较大的光学模式尺寸可以避免由短于2.2 µm的波长处的强双光子吸收24(以及相关的自由载流子吸收25)引起的饱和。虽然波导的大横截面积并不理想,无法有效激发非线性效应(包括寄生双光子吸收),但与超低传播损耗的独特组合在许多应用中都是有利的26,27。

紧密弯曲可实现高集成密度

通常认为,具有微米级横截面的波导需要几毫米的弯曲半径。这是因为确保微米级波导中单模操作的折射率对比度固有地会导致更紧密弯曲的高辐射损耗。在该平台中,我们针对这一限制开发了两种解决方案:

基于 TIR28 的旋转镜(图 5(a) 和 (b))和称为欧拉弯 11 的紧密绝热弯(图 5(a))。

第一种方法适用于肋形波导和条形波导,而第二种方法需要高折射率对比度条形波导。

图 5. (a) 肋状波导和条状波导上的 90° 旋转镜的 SEM 图片;(b) 基于 TIR 镜的紧凑型不平衡 MZI 的细节;(c) L 形和 U 形欧拉弯的 SEM 图片以及使用较大 L 形弯的螺旋波导的细节。

TIR 镜允许紧凑布局,如图 5(b) 所示的不平衡马赫曾德尔干涉仪 (MZI),

该图还显示了平台上可轻松实现的极低损耗 (≈ 0.02 dB) 波导交叉。旋转镜可以设计为几乎任何旋转角度,通过使用抛物线形状和/或使波导足够宽,其损耗可以低至每转 0.1 dB。事实上,主要的损耗机制是由于镜面区域部分缺乏横向引导而导致的光衍射。值得注意的是,旋转镜可在硅的整个(1.2 至 7 µm)波长透明区域内工作,并且可以设计为同时对 TE 和 TM 偏振同样有效,尽管 Goos-Hänchen 位移 29 会引起偏振相关偏移。然而,不可忽略的损耗使它们不适合需要大量弯曲的电路,例如长螺旋波导。

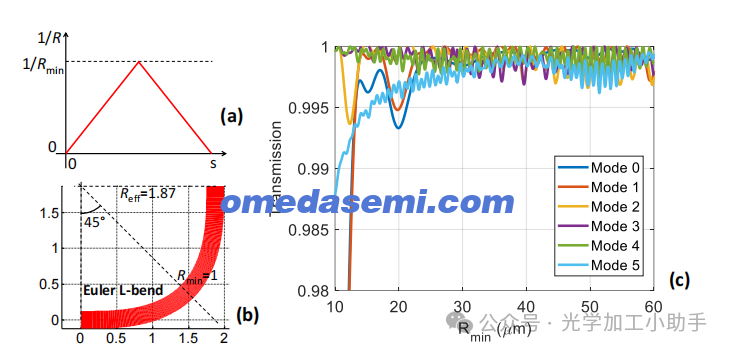

为此,我们还开发了更传统的波导弯曲以实现更低的损耗。它们基于条形波导,确保由于强光限制而导致的辐射损耗可忽略不计。唯一的限制是它们支持在紧密弯曲中容易激发的多个 HOM。因此,我们引入了 11 并获得专利 30 一种曲率逐渐变化的几何形状,使用欧拉螺旋几何形状,如图 5(c) 和图 6(a) 和 (b) 所示。这样就可以实现损耗低于 0.02 dB 的紧密弯曲,有效弯曲半径为几十微米例如,可以实现品质因数 Q 高达 1400 万的紧凑赛道谐振器9,12。

图 6. (a) 曲线显示了欧拉弯中曲率 1/R 随长度 s 变化的线性变化,从零开始,达到 1/Rmin,然后对称地回到零;(b) 90° 欧拉弯(或 L 形弯)的示例布局,最小弯曲半径为 1,显示了最终的有效半径 Reff;(c) 模拟 1.5 µm 宽条带波导在 90° 欧拉弯输出端的 TE00 模式和五个水平高阶 TE 模式的传输,该传输与最小弯曲半径有关。五个 HOM TEn0 模式(n = 1…5)在水平方向上有 n 个节点,在垂直方向上有零个节点。波长为 1.55 µm。尽管一般来说,弯管的工作波长范围不如旋转镜那么宽,但弯管

可以设计为覆盖几百纳米到几微米的带宽。欧拉弯管的一个有趣特性是,它们非常有效地传输大多数受支持的 HOM31(即有效折射率足够高于包层折射率的 HOM),如图 6(c) 所示。换句话说,弯管保留了模式功率分布,这在设计用于模式复用的 PIC32 和使用空间模式作为量子自由度33–36(另见 §5)时非常有用。值得一提的是,旋转镜在反射下也保留了 HOM 功率分布37。

偏振管理

微米级硅波导支持 TE 和 TM 偏振,具有非常相似的空间模式分布、相同的传播损耗和非常相似的有效指数。事实上,具有方形横截面的带状波导可以支持具有相同传播常数的 TE 和 TM 基本模式。材料应变引起的任何可能的残余双折射都可以通过微调波导宽度轻松补偿。

图 7. (a) 利用不同宽度波导的形式双折射作为 PBS 的 MZI 示意图;(b) 通过在芯片上结合 PBS、法拉第旋转器 (FR) 和互易偏振旋转器实现集成光循环器的可能方案

大多数构建模块,包括多模干涉 (MMI) 分离器,都可以设计为同时支持两种极化。另一方面,在许多应用中(包括电信和传感),极化可以用作自由度,在这种情况下需要极化分离器/组合器,最好还需要不同类型的极化旋转器。我们目前正在开发用于极化管理的多种构建模块,包括 MZI 极化光束分离器 (PBS)13,38(见图 7(a))和旋转器39。值得注意的是,我们已经证明了硅本身作为磁光材料的用途,并在零双折射波导中实现了法拉第旋转14。我们的最终目标是构建一个基于分离器/组合器和互易和非互易旋转器的全集成全硅循环器(图 7(b))。我们在本节的最后提到,法拉第镜常用于量子光子学,包括量子密钥分配系统(见§3),以确保稳定运行40,41,因为反射光的偏振始终与输入偏振42正交(即庞加莱球上的对映体)。通过将法拉第旋转器与 MMI 反射器或萨格纳克环43等背反射器相结合,可以在平台上实现法拉第镜。

低损耗波长滤波器

我们已经展示了几种不同类型的波长滤波器,包括 Q 高达 1400 万的环形谐振器9,12、紧凑型 MMI 谐振器43、平顶格子滤波器44和平顶环加载 MZI45

。其中一些滤波器可以设计为具有小于 0.5 dB 的过量损耗。我们还展示了低损耗梯形光栅和阵列波导光栅 (AWG)46。在图 8(a) 中,我们展示了由于使用欧拉弯而占用空间较小的 AWG 布局。由于采用了横截面积为方形的条形波导,该设备与偏振无关。额外损耗在 2 dB 到 3 dB 范围内,消光比 (ER) 大于 25 dB。我们还展示了损耗在 1 dB 到 2 dB 范围内的 AWG46,并且所有通道的 ER 都超过 30 dB。我们目前正在通过改进星形耦合器的设计和制造来进一步减少额外损耗。对于如图 8(a) 所示的梯形光栅,我们已经证明了两种偏振的额外损耗都低于 1 dB,并且所有通道的消光比都超过 20 dB。

图 8. (a) 具有 100 GHz 通道间隔和 5 nm 自由光谱范围的紧凑型 AWG,利用欧拉弯曲和接近零的双折射波导,确保偏振独立操作;(b) 具有 100 GHz 通道间隔的循环梯形光栅。

连接微型和纳米级设备

图 9. (a) 使用本征模扩展方法对从 3 µm 厚的 c-Si

波导到在其上制作的 400 nm 厚、200 µm 长的 a-Si:H 锥形波导的绝热功率传输进行 3D 模拟;(b) 两个自动扶梯的 3D 草图,用于将光耦合到 a-Si:H 波导,然后再耦合回 3 µm 厚的波导,显示了在光在 a-Si:H 中传导的区域中,功能层可以夹在两种硅类型之间;(c) 不同类型的自动扶梯将光耦合到亚微米波导

微米级波导技术的低传播损耗伴随着与直接集成在波导顶部的任何元件的弱相互作用。这个问题已经通过不同的制造技术成功解决,而不会危及平台的性能。例如,最近我们一直在开发一种由氢化非晶硅 (a-Si:H) 制成的轻型自动扶梯 47,以将微米级波导与亚微米波导、包括 2D 材料在内的薄层和超导纳米线连接起来。我们在晶体器件层(1550 nm 波长下的折射率约为 3.48)顶部生长一层亚微米 a-Si:H 层(折射率约为 3.65),并对其进行图案化以实现绝热光耦合。图 9(a) 中的模拟显示了光如何从厚硅波导传播到更薄的 a-Si:H 层。可以优化 a-Si:H 层厚度以最大限度地增加传播光与石墨烯层(用于光检测 48 或调制 49 等应用)或夹在晶体硅 (c-Si) 和 a-Si:H 之间的超导纳米线单光子探测器 50 (SNSPD,另见 §2.2) 的重叠,类似于图 9(b) 中所示的情况。此外,在沉积 a-Si:H 层之前,还可以选择性地去除晶体硅并用沉积的二氧化硅层替换,如图 9(c) 所示。由此产生的高折射率对比度 a-Si:H 波导使我们能够将微米级波导与亚微米波导(包括等离子体槽波导或甚至只是基于亚微米硅波导的 PIC)连接起来,这些 PIC 可以简单地粘合在 a-Si:H 波导的顶部并通过倒锥形衰减耦合。两种类型的自动扶梯都可以使用相同的制造工艺制造。将微尺度波导与纳米光子设备耦合的另一个独特机会来自 URM。事实上,有些情况需要光在功能表面上传播(与自动扶梯的情况不同,自动扶梯沿着它传播)。在这些情况下,可以制造功能表面,或者只是将其转移到镜子的平坦输出表面(由结晶光滑硅制成,未蚀刻)的顶部。这是集成超表面(包括波片51、超透镜52或电光调制器53,54)的直接方法。然而,镜子的有限尺寸(波导传播方向为3μm,即几个波长)可能对超表面的设计构成挑战。

2.2 有源构建块

我们可以将有源元件分为两大类:电光转换器(EOC),在厚SOI平台中,基本上都是移相器(热光或电光)和光电转换器(OEC),即光电探测器。

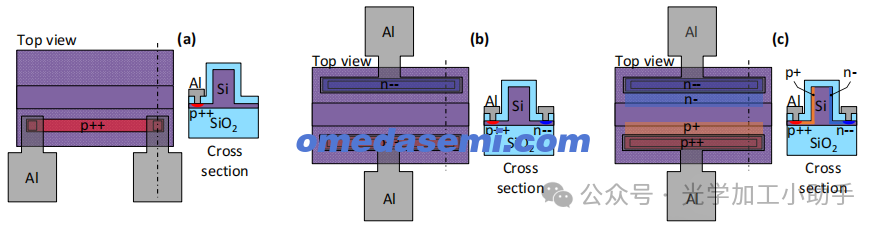

移相器

我们通过在条形波导底部植入薄硅基座来实现热光移相器(图 10(a))。我们通常会切掉基座的剩余部分以实现更低的功耗,达到每 π 移位约 25 mW,上升时间和衰减时间均为约 15 µs(即速度约为 66 kHz)。最近,我们还通过在特殊腔体 SOI 晶片上制造加热器(限制了流经基板的热流)实现了每 π 移位约 2 mW(尚未公布)。与基于放置在波导上覆层顶部的金属线的加热器相比,将加热器直接与硅层接触可确保显着减少热串扰 55。这对于需要多个热光移相器的复杂电路来说是一个主要优势。根据设计,热光移相器不会产生额外损耗

图 10. 平台上可用的三种主要移相器的顶视图和横截面:(a) 热光(另见图 1);(b) 电光,基于通过 PIN 结中的载流子注入实现的等离子体色散;(c)电光,基于通过 PIN 结的高反向偏置电压的 EFIPE。当需要更高的速度时,我们可以使用简单的 PIN 结达到约 2 到 3 MHz,只有一个注入水平,如图 10(b) 所示。在这种情况下,折射率由于载流子注入引起的等离子体色散而发生变化56。π 移位的功耗低于 5 mW。然而,由于 Kramers-Kronig 关系29 ,等离子体色散固有地在相位调制之上增加了幅度调制。与π 移位相关的损耗在 1 dB 到 2 dB 的数量级上。事实上,当制作得足够长时,相同类型的 PIN 结也可用于可变光衰减器。

57为了克服这些限制,我们还与东京大学密切合作,开发了依赖于所谓的电场诱导普克尔斯效应 (EFIPE,见图 10(c)) 的相位调制器。

58 对于这些调制器,我们预计由于高反向偏置(电场约为 40 V/µm,尽可能接近击穿),额外损耗会显著降低。特别是,我们预计相位调制不会产生任何重大的幅度调制。

此外,我们的目标是达到超过 1 GHz 甚至接近 10 GHz 的调制速度。我们还预计功耗在每 π 移位微瓦范围内,这对于低温应用非常重要。事实上,EFIPE 在低温下也能很好地工作59,因为它不受载流子冻结的影响,不像等离子体色散60。

为了实现极低功耗和超过 100 GHz 的调制速度,我们还与苏黎世联邦理工学院和 Polariton Technologies 公司合作开发等离子体调制器61。除了基于非线性聚合物的传统方法外,我们还在探索使用 a-Si:H 作为基于 EFIPE62的非线性材料的可能性。我们指出,等离子体调制器也特别适合低温应用63,因为它们不依赖于电荷载体并且具有超低功耗64。等离子体移相器的主要限制是过量损耗高,通常超过 5 dB。但是,如第 3 节所述,这在某些应用中是可以接受的。总结本节,我们指出,所有平台中量子 PIC(QPIC)都缺少一个关键构建模块,即合适的移相器,以便同时实现小尺寸、超低功耗、高速度、超低光损耗和低温操作,或者至少实现这些特性的一部分,具体取决于应用。最近的结果表明,使用微机电系统 (MEMS) 是亚微米硅 65 和氮化硅 66,67 平台的一条有前途的途径。这种方法可以导致损耗低于 0.5 dB,速度从几 MHz 到 100 MHz 以上,尺寸范围从约 100×100 µm2 到 1×1 mm2。我们目前正在探索的另一种途径是将电光超表面 53,54 放置在 URM 之上,以获得更快、更紧凑的移相器。这里的目标是获取电光聚合物的完整非线性系数,该系数通常在等离子体槽波导68中降低一个数量级。

探测器

该平台包括单片集成锗 (Ge) 光电二极管 (PD),在 1550 nm 波长下响应度约为1 A/W,即量子效率为 80%。我们开发了高速 PD 和监视器 PD。高速 PD 在 1 V 反向偏置 10下工作时速度超过 40 GHz,暗电流约为 4 µA,而监视器 PD 在较低偏置电压下工作,暗电流约为 10 nA,速度约为 1 GHz。

我们目前正在开始对 PD 进行低温表征,以确定暗电流69、响应度、信噪比70、速度、载流子冻结和检测波长范围的温度依赖性。我们还在开发利用硅中雪崩效应的雪崩光电探测器71 (APD)72,并计划在盖革模式下操作它们以实现单光子雪崩探测器 (SPAD)73。

此外,我们还与苏黎世联邦理工学院合作,开发高速等离子体 Ge 探测器,以超过 500 GHz 模拟带宽74,75。这里的主要驱动因素不是检测效率,而是几开尔文的高速操作,目标是开发合适的 OEC 以将大量数据传输到低温恒温器。如第 4 节中更详细地解释的那样,这个想法是使用光纤驱动超导电子器件(例如单通量量子,SFQ)。随着低温和量子应用在 m

图 11. (a) 制备的 NbN SNSPD 在沉积 a-Si:H 之前的 SEM 照片;(b) 蚀刻 a-Si:H 波导后制备的芯片细节显微照片;(c) 嵌入 NbN 纳米线的 a-Si:H 波导的横截面草图(绿色)。

SNSPD 是迄今为止最接近理想单光子探测器的探测器,探测效率超过 97%,延伸到电信波长范围78,速度在 GHz 范围内79,抖动甚至低于 3 ps80,暗计数低于 0.1 Hz81。然而,对于某些量子实现82–84,尤其是基于高斯态的量子实现,光子数分辨率 (PNR) 是一项重要功能,SNSPD 不易实现。一种可能的解决方案是过渡边缘传感器 (TES)85,但它们的速度目前限制在 1 MHz 左右。不幸的是,TES 需要 100 mK 左右的温度,这无法通过闭环台式低温恒温器实现,而需要更复杂、更笨重的亚开尔文冷却器,例如稀释制冷机。然而,这里应该注意的是,目前在 VTT 开发的固态冷却技术可以提供一种可行的解决方案,以便在未来集成紧凑型亚开尔文制冷机86,87。这些冷却器是超导体 - 硅混合芯片,可以通过 3D 集成方案(例如倒装芯片键合)直接连接到 PIC。这将使简单、经济高效、紧凑的脉冲管系统内的电路能够达到亚开尔文工作温度。TES 在光波导上的集成已经在其他平台上得到演示88,89。我们的集成方法

与我们上面对 SNSPD 的解释一致,并利用了 VTT 开发的 TES 像素90 和基于 SQUID 的读出技术91。从更广泛的角度来看,基于 Nb交叉结92 的内部集成超导器件技术可以为微米级平台的量子升级提供有趣的机会(另见§4)。

例如,我们目前将该技术用于 TES 读出电路89、SQUID 磁强计93 和不同的Josephson 参数设备94–96。此外,我们还与皇家理工学院 KTH 和Single Quantum 公司合作,探索将单个 SNSPD 用作高效 PNR 探测器的可能性97–99。

2.3 混合集成

目前有几种不同的 PIC 技术,包括最成熟的亚微米和微米级硅和氮化硅20平台、微米级磷化铟100平台,以及较新的绝缘体上铌酸锂平台101-104和绝缘体上化合物平台105。每种材料系统都有其优点和缺点,因此通常需要适当组合互补系统才能实现完全集成的解决方案。一个典型的例子是,所有不基于化合物半导体的平台都缺乏单片集成光源,需要异质集成106或混合集成7,107才能在芯片上产生光。我们在 VTT 的主要重点是基于晶圆级高精度倒装芯片键合的混合集成,这适用于像我们这样的 CMOS 制造工厂的中等批量生产。与异构和单片集成不同,在混合方法中,硅工艺和 III-V 工艺(或任何其他互补材料系统的工艺)可以在两个不同的制造设施中同时进行,这具有几个优点。这些优点包括总交付周期更短、工艺流程复杂性降低、两种材料系统的约束和权衡减少以及两种工艺的产量分离,从而提高总产量,即提高成本效率。混合集成的另一个优点是它不受单片集成中可能出现的约束(例如 CMOS 兼容性和热预算)的约束。此外,混合集成可以使用市售的芯片(例如光源或光电探测器)进行,从而可以提高成本效率。通过使用垂直面或 URM,我们可以轻松集成光在平面内传播的设备(如分布式布拉格反射器激光器、半导体光放大器或电吸收调制器)或非平面传播的设备(如垂直腔发射激光器或自由空间光电探测器)。特别是,URM 可以成为 QPIC 的关键组件,因为它具有极低的损耗、宽带和偏振无关性。例如,它可用于高效

将基于垂直腔中量子点的确定性单光子源的光耦合108,或将单光子或高斯态耦合到短 SNSPD 阵列(见图 12b)。我们在此强调,尽管我们有一条明确的 SNSPD 单片集成路径(见 §2.2),但基于上述考虑,在我们开发出具有足够高产量的 SNSPD 制造工艺之前,混合集成将是大型 SNSPD 阵列最有效的集成方法。

3. QKD 接收器

厚 SOI 平台可以实现的第一个示例应用是具有更高密钥速率和/或更长工作距离的量子密钥分发 (QKD) 网络109。事实上,PIC 解决方案因其无与伦比的稳定性和可扩展性而出现在主要 QKD 参与者110 的产品路线图中。事实上,迄今为止已报道了几个基于 PIC 的实现示例,涵盖了不同类型的 QKD 方案 111–119。我们已经确定了一条清晰的路径,说明该平台如何支持离散变量 (DV) QKD 和连续变量 (CV) QKD 高性能 QKD 系统的开发和大规模部署,如下文简要介绍。

3.1 DV-QKD

DV-QKD 系统最适合覆盖长距离。迄今为止报道的最长 QKD 链路使用具有中央节点的特殊配置 120,121 达到 830 公里,而最长的点对点链路超过 400 公里 122(相当于超低损耗光纤中约 70 dB 的损耗)。最好的商用系统通常限制在 100 公里到 150 公里的范围内,主要是为了确保安全通信和足够高的密钥速率以供使用。事实上,在最适合长距离的 DV-QKD 实现中,密钥速率与链路传输概率 η 成线性比例,η 是传输光子在接收器处被检测到的概率,考虑了所有可能的传输和耦合损耗以及有限的检测器效率 123。与经典光通信链路形成鲜明对比的是,这种密钥速率缩放意味着传输速度和检测速度之间存在很大的不匹配。换句话说,检测器可以比调制器慢几个数量级,这是一个独特的机会,可以将有史以来最快的光调制器与迄今为止展示的最高效的单光子检测器(即等离子体调制器和 SNSPD)结合起来。目前 QKD 系统的发射机速度在几 GHz 的数量级上,这意味着等离子体相位和幅度调制器可用于将密钥速率提高至少两个数量级,同时仍与接收器端的 SNSPD 很好地匹配。事实上,目前商用的 SNSPD 可以轻松超过 10 MHz 计数率,检测效率超过 80%,未来可能超过 GHz 计数率和 95% 检测效率。我们强调,等离子体调制器的高损耗是传统光通信的一大限制,但对于基于强衰减光源的实用 DV-QKD 发射器来说,这根本不是问题。另一方面,接收器无法容忍高损耗,因此等离子体调制器不适用于协议(如标准 BB84),因为在接收器端也需要调制器来选择测量基础。然而,这并不是一个很大的限制,因为实用 DV-QKD 最强大的协议依赖于无源接收器,不需要调制器 122,124,125。考虑到一些最有前途的 DV-QKD 协议,包括独立于测量设备 (MDI) QKD126,127 和双场 (TF) QKD120,123,通过中央单元 (完全不受信任) 连接用户,所有光子检测都发生于此 (图 12(a)),等离子体调制器和 SNSPD 的组合变得更具吸引力。可以通过为所有用户提供低成本发射器 (可通过等离子体芯片实现) 来实现这些系统的大规模部署,同时部署由运营商拥有的中央检测单元来托管桌面闭环低温恒温器,其中数千个 SNSPD 可以经济地冷却并并行运行。在这个愿景中,低温恒温器将连接到数十到数百根光纤,每根光纤应承载数十到数百个波分复用 (WDM) 信号。为此,我们目前正在 VTT 制造低损耗 AWG,以对来自单根光纤的 WDM 信号进行解复用,并将它们耦合到由 Single Quantum 设计和制造的倒装芯片粘合的 SNSPD 阵列,以匹配我们的布局(见图 12b)。AWG 和 SNSPD 的单片集成已经得到证实128,但光纤耦合和解复用都存在高损耗。此外,由于 SNSPD 制造良率相对较低,大型 SNSPD 阵列的单片集成仍然具有挑战性。SNSPD c 的混合集成最近,研究人员使用亚微米硅波导129演示了仅具有两个探测器的 HIP,用于时间复用 MDI-QKD。其中演示的耦合损耗非常高,因为使用光栅耦合器耦合光纤和 SNSPD。相反,我们的目标是同时确保高产量、宽带低损耗光纤耦合、低解复用损耗的解决方案,并且通过适当设计 SNSPD 甚至可以使其对偏振不敏感

图 12. (a) 基于光子检测中心节点的 QKD 实现示意图,其中所有用户都配备了合适且低成本的发射器;(b) 我们与合作伙伴 Single Quantum 共同开发的解决方案的 3D 草图,用于解决具有低损耗和高制造产量的 SNSPD 阵列问题。

3.2 CV-QKD

另一种方法是 CV-QKD,它依赖于高斯态而不是单光子。主要优点是它的实现41只需要用于经典相干光通信的标准电信组件,特别是不需要单光子探测器。主要缺点是安全实现与传输概率 η 成二次方关系,这将操作范围限制在约 50 公里(或更严格地说,10 dB 损耗,假设标准 0.2 dB/km 光纤损耗)。此外,与 DV-QKD 不同,接收器速度必须与发射器速度匹配。在发射器方面,等离子体调制器再次成为完美的选择,因为它们的损耗很容易容忍,并且可以轻松同时实现相位和幅度的超快调制64。接收器端也需要超快相位调制,但仅限于本地振荡器,而不是量子态41,这意味着一些调制器损耗是可以接受的。检测通常使用散粒噪声限制平衡脉冲零差探测器41进行,其运行速度和稳定性可以从 PIC 集成和专用电子设备132 中大大受益。因此,我们计划利用快速 Ge PD 结合我们在超快电子设备方面的内部专业知识133,134 来开发速度超过 50 GHz 的平衡光电探测器。我们强调,尽管我们目前的 Ge PD 的速度被限制在 40 GHz 左右,但最近已证明体积较小的适当设计的 Ge PD 可以达到 265 GHz135。在我们的设想中,CV-QKD 接收器将单片集成在我们的厚 SOI 平台上,包括超快等离子体相位调制器和平衡光电二极管。同样在这种情况下,与基于光纤的实现相比,PIC 将确保更好、更稳定地控制相对相位和时间抖动,从而提高整个 QKD 系统的整体性能。在发射器方面,在我们的平台上集成等离子体设备并不是绝对必要的,但它可以提高操作稳定性,例如通过集成法拉第镜(参见 §2.1),这是任何其他 PIC 平台都没有的。类似的考虑也适用于 DV-QKD 发射器。事实上,DV-QKD 和 CV-QKD 的许多实际实现都依赖于法拉第镜 41,122,125。

该平台还可以支持 QKD 以外的量子通信应用。一条有希望的途径是开发声光设备,以有效地将超导量子比特或自旋量子比特转换为光学量子比特,反之亦然。

这样的传感器将使我们能够通过光纤中的光量子态连接量子处理器,并创建基于多量子处理器架构的更强大的量子计算机,甚至使用位于几公里外的量子计算机。考虑到这一应用,我们正在与布里斯托尔大学一起探索实现高效压电微波到光学传感器的可能性 136。

4. 扩大低温量子计算机规模

第二个示例应用是使用光纤与超导量子计算机之间传输数据,

旨在扩大量子比特的数量并实现有用的通用量子计算。我们目前处于“嘈杂中型量子”(NISQ)时代137——这意味着在短期和中期内,预计会有数量有限的嘈杂量子比特实现重大应用。然而,人们普遍认为,通用量子计算机将需要大约一百万个量子比特138。

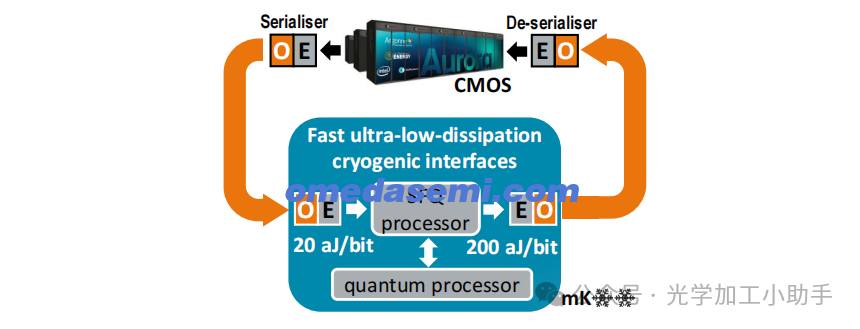

迄今为止,最先进的通用量子计算机基于超导量子比特,工作温度低于 50 mK,这是将热噪声降至最低所必需的。基于硅量子比特的高度可扩展方法也在快速发展139–143,并且也需要低温。在所有低温量子处理器中,电传输线用于传输驱动和读取低温恒温器内量子位的电信号。尽管这种方法在处理几百个量子位时是可行的,但对于数千个量子位来说,它就变得具有挑战性,而当接近一百万个量子位时,这种方法就不再可行了。事实上,电缆在带宽和热导率之间有着不利的权衡。出于这些原因,在 VTT,我们正在积极开发下一代低温量子位通信接口,使用光纤和合适的 OEC 和 EOC。超导量子技术的光学控制至少有两个截然不同的研究方向:(i) 多个 OEC 在低温下产生量子计算机的驱动信号。在这里,OEC 必须接收来自室温的光信号,该信号直接适用于驱动量子位及其门。 (ii) 一些低温 OEC 接收数字光输入信号并将其转换为数字电信号,然后驱动到超导单通量量子 (SFQ) 设备 144 中。SFQ 是一种用于经典数据的超导处理器,它还可以为量子计算机生成驱动信号,如图 13 所示。两种方法的封装密度(对于扩大规模至关重要)都可以通过集成光学技术来支持,例如用于将多个信号复用到同一光纤中的 WDM。第一种方法已经证明了量子比特的控制 145。这种方法受益于使用现有的电量子比特驱动电子设备的可能性,这些电子设备的信号在室温下通过 EOC 简单地转换为光学形式。然而,在量子计算机所需的小信号水平下,OEC 会受到散粒噪声的影响,这可能会对将其模拟信号驱动到敏感的量子计算机中造成不利影响。第二种方法对散粒噪声的容忍度明显更高,因为 OEC 只需要为 SFQ 生成数字信号,SFQ 可以根据数字输入数据生成量化模拟信号。我们的愿景遵循第二种方法,如图 13 所示,其中来自超级计算机的大量数据由合适的 EOC 序列化并通过光纤发送到低温 OEC 以驱动 SFQ 逻辑 144。将数据输入量子处理器后,SFQ 协处理器使用计算输出来驱动合适的低温 EOC,后者通过另一根光纤将结果发送到解序列化 OEC,后者与超级计算机通信。

图 13. 我们计划使用光纤链路将低温量子计算机与超级计算机连接起来的示意图。

串行器和反串行器通常是必需的,因为 SFQ 逻辑的速度通常比标准互补金属氧化物半导体 (CMOS) 电子器件的速度高得多。SFQ 是一个很有前途的选择,因为它具有超低的能量耗散,这在超导量子计算机所需的超低温下工作时是必不可少的。CMOS 电子器件也可用于低温环境,在低温环境中,低温允许较低的工作电压,从而降低功耗 146,147。Cryo-CMOS 使用针对低温操作量身定制的传统 CMOS 组件。然而,对于 CMOS 电路,很难有足够小的耗散。例如,在 3 K 下运行的仅两个自旋量子比特处理器读出和控制电路的总功耗为 330 mW148,

这已经处于现代低温恒温器容差水平的高端。此外,在低温下达到足够高的时钟速率(> 1 GHz)是一项重大挑战,如果不解决,则意味着更高的量子比特开销。低温 CMOS 技术的优势在于现有的制造基础设施和先进的设计工具和专业知识。

使用单通量量子 (SFQ) 技术可以更显著地提高能源效率。后者及其变体(如节能 SFQ)将比特表示为由超导隧道结(称为约瑟夫森结)中的切换过程产生的短(≈ 1 ps)脉冲。这些脉冲的典型能量仅为 0.2 aJ,脉冲可以以超过 100 GHz 的速度处理149

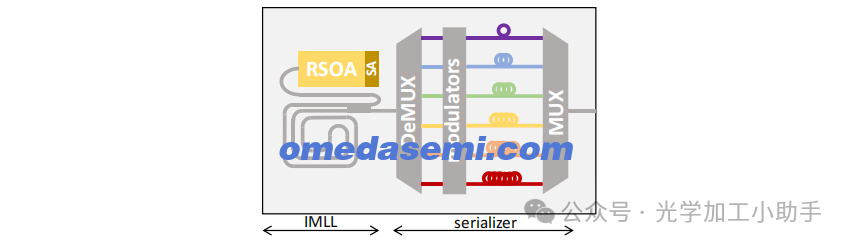

。过去,它们的使用受到低温操作要求和元件密度一般的限制。对于量子比特接口而言,这两个问题都无关紧要。基于单通量量子 (SFQ) 逻辑的超导电子器件耗散的能量不到 CMOS 电子器件耗散能量的 10,而增强型 (eSFQ 或 eRSFQ 逻辑) 甚至比 CMOS 系统耗散的能量还不到 0.1%。SFQ 控制器还可以实现极高的时钟频率,在极端情况下甚至超过 700 GHz151。凭借先进的热管理,SFQ 控制器甚至可以直接与量子比特处理器集成,从而无需非常复杂的布线解决方案。作为这一愿景的一部分,我们目前正在与合作伙伴一起为不同的构建块开发多种 PIC 解决方案。例如,在图 14 中,我们展示了如何用完全集成的 PIC 解决方案取代目前基于光纤和分立元件的原型串行器的一个长期愿景。III-V 反射半导体光放大器 (RSOA)(包括可饱和吸收器 (SA))以倒装芯片方式粘合在硅片上,并与集成、紧凑且低损耗的外部腔体耦合,以创建集成锁模激光器 (IMLL)。然后,低损耗集成解复用器分离生成的波长。每个波导中的信号最终通过幅度调制器阵列独立调制,每个幅度调制器由相对较慢的电信号(1 GHz 至 2.5 GHz)驱动。首先将生成的信号延迟适当延迟单元的倍数,最后通过波长复用器重新组合。我们目前正在开发结合延迟线和最终复用器的无源 PIC。我们将把它们作为我们已经构建的自由空间串行器原型的一部分进行测试。

图 14. 基于 PIC 的串行器的长期愿景,包括集成锁模激光器 (IMLL) 作为多波长光源。

第二个示例是我们正在使用 SNSPD 构建的低温 OEC。在这个特定的应用中,我们更感兴趣的是它们的检测速度,而不是极高的检测效率,因为我们可以承受每个脉冲使用多个光子。我们正与我们的合作者一起努力实现最终的 SNSPD 速度。一种简单的方法是使纳米线尽可能短,但实验结果清楚地表明,锁存 152–154 会成为这样做的问题。主动电猝灭也被提出,但没有显著的改进 155 。为了使 OEC 速度接近 SFQ 速度,我们还在探索不同的多路复用方法,解决 SNSPD 阵列而不是单个探测器的问题。在这种方法中,我们避免在室温下使用光串行器,而是用低温恒温器 156 内的电串行器代替它,从而导致光纤带宽的严重利用不足。最简单的强力方法是空间分割复用 (SDM),即将每个 SNSPD 与专用光纤耦合。我们确实在开发适用于探测器阵列低温照明的 2D 光纤阵列。更精细的方法是使用 WDM,与图 12(b) 中的方式相同,其中单个光纤承载多个波长。时分复用 (TDM) 也可以是一种选择,但它需要对相对较快的交换机网络进行主动控制。图 13 中视觉效果中最苛刻的部分是低温 EOC。事实上,SFQ 电子设备提供的能量和电压非常低(分别为每比特阿焦耳和微伏),因此驱动低温恒温器内的快速光调制器非常具有挑战性。尽管等离子体调制器已被证明可以在小于 1 V 的电压和阿焦耳能级 64 下工作,但使用 SFQ 驱动它们仍然不是一件容易的事,需要一些重大的开发,我们目前正在解决这些问题。

我们目前正与合作伙伴一起并行开发 SFQ 处理器以及支持 PIC 的 EOC 和 OEC,我们计划在未来几年开始测试这些不同构建块的组合,作为我们愿景的概念验证。从长远来看,这将支持芬兰量子计算机的发展,该计算机最近实现了五个量子比特的第一个里程碑157,目前的目标是到 2024 年实现 50 量子比特超导量子计算机。

同时,同样的光学接口技术也将有助于扩大我们正在共同开发的定制硅量子比特平台140,143。

5. 其他有趣的应用和结论

最后,我们简要提到,厚 SOI 技术可以支持许多其他量子技术的发展。

例如,我们刚刚与 KTH 启动了一个项目,将他们的薄铌酸锂波导 104 集成到我们的平台上。

我们还与坦佩雷大学就如何利用我们的 PIC 的多模行为和模式保存能力(见 §2.1)来支持其量子的空间整形 34–36 进行了持续讨论。我们还确定了卫星 QKD 的湍流缓解 158 是我们具有高效移相器和集成响应检测器的低损耗 PIC 的一个有前途的应用。此外,我们还与马克斯普朗克量子光学研究所进行了持续合作,将铒植入我们的硅波导中,以实现具有窄线宽的量子发射器 159。

我们介绍了厚 SOI 平台,特别关注了使其对不同量子技术具有吸引力的独特功能,我们还概述了正在进行的发展,以使其在不久的将来更具吸引力。我们提出了两个具体案例,详细阐述了我们的愿景,即基于 PIC 的解决方案将如何支持基于 DV-QKD 和 CV-QKD 的高性能 QKD 网络的大规模部署以及有用的低温量子计算机的扩展。

作者:Matteo Cherchi*, Arijit Bera, Antti Kemppinen, Jaani Nissilä, Kirsi Tappura, Marco Caputo, Lauri Lehtimäki, Janne Lehtinen, Joonas Govenius, Tomi Hassinen, Mika Prunnila, and Timo Aalto

单位:VTT – Technical Research Centre of Finland Ltd, Tietotie 3, 02150 Espoo, Finland