高量单晶碳化硅(SiC)应用广泛在电力电子领域,由于其优异的击穿电场强度和高热导率。然而,芯片制造过程中的反向研磨通常导致≈70%的单晶SiC被浪费,导致SiC芯片成本高。为了提高利用率,采用单晶SiC。多晶SiC(SoP-SiC)被键合。实现卓越粘合的挑战这种系统的界面是多晶体的非均质表面。其中,具有不同取向的颗粒通常具有不同的物理和化学特性,使其难以充分实现平滑表面以便粘合。在这里,离子束蚀刻(IBE)激活多晶和单晶SiC的表面,并实现在大气中退火后的粘结强度高(可达≈20 MPa)。亚纳米尺度电子显微镜和能谱分析表明IBE方法可以有效抑制氧化硅的形成在粘接界面处,预计这将减少界面热根据声子谱分析的电阻。本研究提供了一种制备高结合率单多晶SiC结的新方法强度和高导热性,这对SiC行业很有价值.

划重点

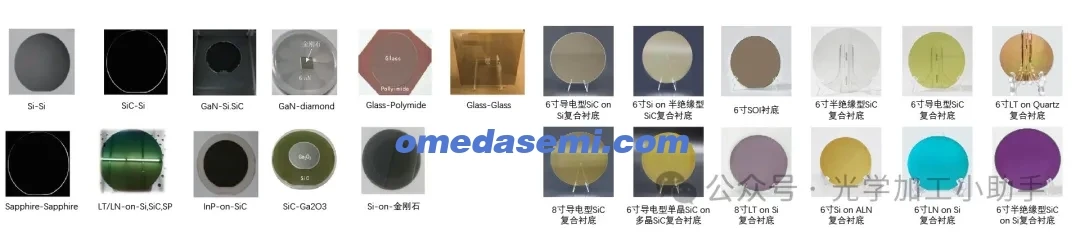

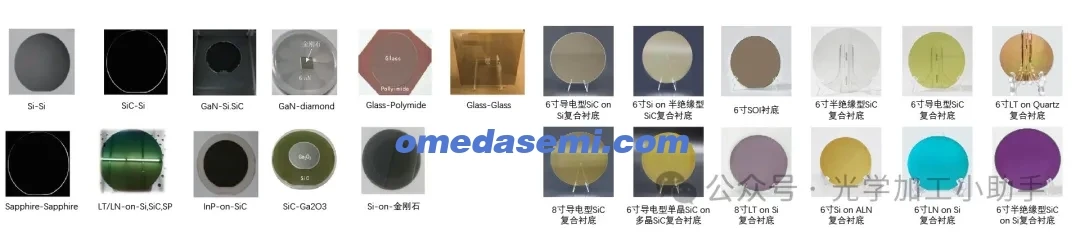

而目前国内提供绝缘体上多材料加工平台的供应严重不足,严重限制了国内科学家在这块的探索,小编为大家提供多材料(InAlAs,Inp,InGaAs,铌酸锂,晶体,碳化硅,磷化铟,砷化镓,钽酸锂,碳化硅,氮化镓,砷化镓,氮化硅,等等等等)和多材料键合加工,离子注入,抛光煎薄的全流程 全产线,自主可控复合衬底加工,您收到我们的衬底后,可以基于自己单位的平台进行后道的刻蚀工艺的开发。

同时可以提供两类工艺

键合可以亲水键合+退火或者室温表面活化键合+改性层

薄膜层的获取可以通过smartcut离子注入(厚度控制精准,膜层有损伤)+退火cmp或者机械减薄+cmp(厚度控制不精准,但是膜层没损伤)

如果想要了解更多可以联系小编

1. 简介

碳化硅 (SiC) 因其优异的性能而在许多领域中占据着关键地位。SiC 具有较宽的带隙,范围从 2.3 到 3.26 eV,具体取决于晶体取向。SiC 的高热导率和相对较低的热膨胀系数使其具有较高的击穿场强和出色的高温稳定性,使其适用于高功率应用。此外,其电子饱和漂移速度约为硅的两倍,可在高频应用中实现更快的开关速度。在微纳制造领域,SiC芯片满足了交通、通信、航空航天、消费电子等行业对大功率器件的要求[1–8]。4H SiC具有优异的晶体性能,可以制造出各种各样的器件,同时具有稳定的热特性和耐高压能力,使其在商业应用中用途广泛、成本低廉。然而,要广泛采用这些应用,一个关键问题是高质量单晶SiC晶片的成本高昂。SiC晶片通常采用物理气相输运(PVT)或其他外延生长技术生产[9,10],所需的苛刻生长条件不仅成本极高,而且限制了单晶SiC块的产量和尺寸。另一方面,昂贵的单晶SiC也造成了巨大的浪费在芯片制造过程中,通过背面研磨步骤去除晶圆背面多余的衬底材料,以降低电阻、降低功耗、提高热导率,最终提高芯片的性能和可靠性。[11,12] 在实际生产中,SiC晶圆衬底厚度通常由原来的≈375μm减小到100μm以下,即有高达≈70%的单晶SiC材料被去除而无法使用。

为了提高高质量单晶SiC的利用率,降低SiC器件的成本,高质量与低质量SiC的集成是一种有用的策略,即在制造过程中去除廉价的低质量SiC,保留昂贵的高质量SiC。过去几年取得了重大进展。例如,先前的研究已经实现了单晶 SiC 在单晶 SiC 上的键合(SoS-SiC),这些键合可以在高达 20 MPa 以上的高压[11]、1000°C 以上的高退火温度下进行[13,14],以及在去离子水中键合[15]、表面活化键合方法[14]等各种表面处理下进行。在这种情况下,顶部高质量 SiC 仍然可以作为器件的功能层,而低质量 SiC 可以在芯片制造过程中用作支撑层。这样的系统具有优异的电子性能,同时允许整体结构在后续器件制备过程的极端温度和压力下保持相当大的化学稳定性和鲁棒性[16–20],[21–23] 为 SiC 器件提供了一种经济高效的替代方案。

用多晶硅替代低质量的单晶 SiC(即在低成本的多晶 SiC 衬底上键合薄的高质量单晶 SiC,即 SoP-SiC)有望进一步降低成本。最近,Soitec 等公司已经使用 Smart Cut 方法展示了有前景的 SoP-SiC 产品。[24] 然而,他们的键合工艺假设必须在真空中进行键合,这限制了 SiC 芯片成本的进一步降低。如果可以在大气环境中实现键合,那么将大大提高时间和财务效率。 SoP-SiC 的挑战在于多晶 SiC 的晶粒取向不同,导致其表面物理化学性质不同。[25–28] 这不仅使多晶 SiC 比单晶 SiC 更难获得光滑表面,而且导致键合界面局部不均匀,键合强度降低。 此外,在 SiC 芯片制造过程中需要严格控制氧化,因为氧化层界面的存在会在有热源的工作条件下引起应力不均匀,降低芯片的稳定性和成品率。 多晶 SiC 复杂的界面条件通常含有较多的含氧杂质,这带来了新的挑战。

[29] 在本工作中,为了克服这些困难,我们采用氩离子束刻蚀 (IBE) 对多晶 SiC 表面进行处理。 IBE 中离子束的高能量是一种物理轰击形式。 IBE 蚀刻的角度相关特性可用于平滑表面粗糙度,本质上起到离子束抛光的作用,从而使多晶表面变得光滑并产生适合键合的活化悬空键。[30–32]

因此,我们利用 IBE 活化表面,然后在大气压力下退火,成功地键合了多晶和单晶 SiC。我们表征了这种键合 SiC 系统的界面结构和力学性能,发现键合界面几乎没有非晶态中间层 (<1 nm),键合强度高达 20.1 MPa。

我们还揭示了潜在的机制,即 IBE 可以有效去除 SiC 表面的污染物,降低表面粗糙度,轰击诱导辐照非晶态 SiC 的形成,后者可以在高温退火过程中转变为晶体。[33,34] 我们还将 IBE 方法与工业环境中普遍使用的等离子预处理方法进行了比较,以强调 IBE 预处理技术的优势。此外,为了阐明中间层对 SiC/SiC 系统中传热的影响,我们进行了亚纳米分辨率声子谱分析,并揭示了将中间层厚度控制在 4 纳米以内有助于提高系统的热导率。我们的工作为晶圆键合提供了一种新的表面预处理方法,能够生产出具有成本效益的高性能 SiC 晶圆。

2. 结果与讨论

2.1. 实验结果

图 1. a) SoP-SiC 实际应用说明。b) SoP-SiC 示意图和光学显微照片。c) 单晶 SiC(左)与多晶 SiC(右)键合的 SEM 图像。d) 不同退火温度下的力学性能分析。绿条表示最小值,红条表示最大值。左轴:键合强度。右轴:参考数据的键合能。[14]

图 1a 阐明了在实际应用中利用 SoP-SiC 键合系统的概念。首先,使用激光将原来约 375 μm 厚的单晶 SiC 切割成约 100 μm 厚,方法是用特定波长的会聚激光束切割和分离表面。[35,36] 允许重复使用剩余的单晶。在确认晶圆的平整度和洁净度后,对单晶 SiC 和多晶 SiC 晶圆的表面进行活化。本研究采用 IBE 进行此步骤。随后,将两个活化表面精确地面对面对齐,并施加外力以确保键合。为了进一步提高键合强度和材料稳定性,对样品进行退火处理。由此产生的键合系统有利于在单晶 SiC 侧生长器件图案层。在封装图案层进行保护后,将样品翻转,并对多晶 SiC 侧进行背面研磨减薄。重要的是,在此减薄过程中去除的大部分材料是多晶 SiC 而不是单晶 SiC,从而大大降低了总体成本。完成这些步骤后,使用标准工业程序完成芯片制造过程。在图 1b 中,该图显示了单晶 SiC(黄色)和多晶 SiC(灰色)之间的界面,右侧是使用光学镜捕获的实际样本图像。图 1c 显示了扫描电子显微镜 (SEM) 图像,显示了界面处 SoP-SiC 的紧密接近。该图像突出显示了大面积、均匀、不间断和无断裂的粘合状态。

2.2. 机械性能测试

粘合强度是评估粘合质量的关键指标,对于评估粘合的整体有效性和实用性至关重要。拉伸测试提供了一种可靠的测量粘合强度的方法。[37]

退火通常用于增强材料系统的键合强度和整体耐久性。为此,我们在大气环境中以 500、750 和 1000°C 对键合样品进行退火。图 1d 说明了使用 IBE 活化键合表征的机械性能。图的左侧面板描绘了键合强度 (𝜎)。键合强度 (𝜎) 源自使用拉伸试验机获得的键合力 (F) 除以键合面积 (A),如公式 1 所示:

然而,与由单晶 SiC 组成的键合样品不同,多晶 SiC 的不透明度对准确测量整个键合区域提出了挑战。因此,光学显微镜图像是我们评估键合强度的主要参考。绿色条表示假设整个样品区域完全键合而计算出的理论键合强度,而红色条则提供更保守的估计。红色条根据样品图像中可见气泡的存在扣除未键合区域。从该图中,我们确认键合强度随退火温度升高而增加。这一观察结果可以归因于较高温度提供的更大动能,使原子在获得更高移动性的同时,能够在界面处形成更紧密的键。因此,观察到的键合强度的增加与高温条件在逻辑上是一致的。图 1d 的右侧显示了相应的键合能数据,这些数据是使用基于该方法的经验转换公式精确计算得出的。[14]

这种键合能转换可以有效评估制备的样品是否满足实际使用要求。通常,如果键合能超过 1 J/m2,键合晶圆样品可以承受晶圆减薄和随后的工艺应力。[38] 如图所示,在 500°C 下退火的样品的键合能略低于规定标准。相比之下,在 750 和 1000°C 下退火的样品的键合能超过 1 J m-2,表明其机械性能足以承受芯片制造工艺。

2.3. 原子结构表征

为了系统地分析键合中观察到的机械性能差异,必须仔细研究界面的影响。键合界面的属性(包括原子结构、化学成分以及缺陷或杂质的存在)决定了键合的整体强度和耐久性。这些界面特性的变化会显著影响机械性能参数,例如粘附强度、断裂韧性和热稳定性。因此,全面表征界面对于理解和解决这些机械性能差异的根本原因至关重要。

图 2. IBE 激活的键合界面的 STEM 图像。a、b) 在大气中以 750°C 退火的键合 SoP-SiC 界面。c、d) 在大气中以 1000°C 退火的键合SoP─SiC 界面。e) 在真空条件下直接键合 SoS─SiC。

图 2 展示了扫描透射电子显微镜 (STEM) 原子图像,描绘了在不同条件下制备的键合样品,主要关注 SoP-SiC 之间的键合。此外,为了进行比较分析,图 2e 说明了 SoS-SiC 的直接键合。

在图 2a、b 中,样品是通过使用 IBE 激活表面,然后在 750°C 下退火来制备的。图 2a 显示了微观尺度上均匀连续的键合界面,顶部为单晶 SiC,底部为多晶 SiC。界面没有间隙或裂缝,呈现出均匀而笔直的键合线。图 2b 显示了纳米级的原子图像,清楚地说明了两种材料之间存在约 2 纳米厚的非晶过渡层。为了直接表征晶体结构,我们在右侧展示了快速傅里叶变换 (FFT) 图像。这些图像显示了样品顶部和底部位置的单晶状态,直观地表示了各个晶片的晶区轴取向并提供中间层的晶格信息。FFT 图像中非晶环的出现明确证实了材料之间存在非晶过渡层。

在图 2c、d 中,样品也是通过使用 IBE 活化表面,然后在 1000 °C 下退火来制备的。IBE参数保持一致。图 2c 显示键合界面在微观尺度上保持良好键合,单晶 SiC 在顶部,多晶 SiC 在底部。即使在高温下,界面也没有出现断裂。图 2d 提供了界面结构的详细原子尺度表征。图像显示几乎没有非晶过渡层,表明界面结合得非常好。为了进一步确认不存在中间层,我们在右侧展示了 FFT 图像,这些图像清楚地描绘了两个晶片的晶区轴取向。值得注意的是,FFT 分析揭示了中间层中的单晶结构,过渡特性最小,证实了在高温退火条件下实现 SoP-SiC 之间近乎完美的键合界面的可行性。

为了进行比较,我们在图 2e 中展示了 SoS-SiC 之间的键合。该图清楚地显示了没有任何过渡层。与图 2d 不同,由于多晶的随机取向,图 2e 中的晶体取向差异很小,而 SoS─SiC 键合中观察到的轻微错位则相反。比较图 2d、e,这种比较强调了我们的键合方法可以实现 SoP─SiC 之间的中间层质量,与 SoS─SiC 的直接键合相当。这有效地解决了中间层的存在并实现了完美的直接键合

2.4 IBE 与等离子活化的比较

在半导体工业中,等离子表面活化法更常用于晶圆键合,主要用于硅基材料集成。[39–43] 然而,这种方法有固有的局限性,例如其能量不足以激活化学稳定或较硬的材料,并且对表面平整度有严格的要求,同时可能形成厚的氧化层。对于需要高效散热的器件,额外的氧化层会对键合质量和热导率产生不利影响。此外,不均匀的氧化层会影响器件的产量、性能和寿命。[44,45] 为了缓解这些挑战,我们研究了 IBE 预处理方法。利用 IBE 旨在增强 SiC 表面的活化,最大限度地减少氧化层的形成,从而提高键合界面的机械性能和热导率。通过对这两种预处理方法的比较分析,我们的目标是找到一种最佳的 SoP-SiC 键合解决方案。

图 3. 键合界面的特征。a、b) 750°C 退火后 IBE 激活界面的 EDS 图像。c、d) 750°C 退火后等离子激活界面的 EDS 图像。e) IBE 引起的粗糙度变化。f) 原始、IBE 激活和等离子激活单晶 SiC 表面的 XPS 分析。g) 键合过程模型示意图。

图 3a、b、c、d 利用能量色散光谱 (EDS) 分析定性和定量表征用 IBE 和等离子表面活化方法预处理的样品的键合界面,然后在 750°C 的大气中退火。图 3a、b 描绘了用 IBE 预处理的样品的结果,显示中间层厚度约为 2 纳米。该层中的氧元素明显增加,而碳和硅元素则减少。这表明 IBE 预处理后形成的中间层含有少量的非晶态二氧化硅,总体氧含量相对较低。相比之下,图 3c、d 展示了通过等离子预处理制备的 SoP─SiC 样品的 EDS 分析结果。这些图表明中间层明显变厚,约为 150 nm,同时氧含量也大幅增加。这意味着等离子预处理后形成的中间层更厚,主要由二氧化硅组成。

在图 3e 中,我们展示了不同 IBE 处理时间下单晶和多晶 SiC 的粗糙度变化。红线代表单晶 SiC,可以观察到随着轰击时间的增加,表面变得更光滑,曲线的斜率逐渐变平。黑线代表多晶 SiC,曲线显示轰击约 2 分钟后粗糙度略有增加,随后下降。与单晶 SiC 不同,我们推测多晶 SiC 可能更难清洁。在初始 IBE 过程中,多晶 SiC 可能会经历表面清洁,达到阈值后,进一步的处理会影响现在清洁的表面,产生悬空键。为了进一步研究两种预处理方法对表面特性的影响,进行了 X 射线光电子能谱 (XPS) 分析,如图 3f 所示。分析重点是收集 Si2p 和 C1s 元素特有的单晶 SiC 信号,因为多晶 SiC 的成分不一致,因此未进行测试。在图 3f 的顶部,代表原始单晶 SiC,我们看到除了简单的表面清洁外,在测试前没有执行任何活化步骤。在 Si2p 光谱中,表面上明显存在大量 SiOxCy 键[46],我们将其归因于碳化硅固有的氧化性质。[47,48] 类似地,原始表面的 C1s 光谱也显示了大量 SiOxCy。在图 3f 的中间,显示了用 IBE 处理的样品。与原始表面相比,Si 2p 光谱显示 SiOxCy 显著减少,Si─C 键显著加宽。这种加宽可能表明在 IBE 处理过程中形成了非晶硅。[49] 虽然 IBE 处理过的表面表现出最小的氧化,但在活化过程中,SiOxCy 中氧元素的存在不能完全排除。此外,C 1s 光谱显示 sp3 C─C 键显著增加,[50] 这表明在活化过程中也可能形成大量非晶碳。

相反,在图 3f 的底部,等离子处理过的表面显示出 SiOxCy 键大量转化为 SiO2,[51] 表明等离子活化后产生了羟基。[52,53] 在 Si 2p 光谱中,可以清楚地观察到这种转化。此外,在 C 1s 光谱中,还检测到了大量无定形碳。然而,与 IBE 处理的样品不同,在等离子处理的样品中没有观察到 Si─C 键的明显增宽。这种差异可能是由于处理过程中等离子团簇引起的化学改性,使表面具有亲水性并影响其在退火过程中与大气水分的相互作用。这种亲水性导致氧化层厚度随时间增加。在图 3g 中,基于实验数据和文献参考[54],我们提出了一个模型来解释 IBE 和等离子体活化方法影响 SiC 键合界面结构的机制。原始单晶 SiC 表面主要由 SiOxCy 键组成。经过 IBE 预处理后,由于物理轰击,表面性质变化很小,但仍有相当数量的非晶硅和非晶碳残留。在加热和退火后,这些非晶态材料可有助于在 SiC 键合界面形成薄氧化层。相反,等离子体预处理增强了表面亲水性并产生大量羟基。结合大气退火的影响,这导致现有氧化层变厚。因此,我们得出结论,IBE 预处理可能更有效地减少 SiC 键合界面处二氧化硅的形成。此外,我们在图 S5(支持信息)中比较了这两种方法的机械性能。

2.5. 界面 SiOx 对声子谱的影响

对于硅基同质结系统,键合过程中形成的含氧中间层在填充界面间隙方面起着至关重要的作用。[55] 然而,SiOx 的存在破坏了 SiC 的连续性,成为界面热导率的障碍。[56,57] 声子作为晶格振动的量子,负责半导体和绝缘体中的热传输。声子在界面上的传播在很大程度上取决于态密度 (DOS) 的重叠和声子模式的匹配。[58] SiO 中间层的声子模式与两侧的 SiC 声子模式明显不同,对原本一致的 SiC 声子模式造成了重大障碍。这种势垒的范围与夹层的厚度密切相关。

图 4. 跨界面声子的亚纳米测量。a) SoS-SiC 键合样品的界面声子表征。上图为声子强度映射,蓝线代表强度值,中间为相应的 HAADF 图像,

下图为声子的线轮廓映射。白线的值(重叠因子)表示此处两个相邻声子光谱的重叠程度。b–d) SoP─SiC 键合样品的相应结果。e–h) 相应的声子光谱和提取的层间模式。橙色和绿色实线代表块体 SiC 的两侧,而红色实线代表 SiO 层间。黑色实线(Diff)表示残余光谱,即从层间光谱中减去块体 SiC 光谱成分后的纯层间振动模式。

在图4a、b、c、d中,我们研究了四个具有不同厚度SiO夹层的横截面样品的声子态密度(DOS),并研究了夹层内SiC声子模式的变化。我们从SiC和夹层的两侧提取特征光谱,如图4e、f、g、h所示,并对它们的强度进行定量比较。图4a示出了SoS─SiC的界面,其中几乎没有夹层。在界面处,声子DOS的重叠因子没有衰减,表明两侧SiC的声子模式在界面上完全匹配。请注意,两侧声子强度的差异是由于两侧SiC区域轴不一致造成的。图 4b、c、d 中所示的其他样品是通过退火 SoP─SiC 获得的。图 4b、c 分别显示了层间厚度为 2 和 4 nm 的样品。与原子级 SiC 键合的情况不同,在界面处声子模式是连续的,只有一部分 SiC 声子模式仍然连接到层间 SiC 的两侧。然而,随着层间厚度的增加,这种连接逐渐减弱,从层间光谱中提取的 SiC 成分减少,纯 SiO 层间模式增强就是明证。图 4d 描绘了厚度约为 10 nm 的 SoP─SiC 层,充分展示了 SiO 的声子振动光谱。在这种层间厚度下,两侧的 SiC 声子模式在层间完全断开,声子 DOS 的重叠因子在 SiC─SIO 界面处显著降低。此时,SiC─SiC界面系统应视为SiC─SiO─SiC双界面系统,因为从声子传输角度看,较厚的SiO夹层完全隔绝了SiC声子的直接传输,因此应存在一个临界的夹层厚度值,一旦SiO夹层厚度超过此临界值,就会形成两个异质结界面,如图4d的情况,由于声子需要通过界面声子桥进行非弹性散射,导致声子失配,界面热阻较大[59] 穿过界面。但当层间厚度低于临界值时,SiC 声子模的离域效应可以在层间建立连通,显著提高热导率,如图 4a、b、c 中的情形。因此,控制层间厚度低于临界厚度值将显著提高 SiC/SiC 键合体系的热导率。显然,这个临界厚度值是由两侧 SiC 声子的 DOS 是否重叠决定的,与 SiC 声子的离域程度密切相关。我们的实验结果表明它的值在 4 到 10 nm 之间。参考文献 [60] 指出 SiC 中单个堆垛层错产生的局域声子的空间宽度为 6.8 nm,落在我们给出的 4–10 nm 范围内,进一步验证了分析的合理性。鉴于 SiC 在高功率和高频电子设备中的广泛应用,IBE 表面活化技术因其能够获得更薄的中间层而显得尤为重要。该工艺有效地增强了键合界面的热导率,从而有助于实现器件的最佳性能。图 S6(支持信息)提供了有关中间层厚度影响的更多模拟数据。

3. 结论

在本研究中,我们成功地在大气中使用离子束蚀刻 (IBE) 通过表面活化实现了 SoP─SiC 的键合。IBE 的高能离子束,加上其蚀刻角度依赖性,使我们能够获得更光滑的多晶表面,并激活表面以进行键合。此外,我们分析了潜在的机制。IBE 通过物理轰击有效去除表面污染物和氧化物,并诱导非晶 Si─C层和 C─C 层的形成。在足够温度(1000°C)退火期间,该非晶层转变为晶体,导致界面处形成键合而没有任何非晶层,键合强度高达 20.1 MPa。此外,我们观察到多晶体不会因高温退火而发生任何变化。此外,为了阐明中间层对 SiC/SiC 系统中传热的影响,声子谱分析表明,将非晶层厚度控制在 4nm 以内可以显著提高热导率。本研究为晶圆键合提供了一种新的表面预处理方法,能够生产出具有成本效益和高性能的 SoP-SiC。

4. 实验部分

样品准备:单晶 SiC 样品取自 4 英寸、

<11–20>、4° 离轴 4H-SiC 晶片,厚度约为 375 μm。多晶 SiC 样品取自无压烧结 SiC,厚度为 2 mm。单晶 SiC 和多晶 SiC 样品均被切成小块,大小约为 10 × 10 mm 和 8 × 8 mm。在粘合过程之前,表面依次用丙酮、乙醇和去离子水进行细致清洁,以确保表面没有受到污染。图 S1(支持信息)中展示了单晶 SiC 和多晶 SiC 的详细 XRD 和拉曼光谱。

键合工艺:IBE活化法:首先,将需要活化的单晶SiC和多晶SiC芯片的表面朝上粘贴在同一胶带上,然后固定在IBE样品台上,如图S2(支持信息)所示。IBE工艺使用Ar离子束活化晶圆,加速电压设置为1kV,电流设置为100mA,同时保持蚀刻室中的真空度为5×10−4。离子束以10°的角度指向,并在样品台旋转的情况下施加3分钟。在图S3(支持信息)中,SRIM模拟用于确定不同角度下的最佳效率。表面活化后,立即通过折叠胶带将两个活化表面压在一起,并放置在压力约为14.5MPa的加压模具中,同时在空气气氛中进行热退火10小时。退火温度分别为 500、750 和 1000 °C。图 S4(支持信息)显示了使用 IBE 方法的不同厚度的单晶 SiC 与多晶 SiC 键合样品。

键合工艺:等离子激活法:等离子功率设置为 300W,Ar 气流量为 35 sccm。等离子激活持续 3 分钟。其余设置与 IBE 激活法一致。

特性:使用 IBE 机(IBE-100,Advancedmems)和等离子机(PDC-MG,成都明恒科技发展有限公司)激活碳化硅表面。之后,使用拉伸测试设备(HP1000,乐清市汉德派仪器有限公司)测量退火后的键合强度。采用X射线光电子能谱(Axis Ultra, Kratos Analytical Ltd.)分析IBE和等离子体活化前后SiC表面的原始状态。采用原子力显微镜(DimensionIcon, BRUKER)评估SiC表面粗糙度的变化。为了观察键合界面,首先使用聚焦离子束(Helios

G4 UX, Thermo Fisher)制备显微镜样品,同时在同一设备中使用扫描电子显微镜(SEM)进行大面积表征。采用扫描透射电子显微镜(Titan Cubed Themis G2 300, FEI)表征界面原子结构,并辅以能量色散X射线能谱(EDS)。此外,还在电子显微镜 (U-HERMES200,Nion) 上进行了电子能量损失谱 (EELS) 实验。

作者:Szuyu Huang, Fachen Liu, Jiaxin Liu, Xiaoyue Gao, Zhenzhong Wang,* and Peng Gao*

单位:Electron Microscopy Laboratory School of Physics Peking University