基于Si的异质和单体3D集成InGaAs HEMT的制作

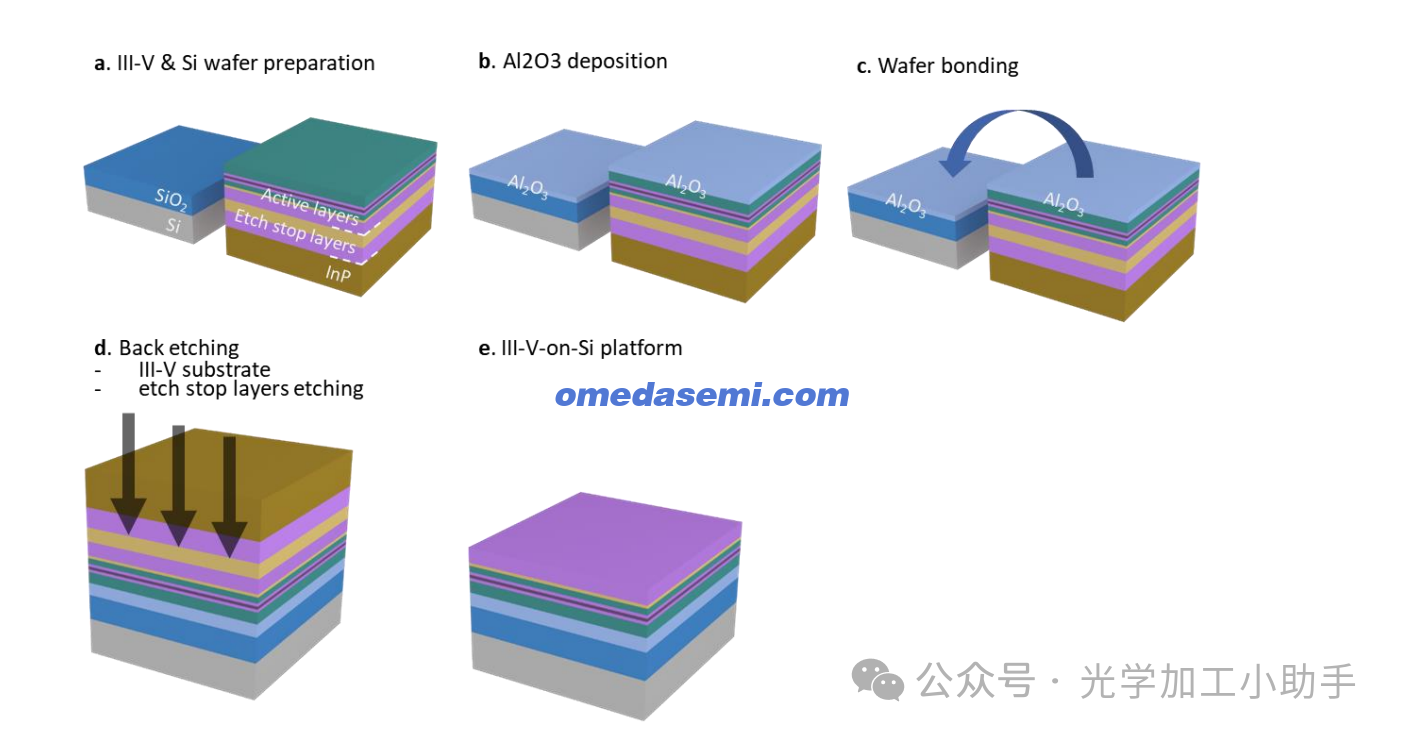

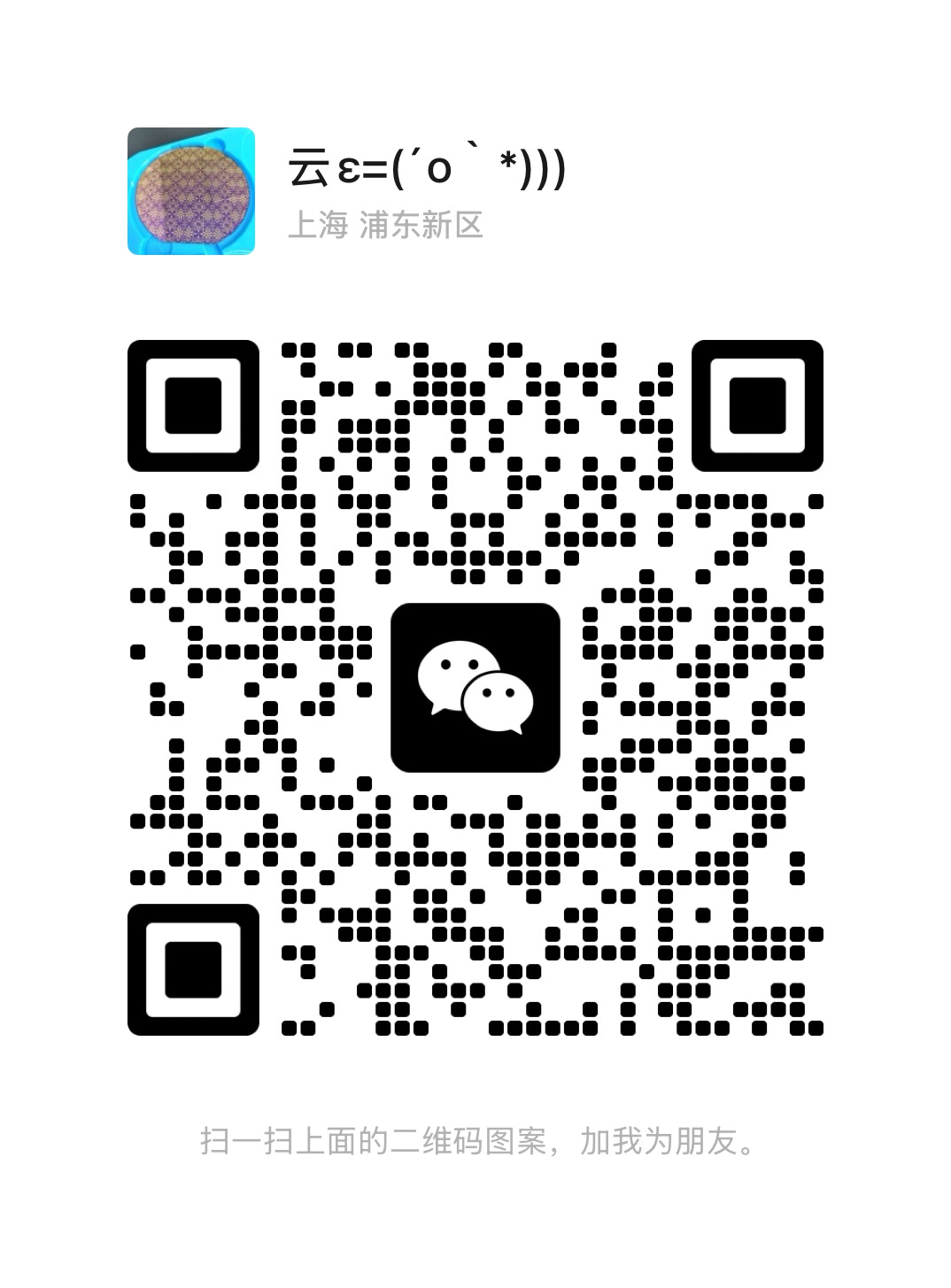

III-V-on-Si平台。a–e,使用直接晶圆键合技术的III-V-on-Si平台制作工艺流程

该工艺从III-V在Si晶圆上的制作开始。工艺流程的示意图见补充图1。

*片上35外延生长

*氧化铝作为中间层的表面活化键合,以及芯片对晶圆的键合 --D2W键合(本文用这个方式来实现常温键合)

同时与文章团队把氧化铝的沉积和键合分开做的区别,我们的设备是一体化的设备 ,薄膜的沉积和键合在同一个超高真空腔室内完成

*外延层衬底的去除

III-V异质结构通过分子束外延(MBE)在半绝缘InP晶圆上生长。III-V异质结构包含两种活性层,以倒序方式生长并具有刻蚀停止层。刻蚀停止层由InGaAs和InP层组成,活性层包括40nm n+-InGaAs接触层、3nm InP刻蚀停止层、9nm InAlAs障碍层(含Si δ掺杂)、InGaAs基QW通道(In0.53Ga0.47As/In0.8Ga0.2As/In0.53Ga0.47As,1/4/3nm)和30nm InAlAs背部障碍层。我们先清洗III-V晶圆和Si晶圆。清洗步骤后,在Si晶圆上沉积了2μm厚的SiO2作为介电层。

随后,将两块样品加载到250°C的原子层沉积(ALD)腔体中,沉积20nm厚的Al2O3作为连接介电层。在O2等离子体表面激活后,

通过200°C的直接晶圆键合(DWB)工艺将III-V晶圆与Si晶圆键合。最后,通过HCl和H3PO4:H2O2:H2O溶液选择性去除III-V基底和刻蚀停止层,得到基于III-V的Si晶圆。

划重点

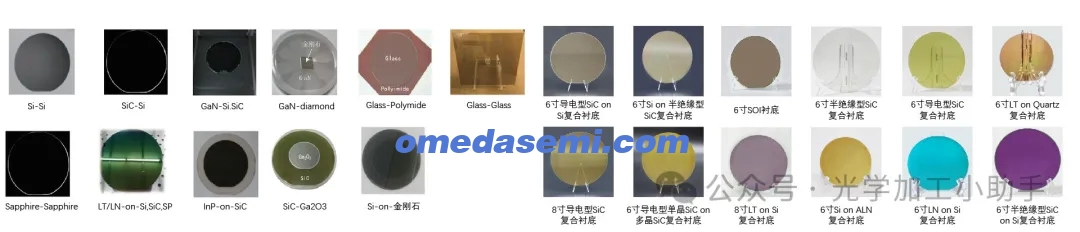

Al2O3晶圆;--紫外光波导平台

SINOI晶圆;--超低损耗氮化硅薄膜晶圆,

SICOI晶圆;用于碳化硅光子集成线路的高纯半绝缘碳化硅薄膜衬底

LTOI晶圆;铌酸锂的最有力的竞争对手,薄膜钽酸锂晶圆

LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

等离子刻蚀和划片,

EBL和6寸 150nmDUV加工微纳结构

从目前我们看到的

单材料波导平台:sicoi,lnoi,ltoi,InGaPOI,inpoi,GAASOI,TI-SAPPHIREOI(nature)

异质集成平台:sin/soi-lt/ln

三五和无源波导集成平台:inp/gaas-soi/sin/si

晶体和无源波导集成平台;Ce-Yig-OI--nature文章

上述三种平台无疑都用到了先进的键合设备,表面活化键合(键合气泡少,可用面积多)和D2W键合,同时上述两种设备技术较为先进,采购价格较贵(几百到上千万),国内很多平台,单位,学校都还没有,因此我们可以看到,欧洲和美国在光子学异质集成光子学领域创新层出不穷,同时也出现了很多基于异质集成光子学技术的初创企业,国内也有一部分异质集成光子学企业,但大多也为国外归国人才创建。

为了解决这个问题,(表面活化键合和D2W芯片对晶圆键合,尤其适用无源波导上异质集成三五族激光器)

小编为大家提供多材料(InAlAs,Inp,InGaAs,inp,gaas,铌酸锂,晶体,碳化硅,磷化铟,砷化镓,钽酸锂,碳化硅,氮化镓,砷化镓,氮化硅,等等等等)和多材料键合加工,离子注入,抛光煎薄的全流程 全产线,自主可控复合衬底加工,您收到我们的衬底后,可以基于自己单位的平台进行后道的刻蚀工艺的开发。

同时可以提供两类工艺

键合可以亲水键合+退火或者室温表面活化键合+改性层或者D2W芯片和晶圆键合

薄膜层的获取可以通过smartcut离子注入(厚度控制精准,膜层有损伤)+退火cmp或者机械减薄+cmp(厚度控制不精准,但是膜层没损伤)

三五外延衬底层的去除可以使用湿法工艺去除,基于此平台,您可以做

多材料间的异质集成创新,

如果想要获取原文,了解更多可以联系小编

摘要

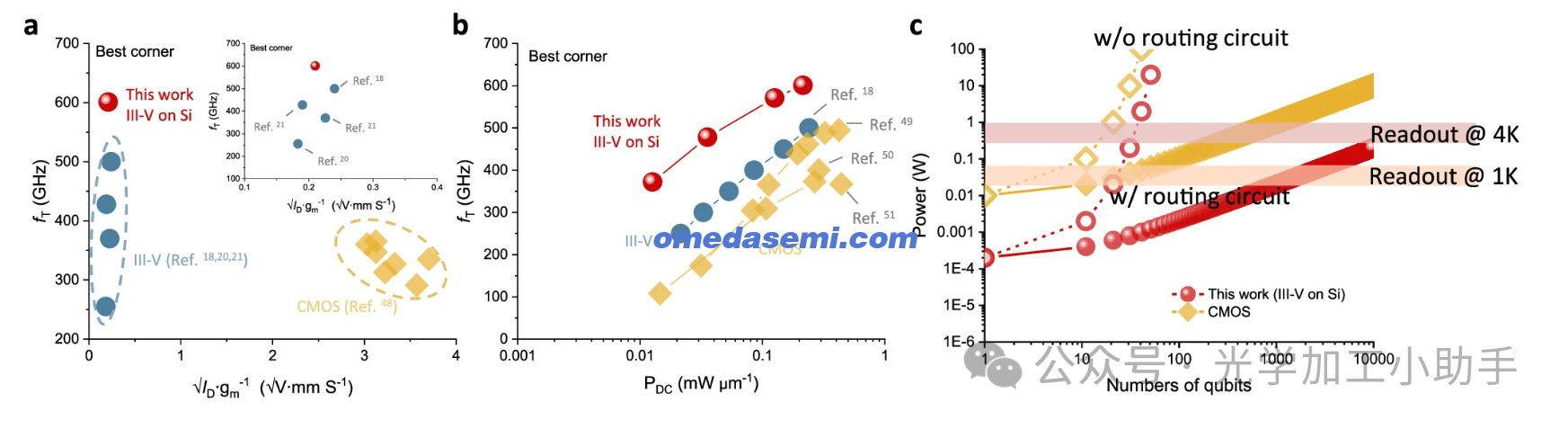

量子计算机目前面临着与经典计算相似的扩展性挑战。近期,采用硅CMOS技术制造的高保真自旋量子比特的研究成果,以及低温CMOS控制/读出电子技术能够集成在同一芯片或晶圆上的展示,提供了突破量子比特尺寸、输入输出和集成性挑战的机会。然而,基于低温CMOS的控制/读出电子技术的功耗无法支持成千上万的量子比特。在此,我们展示了基于III–V族二硅电子气和铌超导体的低温电子技术可以与硅集成,并在极低功耗下运行,从而实现对数百万量子比特的控制和读出。我们的器件在4K下具有601 GHz的单位增益截止频率、593 GHz的单位功率增益截止频率,并且比CMOS功耗低10倍以上,噪声指数也表现出显著优势。

介绍

量子计算机在某些任务中已展示出比经典计算机更强的计算能力1,2,3,4。为了实现其全部潜力并解决现实世界中的问题,量子计算机需要成为大规模系统,具备数百万到数十亿个量子比特4,5。在这一背景下,在各种物理量子比特平台中,基于硅的量子比特由于其与互补金属氧化物半导体(CMOS)技术的内在可扩展性,成为了关键平台6。如今,基于硅自旋量子比特的量子计算机由处于极低温阶段的量子比特和在常温下用于控制和读出的经典微波电子设备组成,它们通过非常长的同轴电缆连接(图1a左)。这种方法对于少量量子比特是可行的,并且有助于演示量子计算系统的概念。然而,考虑到量子比特平台需要为每个量子比特配备一个或多个控制和读出线路,与传统计算机不同,由于输入输出的困难以及长同轴电缆引起的高损耗,采用这种方法几乎不可能实现成千上万个量子比特。

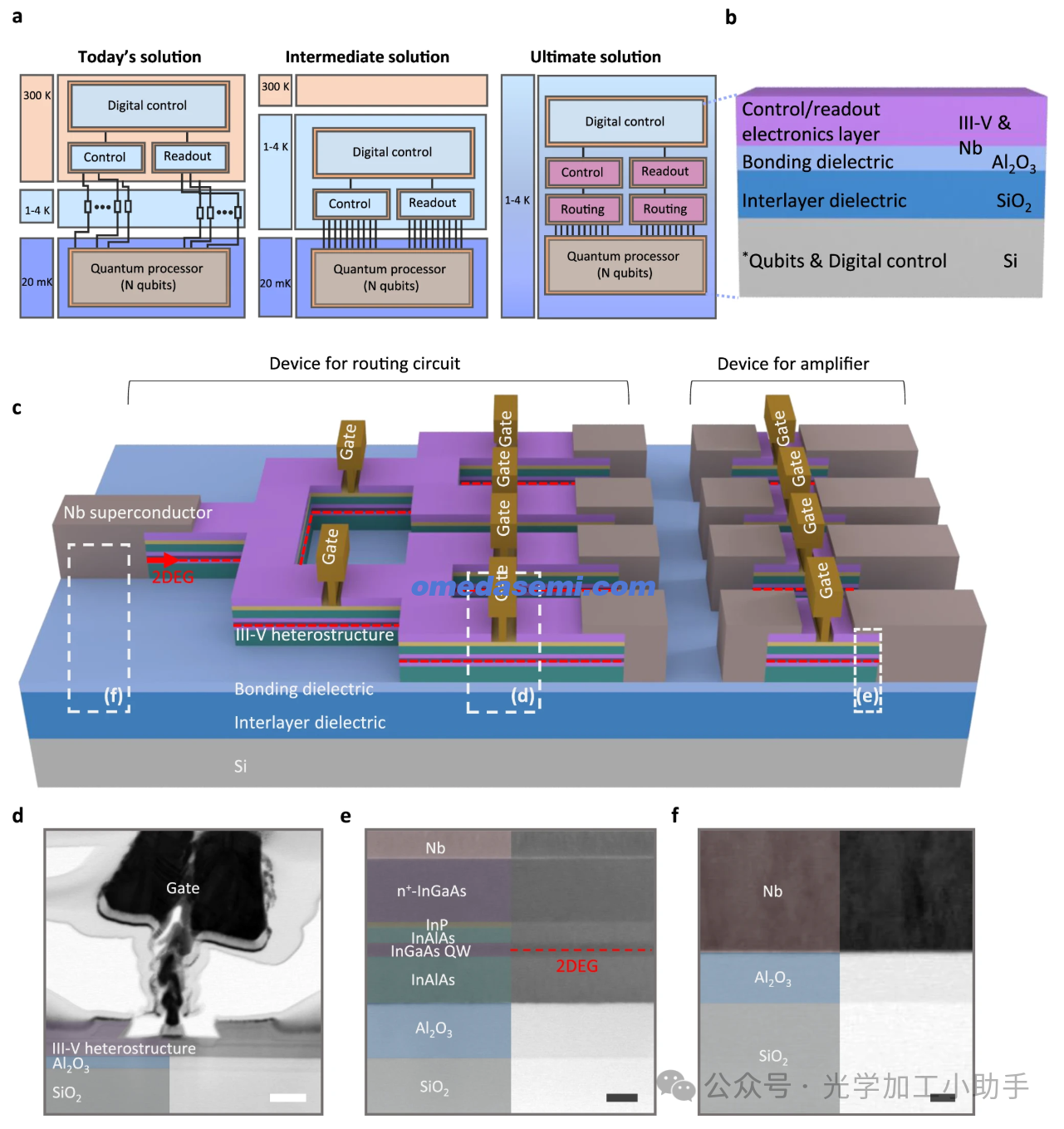

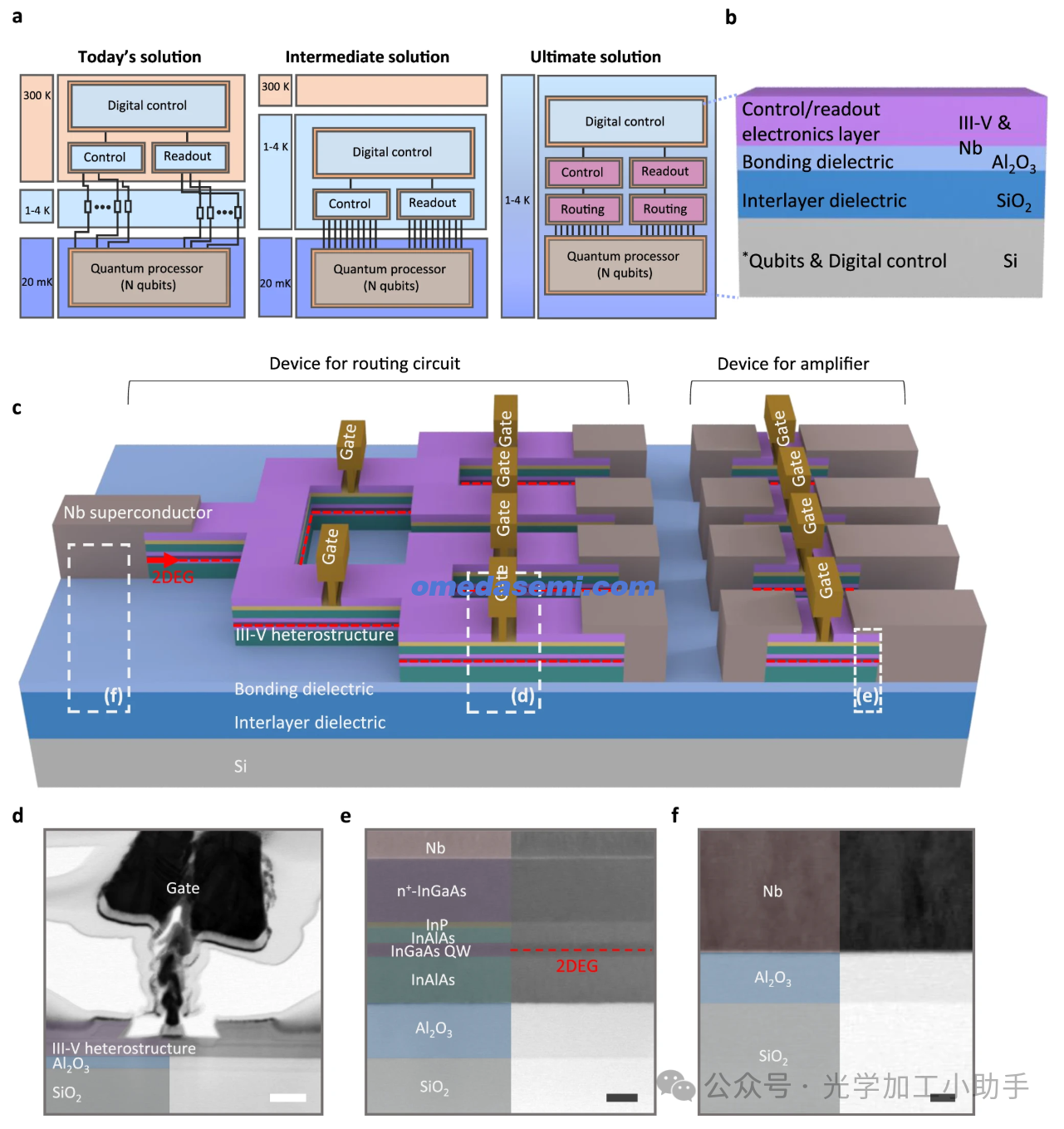

图1:基于III–V族电子器件与硅的异质和单片三维集成概念,面向大规模量子计算解决方案。

a 现代量子计算系统的特点是量子比特芯片在1 K以下工作,同时伴随常温下(300 K)运行的经典微波电子设备。这些经典微波电子设备对于控制和读出功能至关重要,它们通过长同轴电缆与量子比特连接。将控制/读出电子设备更靠近量子比特芯片有助于减少来自常温的同轴电缆数量。未来大规模量子计算系统的最终解决方案是将量子比特和低温控制/读出电子集成到同一芯片上。考虑到冷却功率的限制,对于极低功耗低温电子设备(包括路由电路和放大器)的需求变得尤为重要。

b 基于III–V族/CMOS的异质三维集成电路概念图,用于将量子比特和控制/读出电子集成到同一芯片上。尽管这项工作探索了在硅上进行三维集成,而非CMOS,但我们预计未来的研究将实现更多功能,包括与代工厂可用的基于CMOS的量子比特和数字模块的集成。

c 提议的低温设备的三维示意图,用于放大器和开关,利用基于III–V族的高迁移率二维电子气(2DEG)通道和基于Nb的超导体集成在硅上。这些射频信号放大器设备由III–V高电子迁移率晶体管与Nb超导材料组合而成,以实现高频、低噪声和低功耗操作。

d III–V异质结构的横截面STEM图像,具有T型栅极,栅长为70 nm。尺度条,100 nm。

e III–V异质结构的横截面STEM图像,Nb与硅上的Al2O3(粘接介电层)和SiO2(层间介电层)一起使用。InAlAs/InGaAs异质结与硅的δ掺杂在量子阱(QW)InGaAs层中诱导出二维电子气(2DEG),在低温下提供显著高的电子迁移率。尺度条,20 nm。

f 硅上Nb全局互连的横截面STEM图像,具有Al2O3(粘接介电层)和SiO2(层间介电层)。尺度条,20 nm。

为克服这一瓶颈,提出了将控制和读出电子设备靠近量子比特的想法,作为一种中间解决方案(图1a(中))6,7,8。最终,类似于传统计算机的发展,建议利用先进的半导体工艺,将量子比特和控制/读出电子集成到同一芯片上(图1a(右))。事实上,近期的研究集中在利用CMOS工艺将量子比特和控制/读出电子集成到同一芯片上9,10。

然而,一个关键挑战是控制和读出电子设备的功耗。量子比特只能在特定的温度范围内工作,而在这些温度下的功耗是高度受限的,这为量子计算系统带来了显著的功耗约束。由于这一问题,近年来一直在积极研究能够在更高温度下工作的量子比特11,12,13。最近,能够在4 K下工作的自旋量子比特已经被开发出来,稍微缓解了功耗的限制13。然而,要实现成千上万个量子比特,极低功耗的控制/读出电子设备是必不可少的。具体来说,要控制和读取量子比特,我们必须使用射频(RF)信号,通常是在GHz范围内。因此,控制/读出电子设备中应该使用射频晶体管,并与一个将射频信号转换和处理成数字信号的数字模块结合,形成一个单一系统(图1a(右))。然而,当使用CMOS技术时,射频信号放大所消耗的功率占总系统功耗的40,这对单独使用CMOS技术构成了重大挑战,并且是降低整个系统功耗的主要难题。

为了实现超低功耗低温射频晶体管,已经探索了几种技术,包括基于SiGe的异质结双极晶体管(HBT)15,16,17和基于InP的高电子迁移率晶体管(HEMT)18,19,20,21。SiGe HBT在与CMOS的集成能力方面具有显著优势;然而,与InP HEMT设备相比,它存在噪声水平较高和工作功率特性差等问题19。相比之下,InP HEMT在低温下展现出卓越的低噪声和低功耗特性,使其成为当代量子计算机的首选。然而,缺乏与硅集成的低温III–V技术限制了其在CMOS驱动的大规模量子计算应用中的利用。

在本文中,我们报告了利用基于III–V族的高迁移率二维电子气(2DEG)通道和基于Nb的超导体集成在硅上的高频、低噪声、低功耗低温射频晶体管和路由电路,这些内容在我们之前的研究中已有概念性介绍22。在此,我们提供了相较于先前工作的结果、分析和启示的扩展。该器件在低温下表现特别高效,最低可达4 K,此时2DEG的电阻显著下降,Nb超导体的电阻趋近于零。我们展示了该器件可以提供先进的低温性能,具体表现为在4 K下具有601 GHz的单位电流增益截止频率(fT)、593 GHz的单位功率增益截止频率(fMAX)和噪声指标( )的表现。值得注意的是,这些性能实现时的功耗比传统CMOS技术低一个数量级,并且能够无缝集成到硅上。此外,通过采用具有突破性的2DEG和Nb路由电路,我们展示了极低功耗电子设备的可行性,这使得在4 K下能够利用数千个量子比特。我们的研究为大规模量子计算系统中所需的可扩展低温控制/读出平台奠定了基础。

结果和讨论

概念与器件结构

由于冷却预算的限制,低温槽中只能提供少量的控制/读出电子设备。因此,除了放大射频信号的设备外,还需要路由设备,以便用少量的低温电子设备控制/读取大量的量子比特。图1b和1c展示了这些设备的概念和结构。III–V族异质结构和Nb超导体与硅单片集成,我们使用这些材料制造了放大器和路由电路设备。不同材料在硅基上的单片集成技术在补充图1、图2和方法部分进行了详细说明。通过使用III–V族材料与硅的片间键合技术,甚至射频电路也能实现23,24。射频信号放大器的设备由带有T型栅极的HEMT(图1d)和基于Nb的超导体(图1e)组成。在各种超导材料中,选择Nb是因为它在4K下具有超导性质,并且与III–V族材料,尤其是InGaAs,在接触电阻方面具有出色的兼容性(补充图3)。此外,Nb和InGaAs的接触预计具有优异的设备可靠性,因为其无合金化特性25,26。最近的研究已朝着在III–V材料上外延生长Nb的方向发展27,进一步扩展了其在量子计算中的应用潜力。路由电路也由III–V HEMT和Nb超导体组成,但采用了关键设计方法,即使用III–V 2DEG局部互连和Nb全局互连。III–V 2DEG用于晶体管间的连接(称为局部互连),以消除垂直传输电阻,这是低温条件下的主要瓶颈,从而实现极低的电阻和高可扩展性。此外,针对全局互连,采用Nb超导材料有效去除寄生电阻,最终实现低噪声和低功耗的运行(图1f)。

接下来的讨论详细阐述了如何通过精心设计III–V族异质结构,并引入与III–V材料兼容的Nb超导体,使得高性能低温设备的开发成为可能。这些设备在4K下运行,具备高频率、低噪声和低功耗的特点,达到的性能指标显著超越当前的技术水平。这一概念为未来大规模量子计算系统提供了一个有前景的路线。

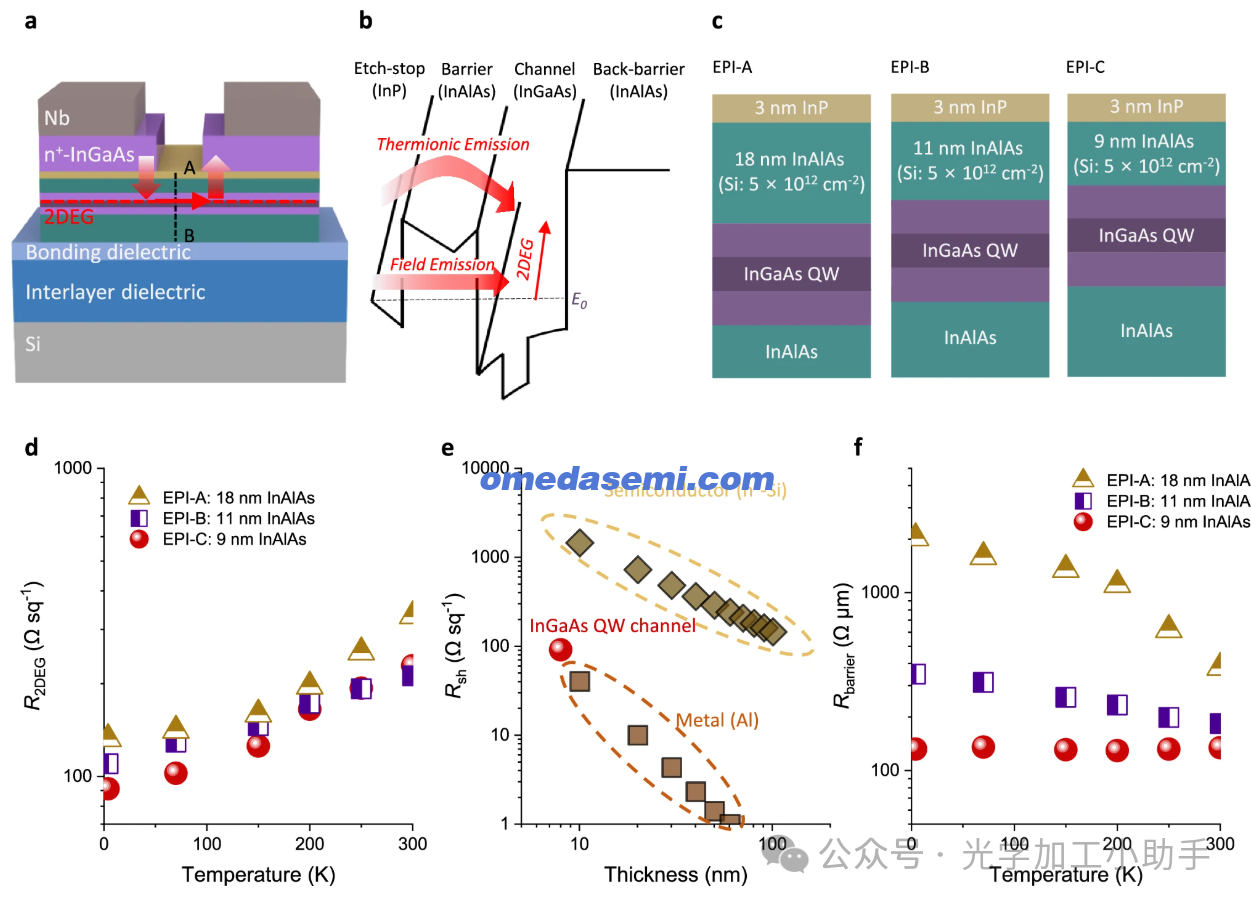

III–V族异质结构的设计与表征

III–V族异质结构必须精心设计,以实现低功耗和低噪声的低温操作。HEMT是基于多个III–V材料的异质结构建的。由于InAlAs/InGaAs异质结与Si δ掺杂的结合,在量子阱通道中形成了具有极高电子迁移率(4K下为40,000 cm² V⁻¹ s⁻¹)的二维电子气(2DEG)(图2a)。然而,在障碍层中不可避免地会形成一个垂直传输电阻成分,称为障碍电阻(Rbarrier)。这一成分在室温下占InGaAs HEMTs总电阻的很大一部分(大约60%或更多)28,29。随着环境转变为低温条件,这一成分变得更加主导,因为主要的电流输运机制由热发射转变为场发射(图2b)。值得注意的是,场发射的程度受层厚度的调节。因此,优化障碍层厚度对于最小化Rbarrier至关重要。

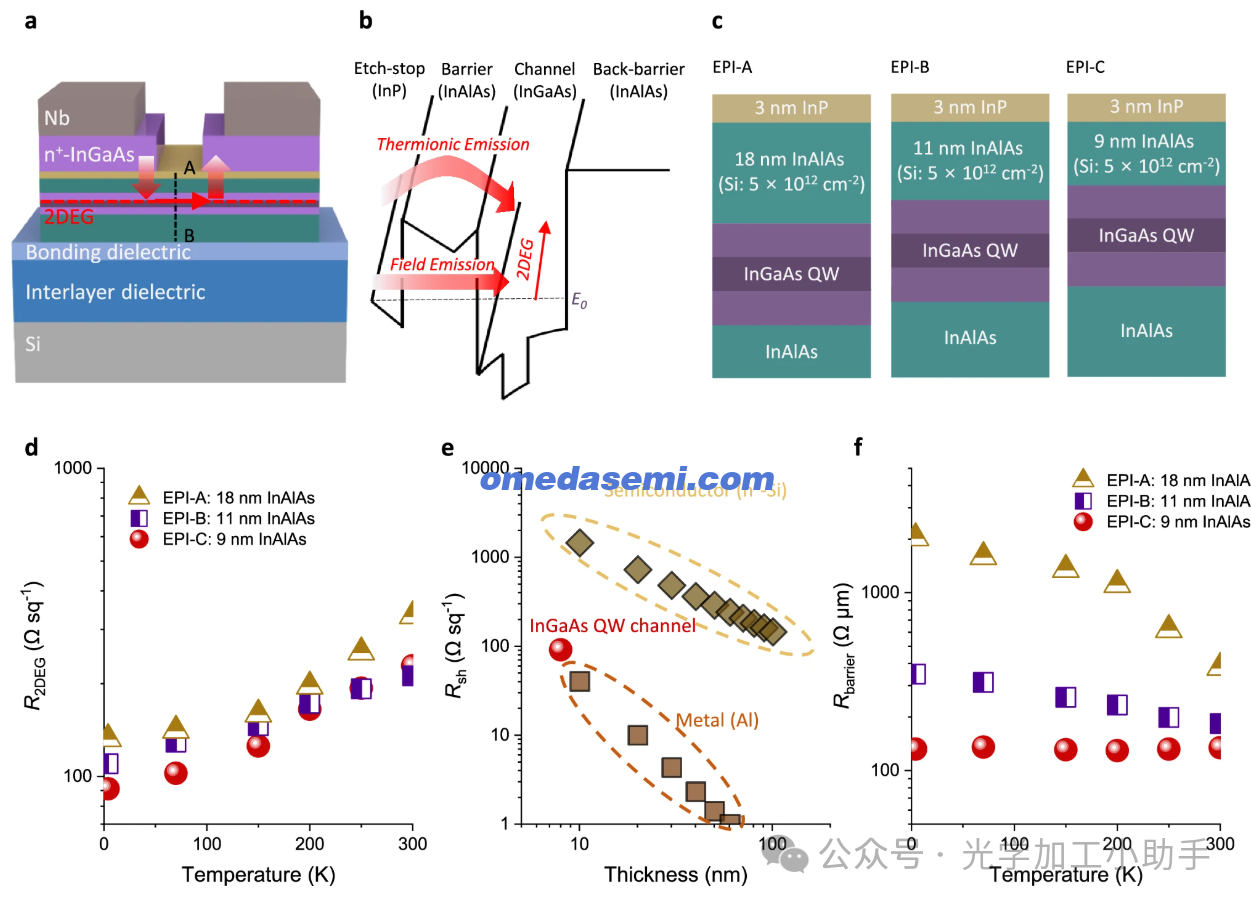

图2:低温设备用III–V族异质结构设计

a. III–V族异质结构的示意图,集成在硅基上,并采用Al₂O₃键合介质层和SiO₂中介层。

b. III–V族异质结构沿图(a)中的AB线的导带示意图。展示了两种不同的发射机制(热发射和场发射)。在低温条件下,场发射是主导机制。

c. 三种不同的III–V族异质结构,具有不同的障碍层厚度。InAlAs障碍层的厚度分别为18 nm、11 nm和9 nm,其他层保持相同。

d. 三种不同III–V族异质结构的二维电子气(2DEG)电阻率(R2DEG)随温度的变化曲线。

e. 在4K下,III–V族2DEG与常规金属(铝)和半导体(n⁺-Si)材料的电阻率(Rsh)厚度关系。III–V族2DEG的Rsh比典型的高掺杂硅低10倍以上,且与相同厚度的铝金属相当。

f. 不同III–V族异质结构中障碍电阻(Rbarrier)随温度的变化。随着温度的降低,障碍层厚度变化所引起的Rbarrier差异增加。该现象是由于低温下机制的变化,强调了低温下障碍层缩放的重要性。

III–V族异质结构的设计与特性

为了探究障碍层厚度对III–V族异质结构在低温下特性的实际影响,我们设计了障碍层厚度分别为18、11和9 nm的外延结构,同时保持其他层次相同,如图2c所示。三种不同III–V族异质结构的横截面扫描透射电子显微镜(STEM)图像见于补充图4。表征结果总结如下图2d至f所示。

我们3D集成InGaAs HEMT的二维电子气(2DEG)层的片电阻(R2DEG)在4 K时范围为91到132 Ω sq⁻¹,这略高于传统InGaAs HEMT的R2DEG(20到90 Ω sq⁻¹)20,25,30,31,主要是由于背面界面的问题,未来需要进一步研究以减小其影响。然而,4 K下91 Ω sq⁻¹的R2DEG比典型的高掺杂硅半导体小10倍以上,且与相同厚度的铝金属具有相似的片电阻。其原因是2DEG在4 K下的电子迁移率更高,从而实现了更高的频率、更低的功耗和噪声性能。

然而,图2f中的Rbarrier对比揭示了,除非能够抑制Rbarrier,否则InAlAs/InGaAs异质结构与Si δ掺杂实现的卓越导电性将无法充分发挥作用。对于未优化障碍层厚度的情况(如图2c所示的EPI-A),在4 K时,Rbarrier增至超过1000 Ω μm,相当于一个片电阻为100 Ω sq⁻¹的2DEG上10 μm长通道的电阻。这表明,InAlAs障碍层的厚度对Rbarrier有主导作用,因此在低温下,障碍层的厚度在决定整体设备电阻上发挥了关键作用。因此,为确保具有亚微米尺度的设备有效工作,Rbarrier必须降低到约100 Ω μm。具有9 nm InAlAs障碍层的III–V族异质结构表现出132 Ω μm的非常低的Rbarrier。如此低的Rbarrier可以在低温下实现高频、低噪声、低功耗的操作。在这种背景下,障碍层的厚度起着至关重要的作用。适当缩小障碍层厚度可实现更有效的场发射,从而在低温下实现低寄生电阻。然而,过度缩小障碍层厚度会导致高门漏电流并产生额外噪声,因此设计合适的障碍层厚度至关重要,本研究采用了9 nm的障碍层厚度。

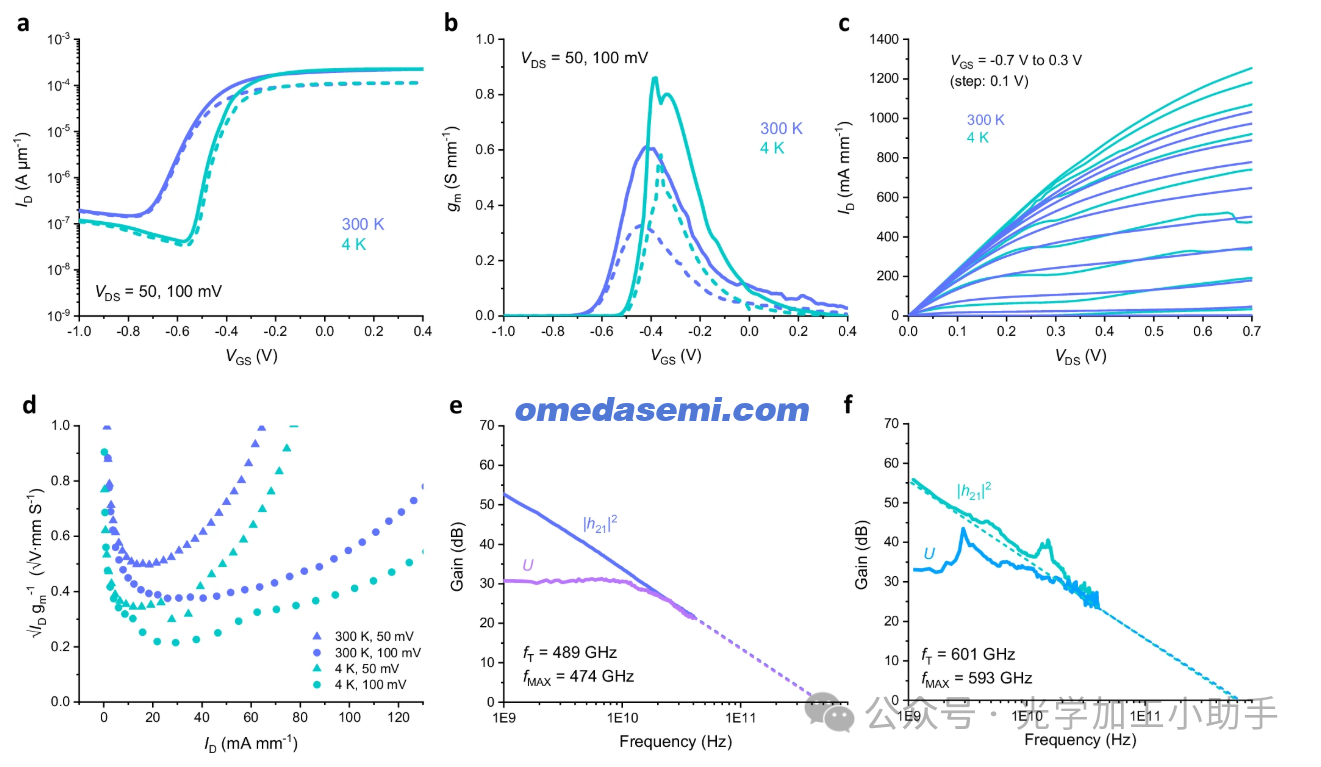

低功耗、低噪声放大器的低温设备

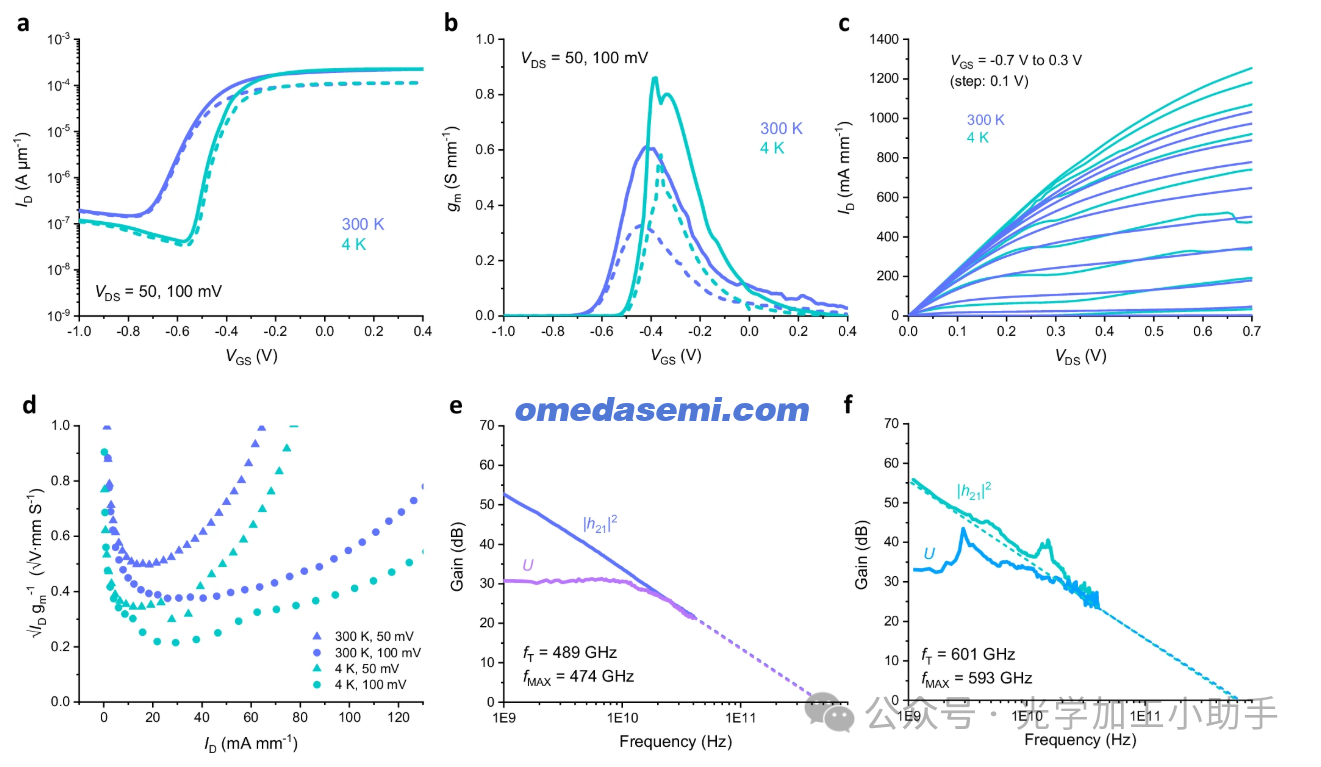

III-V HEMT与Nb超导体集成在硅上的表征分别在300 K和4 K的低温探针站中进行,详细的测量设置见于方法部分。以下报告的所有结果均针对门长LG = 70 nm的双指设备。为了进行公平比较,电流按设备的总宽度进行了归一化。图3a展示了低漏极电压(VDS)50 mV和100 mV下的转移特性。随着温度降低到低温水平,设备的亚阈值摆幅(SS)得到改善,设备的关闭电流减少,同时门漏电流也减小(见补充图6)。在4 K时,VDS = 50 mV时,最低SS为35 mV dec⁻¹,门漏电流在典型的最优低噪声操作下为10⁻⁸ A μm⁻¹,足够小,不会主导噪声性能。35 mV dec⁻¹的SS值与以前报告的低温设备相比并不特别低20,21,32,33,这归因于通道电位的波动34,35,影响了设备中的无序程度,从而影响设备的SS。该效应主要取决于通道结构34,35,因此为量子计算应用设计合适的通道结构至关重要。

图3b展示了在VDS为50 mV和100 mV时测量的跨导(gm)特性。与300 K相比,在4 K下,通过优化III-V异质结构和Nb基接触获得了显著提高的gm(0.8 S mm⁻¹),这是由于迁移率的提高和寄生电阻的降低(见补充图3、7)。在4 K下,设备的低寄生电阻和优异的迁移率特性也可以在输出特性中找到,输出特性在VGS范围为-0.7 V到0.3 V时测量(图3c),显示出在4 K时0.4 Ω mm的最优开关电阻(Ron)和1225 mA mm⁻¹的最大漏电流(在VGS为0.3 V时)。设备的低噪声潜力可以通过噪声指示因子(),这是低噪声和低功率RF应用中非常重要的指标来清晰地体现。噪声指示因子(噪声指示因子)随漏电流(ID)的变化关系见图3d。在4 K时,设备在ID为20 mA mm⁻¹时表现出0.21的低噪声指示因子。ID的范围为15–20 mA mm⁻¹,适用于最优低噪声操作,这是一个非常低的电流水平,因此适用于低功率操作。

III-V HEMT在Si上的转移特性(a)和跨导特性(b),门长(LG)为70 nm,门宽(WG)为2×20 μm,在VDS为50 mV(虚线)和100 mV(实线)下测量。测量在300 K和4 K下进行。当温度降至4 K时,设备表现出改进的转移特性,在VDS = 50 mV时SS为35 mV/dec。同时观察到正向阈值电压(VTH)的偏移。该设备在4 K下提供了更锋利的跨导特性,在低VDS(100 mV)下的峰值跨导(gm)为0.8 S/mm,相较于300 K下的测量结果有所提高。这一改善归因于2DEG迁移率的提升和寄生电阻的减少。

(c) 输出特性

同一设备的输出特性,显示出在4 K下更低的开启电阻和更高的最大电流。

(d) 噪声指示因子

在低VDS(50 mV和100 mV)下测量设备的噪声指示因子(噪声指示因子与ID的关系)。测量在300 K和4 K下进行。设备在4 K下表现出非常低的噪声指示因子(0.21),在VDS = 50 mV和100 mV时,最小噪声指示因子的PDC分别为0.8 mW/mm和2 mW/mm。

(e) 增益特性(300 K下)

在300 K下测量门长(LG)为70 nm、门宽(WG)为2×20 μm的III-V HEMT的增益特性,VDS为500 mV。增益是通过外推h21和U曲线并使用−20 dB/dec的斜率来提取fT和fMAX。

(f) 增益特性(4 K下)

在4 K下,测量了相同设备的增益特性,VDS为500 mV。通过这些测量,得到了该设备在低温下的增益特性,fT和fMAX增大,表明其具有更强的高频性能。

这些结果表明,III-V HEMT在低温下具有优异的性能,适合于低噪声、低功耗的射频应用,特别是在量子计算等低温电子学领域。

高频特性也在300 K和4 K下使用矢量网络分析(VNA)进行测试。在设备特性测试之前,进行了片上校准,以去除来自电缆和探针站的外部效应,确保测试结果的准确性。通过使用在同一衬底上制造的开路和短路测试图案,进行了接触垫的去嵌套过程,从而去除了与接触垫相关的寄生元件。随后,测量了III-V HEMT在Si上的散射(S)参数。由S参数得到的电流增益(h21)和单向功率增益(U)如图3e、f所示。该设备在300 K时表现出489 GHz的fT和474 GHz的fMAX。当温度降至4 K时,由于电子迁移率的提高和寄生电阻的降低(如直流特性分析所示),fT和fMAX显著增强,分别达到了601 GHz和593 GHz,且在低VDS(0.5 V)下测试。这些结果表明,基于Si的III-V HEMT低温射频晶体管不仅优于基于CMOS的低温射频晶体管,而且与传统的基于III-V的低温射频晶体管相比,提供了具有竞争力的性能。近期,研究人员一直在探索优化的障碍层、间隔层和通道结构,以进一步提高最先进的InGaAs HEMT低噪声放大器(LNA)在量子计算应用中的40 dB增益和1.4 K的平均噪声温度。将这些优化设计融入到本研究中,可能会使我们更接近实现大规模量子计算平台。此外,由于我们的设备集成在Si上,它打破了传统设备中低温性能与集成能力之间的权衡关系。事实上,我们的设备可以集成到低温CMOS芯片中,包括数字块或量子比特处理器,前期研究已通过III-V与CMOS技术的异质化和单片3D集成证明了这一方法的潜力。

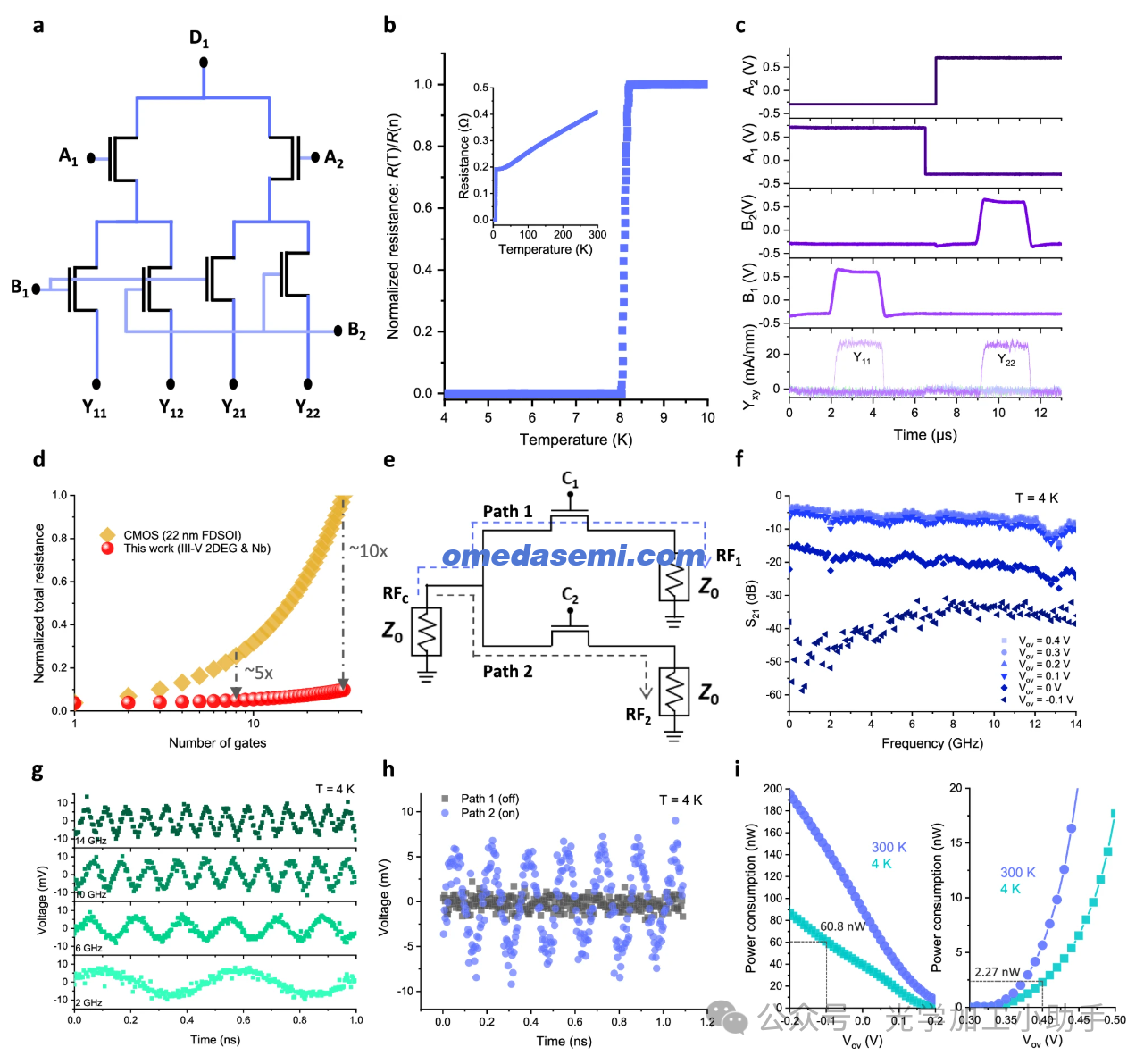

低功耗路由策略

为了在低温环境下的冷却设备预算内实现大规模量子计算系统,开发能在非常低功耗下运行的低温射频晶体管至关重要。然而,单纯地降低低温射频设备的功耗可能存在局限性。因此,针对控制和读取大量量子比特的少量低温设备,积极开发了路由电路。大规模量子计算系统的路由电路必须满足多个标准:低功耗、低噪声、低插入损耗和高隔离能力。低温路由电路已经使用各种技术,如CMOS和III-V,进行了演示。然而,传统路由电路的一个限制是其较大的垂直传输电阻。利用最先进的低温CMOS(22 nm FDSOI)的1对8路由电路的垂直传输电阻部分约为80%(见补充图8)。这意味着,垂直传输电阻在低温下是路由电路的主要瓶颈。因此,减少垂直传输电阻,或理想情况下消除垂直传输电阻,是开发高可扩展路由电路的关键。

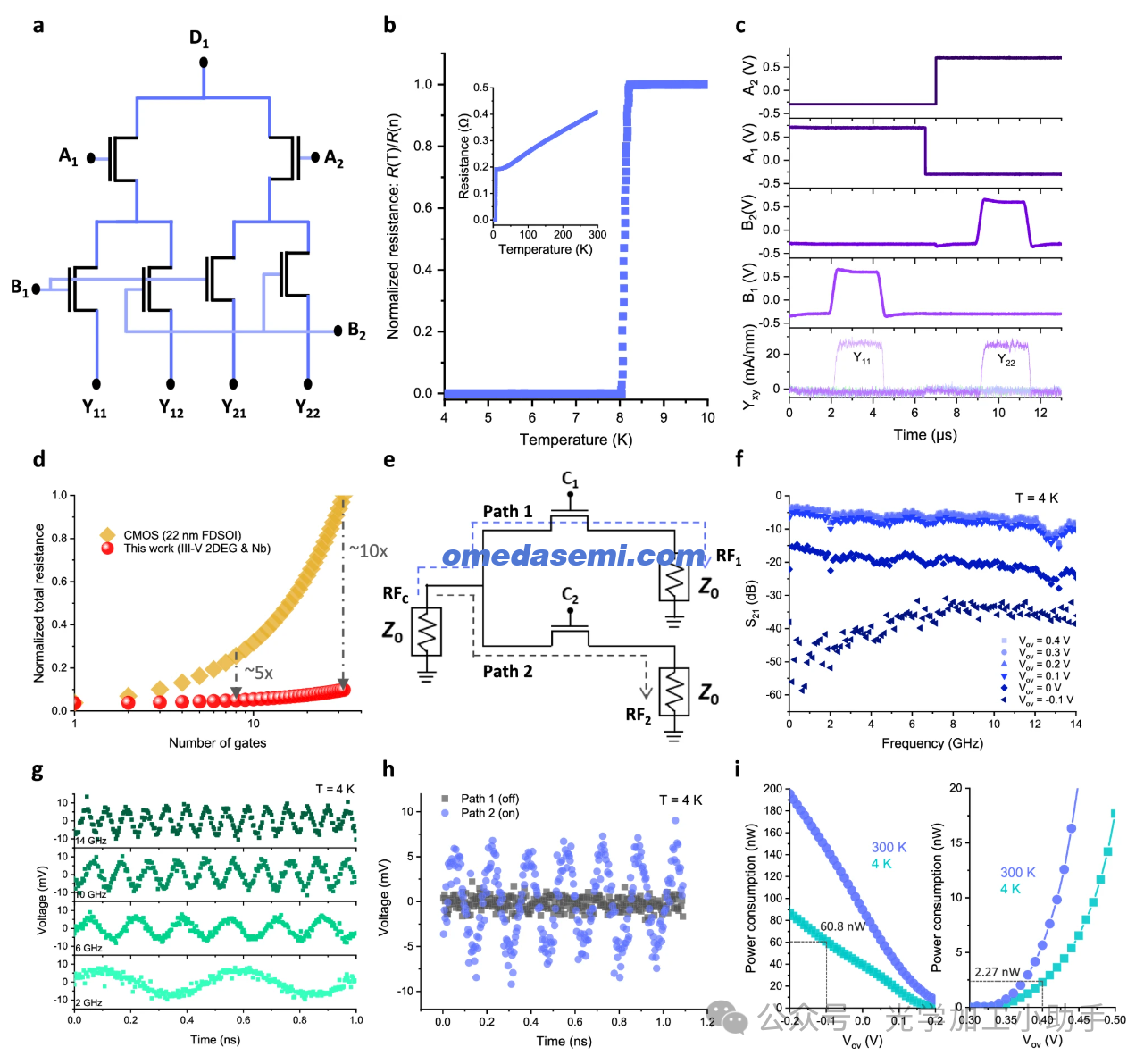

为了解决这个瓶颈,我们设计了使用III-V 2DEG本地互连和Nb超导全球互连的路由电路(见图4a)。路由电路的更详细的横截面结构可以在补充图8中找到。通过将晶体管之间的本地互连从金属替换为2DEG,能够有效消除垂直传输电阻(见补充图8)。在全球互连方面,使用Nb超导材料,以最小化电极的功耗并抑制由此产生的自加热效应。Nb的超导转变如图4b所示,发生在8 K的温度范围内。路由电路的工作温度为4 K,在此温度下,Nb全球互连保持超导状态。时间域测量如图4c所示。将常规电压应用到公共端口,开启状态电压应用到A1,关闭状态电压应用到A2,并对B1施加开启状态电压脉冲,导致电流流过相应的Y11输出。相反,将关闭状态电压应用到A1,开启状态电压应用到A2,并对B2施加开启状态电压脉冲,导致电流流过相应的Y22输出。这些结果展示了1对4直流路由中的正确路由操作。我们的方法与传统CMOS方法在相同布局下的总电阻预测值如图4d所示。用于预测的布局可以在补充图8中找到。采用2DEG本地互连和Nb全球互连的路由电路在8个门的路由中比传统结构的电阻减少约5倍,而在32个门的路由中减少幅度可达到约10倍(见图4d)。门数越多,我们的结构的效果越显著,适用于大规模量子计算系统。这一改进归因于超导全球互连的零电阻以及通过引入2DEG且通道间无金属接触显著减少的本地电阻。随着量子计算机规模的增大,该结构的影响愈加突出。因此,这一架构可能为高度可扩展的路由系统提供了一个有前景的解决方案。

图4:基于III-V的低温直流(DC)和射频(RF)路由电路在Si上的单片集成特性。

a 1对4直流路由电路示意图。共有一个输入端和四个输出端,配有四个控制门(A1、A2、B1、B2)。

b Nb的电阻与温度的关系(标准化到10 K时的电阻),显示了8 K的转变温度。插图包括了最高300 K时的电阻值。

c 不同输入电压下的输入输出波形,展示了低温路由的功能性。

d 在缩放结构下,所展示的路由电路与传统CMOS路由电路(22 nm FDSOI)相比的电阻基准。路由电路的布局可以在补充图8中找到。电阻已标准化为具有32个门的CMOS路由电路的电阻值。

e 1对2射频路由电路示意图。共有两个射频输出端(RF1和RF2)和一个公共端口(RFC)。C1和C2为控制门。

f 不同控制门Vov下的S21与频率的关系。

g 不同输入信号频率下的输出波形。

h 在路径1关闭、路径B开启的情况下,6 GHz输入信号的输出波形。

i 静态功耗与Vov的关系,分别在4 K和300 K下测量。线条表示典型工作区域,Vov范围为−0.1至0.4 V。

我们开发了不仅用于直流(DC)信号的路由电路,还开发了1对2射频(RF)信号路由电路。如图4e所示,射频信号输入到一个公共端口并分成两条路径。这些路径通过使用基于Si的III–V 2DEG进行选择性连接或隔离。通过在控制门上施加偏压,可以调节2DEG的密度,从而改变射频信号的传输特性(见图4f)。在8 GHz时,插入损耗和隔离度分别为5.1 dB和32.8 dB。开关比(S21,off - S21,on)在14 GHz以下约为25 dB,证明了该电路适用于自旋量子比特的控制(参见文献46)。如图4g和4h所示,路由电路的时域响应通过信号发生器和示波器进行演示。路由电路在2–14 GHz频率范围内几乎不受频率变化的显著影响(图4g),并展示了优秀的路由能力(图4h)。静态功耗是射频路由电路功耗的主要部分,已进行了测量(图4i)。由于在低温下门漏电流减少,开关能够以更低的静态功耗运行。在开关的工作范围内(Vov:−0.1至0.4 V),每个开关的功耗最低可达60.8 nW。

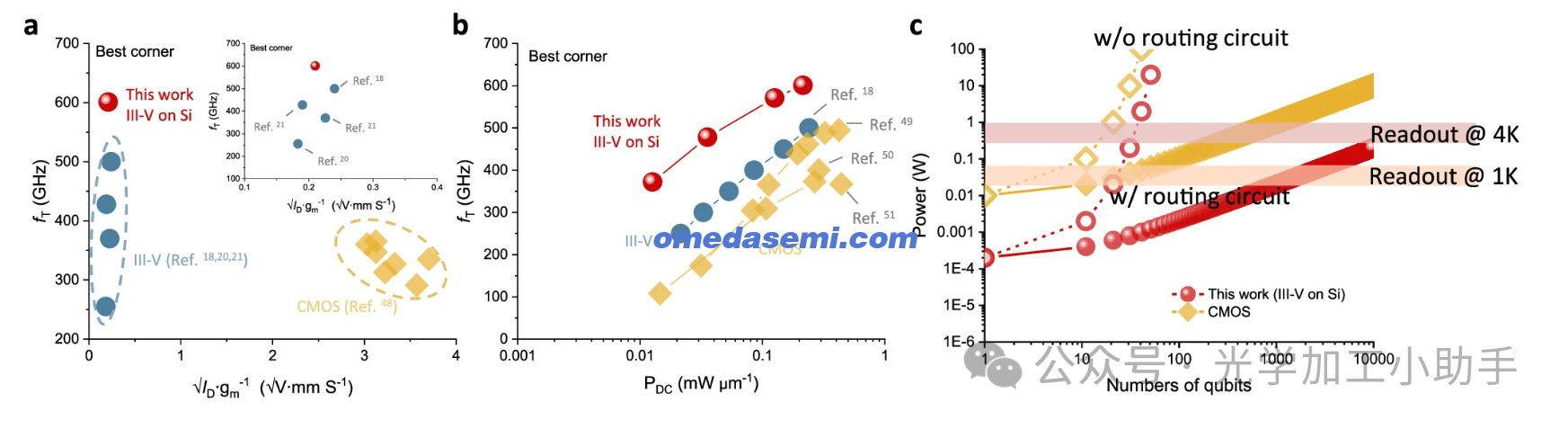

性能基准

对于用于大规模量子计算应用的低温器件,高频、低噪声和低功耗特性是非常重要的。传统低温电子器件面临的主要局限之一是高性能(高频、低噪声、低功耗)和可扩展性(集成能力和CMOS兼容性)之间的权衡。当前广泛应用于量子计算系统中的III–V HEMT基础的低温电子器件,表现出高的截止频率、低噪声和低功耗特性。然而,由于其可扩展性差且与CMOS兼容性低,它们并不被认为是未来大规模量子计算的有前景的候选者。另一方面,基于CMOS的低温器件从可扩展性的角度来看非常有效,因为CMOS技术在自旋量子比特方面的积极发展,以及CMOS可以实现量子比特控制/读出电子器件的共同集成。然而,CMOS器件的缺点是难以实现高性能。图5a和5b展示了基于III-V/Si的低温射频电子器件与文献中已有的其他方法(包括III–V和CMOS)的性能基准对比。fT和最大增益(fMAX)是在各自的最佳偏压点提取的。对于我们的器件,fT是在VDS为500 mV时提取的,fMAX是在VDS为100 mV时提取的。该基准突出了我们器件的两个主要特点。首先,我们基于III-V的器件集成在Si上,明显优于基于CMOS的低温器件。截止频率大约是后者的两倍,噪声指示因子约小15到20倍(图5a)。特别重要的是,这些优异的特性在功耗上比CMOS器件低10倍以上。其次,我们的器件不仅超越了CMOS性能,还比以前报道的III-V器件表现更为出色(参见文献18, 20, 21, 47, 48, 49, 50)。这种显著的改进可能来自两个主要因素:(1)优化的III-V异质结构,具有量子阱通道和屏障厚度,可以更有效地提高电子迁移率并减少低温下的寄生电阻;(2)基于Nb的欧姆接触有效地减少了接触电阻,这在射频器件的扩展中尤为重要,能够改善高频、低噪声和低功耗特性。当然,fT和噪声指标并不直接代表低噪声放大器(LNA电路)的增益和最小噪声水平,但显然我们的器件具有作为量子比特信号读出设备的足够潜力。在未来的研究中,需要对LNA制备后的最小噪声进行全面评估(参见文献19, 37, 38)。

图5:使用基于Si的III-V器件实现高增益和低噪声低温电子器件。

(a)fT与最大增益(fMAX)和(b)fT与最小噪声指示因子(PDC)的基准对比,展示了最先进的低温射频晶体管。fT和fMAX在各自的最佳偏压点提取,而不是在相同的偏压下。呈现的器件中,我们的器件最接近最佳角落区域(即,最高的fT和最低的噪声指示因子,以及最高的fT和最低的PDC)。插图仅展示了III-V的fT与fMAX基准。数据来源于文献18、20、21、47、48、49、50。

(c)根据门数以及是否包含路由电路,预测我们的器件和CMOS器件的功耗曲线。路由比为1:10。彩色线表示通过最先进的稀释制冷机可实现的冷却功率,假设读取时功耗为50%。

基于低温射频器件和路由电路的性能,我们估算了读取电子设备的功耗。图5c显示了我们提出的平台与仅使用CMOS平台的功耗对比,考虑了门数以及是否包含路由电路的情况下的功耗曲线。假设路由比为1:10,并且读取时功耗为50%。彩色线表示通过最先进的稀释制冷机提供的冷却功率。我们的预测结果强烈表明:虽然仅使用CMOS技术来控制和读取数千个量子比特是一个可行的方法,但要达到数万个量子比特,或更大规模,可能需要实现本研究中提出的基于III-V-on-Si技术。

我们展示了使用III-V异质结构和Nb超导材料集成在Si上的低温电子器件,用于放大GHz范围的信号和信号路由。我们器件的能力和优势来自于精心设计的III-V异质结构与引入的Nb超导材料的独特结合,从而提供了最先进的低温性能。至关重要的是,由于我们的器件是在Si晶圆上通过异质和单体3D集成方法演示的,它解决了传统III-V技术在与Si集成上的根本问题,从而为大规模量子计算系统提供了一条途径。鉴于我们的异质和单体3D集成解决方案能够在不降低性能的情况下容纳多种功能,未来可以将更多功能(例如基于CMOS的量子比特(如自旋量子比特)和控制/读取电子学(如模拟到数字转换器、数字到模拟转换器、混频器))集成到我们的方案中。

方法

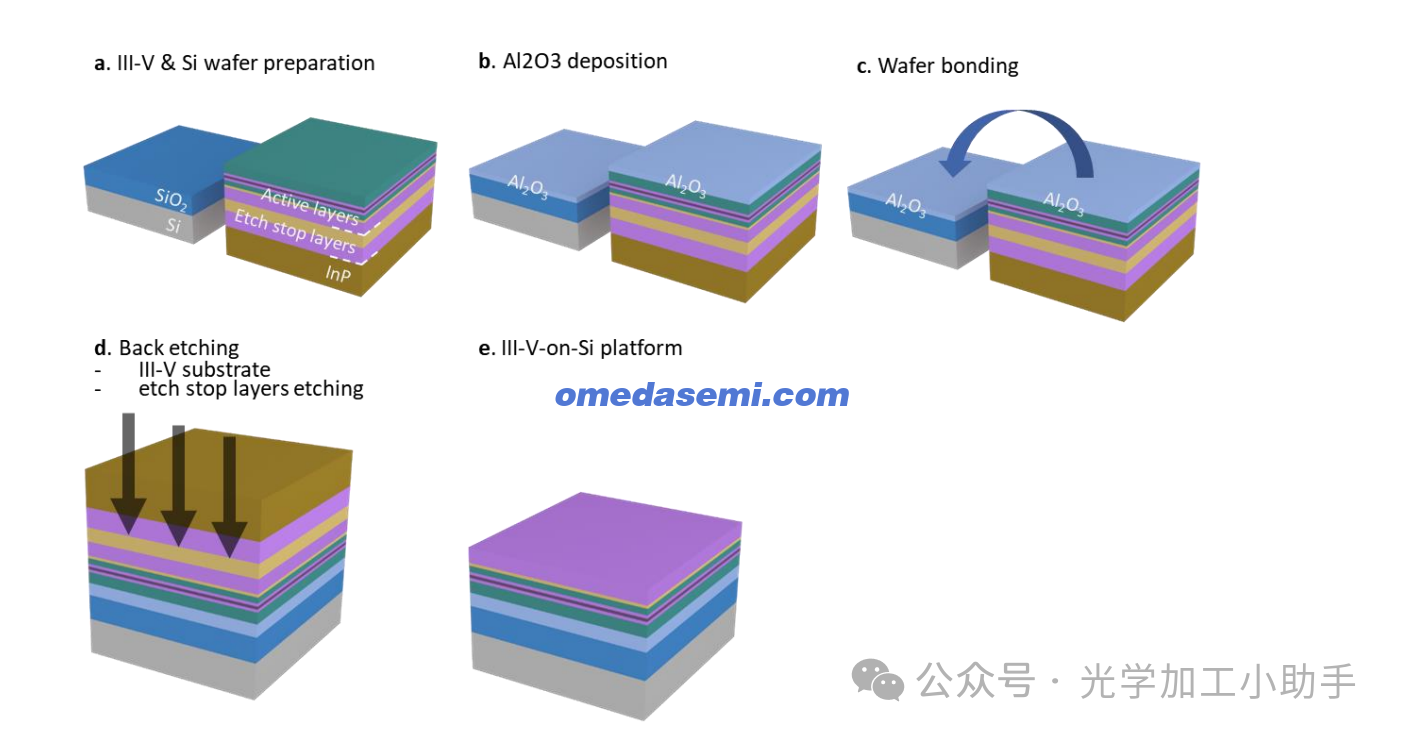

基于Si的异质和单体3D集成InGaAs HEMT的制作

该工艺从III-V在Si晶圆上的制作开始。工艺流程的示意图见补充图1。III-V异质结构通过分子束外延(MBE)在半绝缘InP晶圆上生长。III-V异质结构包含两种活性层,以倒序方式生长并具有刻蚀停止层。刻蚀停止层由InGaAs和InP层组成,活性层包括40nm n+-InGaAs接触层、3nm InP刻蚀停止层、9nm InAlAs障碍层(含Si δ掺杂)、InGaAs基QW通道(In0.53Ga0.47As/In0.8Ga0.2As/In0.53Ga0.47As,1/4/3nm)和30nm InAlAs背部障碍层。我们先清洗III-V晶圆和Si晶圆。清洗步骤后,在Si晶圆上沉积了2μm厚的SiO2作为介电层。随后,将两块样品加载到250°C的原子层沉积(ALD)腔体中,沉积20nm厚的Al2O3作为连接介电层。在O2等离子体表面激活后,通过200°C的直接晶圆键合(DWB)工艺将III-V晶圆与Si晶圆键合。最后,通过HCl和H3PO4:H2O2:H2O溶液选择性去除III-V基底和刻蚀停止层,得到基于III-V的Si晶圆。

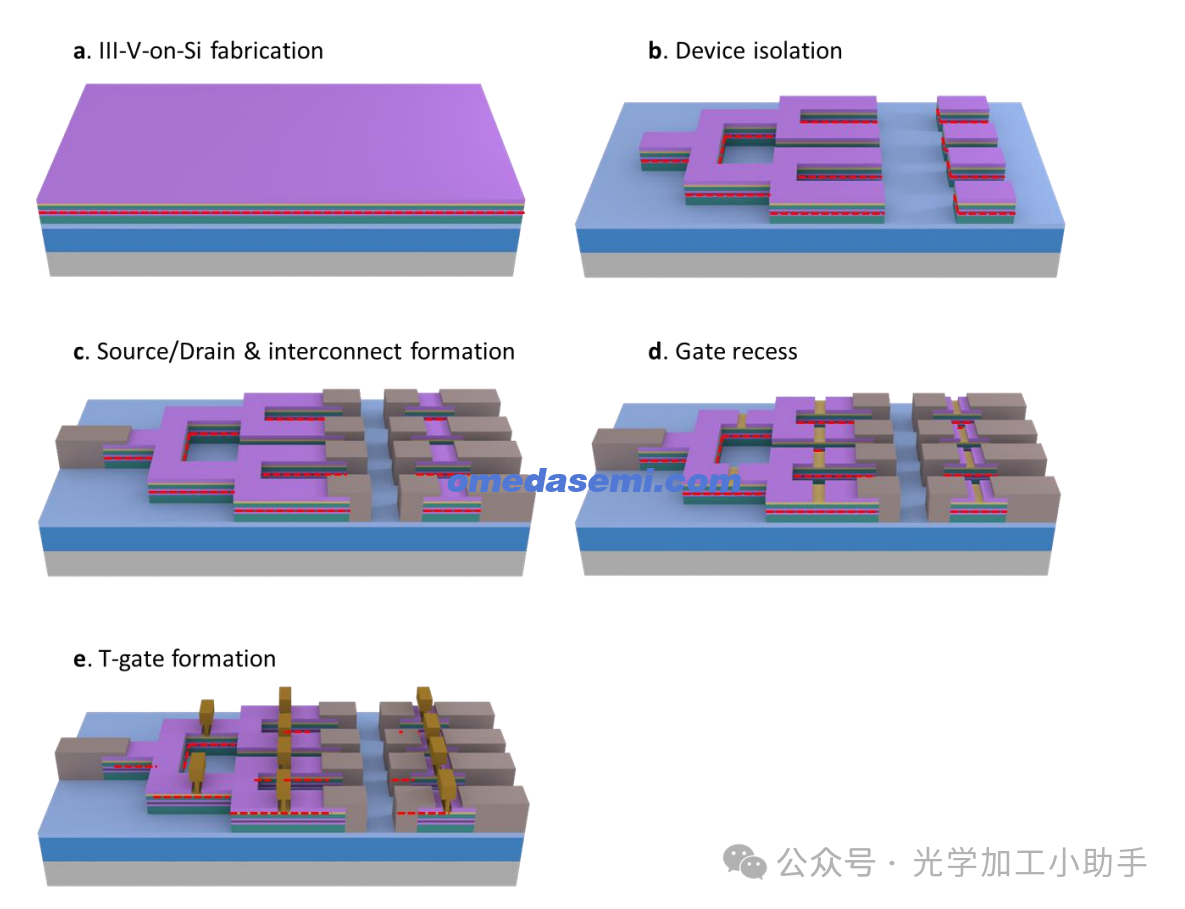

基于HEMT的低噪声射频器件和HEMT路由电路使用相同的工艺步骤制作。处理步骤的示意图见补充图2。通过H3PO4:H2O2:H2O和H3PO4:HCl溶液进行器件区定义。在HCl:DI溶液去除本征氧化物后,沉积了Nb接触金属。接着,我们重新沉积了Nb作为全局互联。T形图案通过双重曝光电子束光刻定义,电子束光刻胶使用PMMA和PMMA-PMAA的双层结构。在沉积栅极金属之前,通过柠檬酸溶液对n+-InGaAs层进行蚀刻,形成栅极凹槽。然后,沉积Pt/Ti/Au的栅极金属。最后,在250°C下退火5分钟。射频放大器、直流开关和射频开关的器件具有40μm、5μm和30μm的栅宽(WG),而栅长(LG)和源漏间距(LSD)均为70nm和2μm。通过相同的集成工艺,我们展示了基于III-V HEMT的Si CMOS异质和单体3D集成,且顶部和底部器件及电路的性能没有任何退化。

电气特性测试

低温电气测量使用配备冷却辐射屏蔽的Lakeshore低温探针台进行,以防止器件因热辐射而加热。直流特性通过配备Keithley 4200的晶圆探针台进行测量,射频特性则通过配备VNA、信号发生器和频谱分析仪的晶圆探针台进行测量。GSG探针和同轴电缆使用离晶圆两端的双端开路短路负载法进行校准。此外,还使用标准的去嵌入技术,通过晶圆上的开路和短路图案去除与接触垫相关的寄生电容和电感。