本文分享一篇文章,作者开发出了用于超低功耗声波谐振器的在4HSIC上进行深反应刻蚀的工艺

采用高声速材料制成的具有高品质因数 (Q) 的集成机械谐振器对于各种应用至关重要,包括化学传感器、定时谐振器和用于 GPS 遮挡环境中导航的高性能惯性传感器。虽然硅是实现微机电系统 (MEMS) 谐振器的最常用基板,但由于 Akhiezer 极限高,SiC 表现出极小的固有声子耗散。本文报告了单晶 4H 绝缘体上 SiC (SiCOI) 基板的纳米精度深反应离子蚀刻 (DRIE) 的最新结果,以探索体声波 (BAW) SiC 谐振器的耗散极限。我们首次报告了 ƒ·Q 乘积超过 1×1014 Hz 的电容式 Lamé 模式谐振器。讨论了表面粗糙度对耗散的贡献以及在 SiCOI 衬底中蚀刻镜面抛光沟槽的实际考虑,为 Q 值超过 100 M 的微机械 SiC 谐振器铺平了道路。

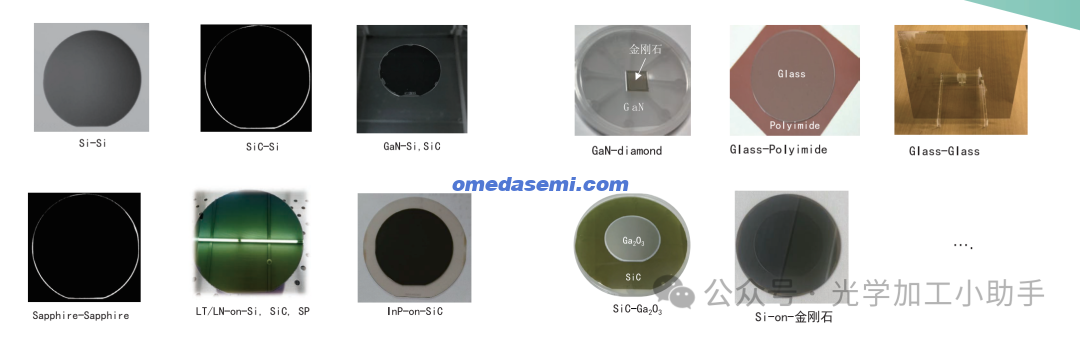

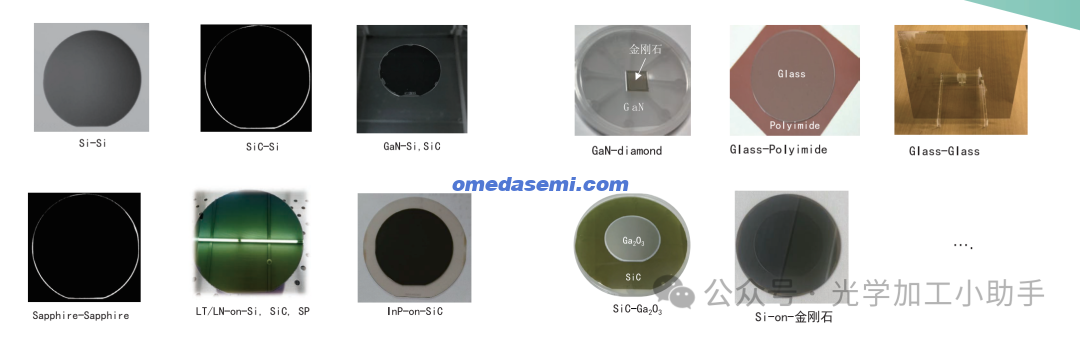

复合衬底片--SiCOI/GaNoI库存,定制加工

GaAs-SiC,InP-Diamond, LN-SiC,Si-Si,GaN-Dlamond,Sl-Diamond,蓝宝石-蓝宝石,金刚石-sic, sic-inp,sic-LN, ic-ga2o3,glass--glass,Si-SiC,Si-GaAs、GaAs- SiC、Si–SiC、SiC–SiC、Ge–Ge 、Al 2 O 3 -Al 2 O 3 ,GaP-InP, GaN-Si、LiNbO 3 -Al 2 O 3 、and more(晶体ybyag,ndyvo4,zns,陶瓷,等等)

LiNbo3-SI/SIC,LiTaO3-SIC/Si (国产技术,交期快,无气泡,良率高)

扩展的多材料的体系,将键合技术扩大了应用范围

*MEMS传感器 *光子集成电路 *半导体激光器

*功率器件 *3D封装 *异质集成

划重点--代工,代工,代工,卖设备

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜方式(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束直写等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

激光器芯片/探测器芯片/PIC芯片封装耦合服务"

请联系小编免费获取原文,也欢迎交流半导体行业,工艺,技术,市场发展

简介

微机械和纳米机械谐振器广泛应用于各种应用,包括消费电子产品、精密机器人、惯性导航 (1) 和用于健康监测的可穿戴传感器 (2)。这些谐振器的关键性能指标包括 Q 值和热机械布朗运动噪声。尽管硅 (Si) 是高 Q 值应用的成熟基板,但第三代半导体碳化硅 (SiC) 有望支持具有超高 Q 值的小体积谐振器,远远超出了 Si 的范围。SiC 的非凡前景是将机械 Q 值提高 30 倍,这源于其相对于 Si 的声子 Akhiezer 极限更低,接近光学谐振器的声子 Akhiezer 极限。最近,我们的小组展示了集成 Lamé 谐振器,其机械 ƒ·Q 值大于 1×1014 Hz (3),比 Si 的 Akhiezer 极限高出 4 倍,并受到微尺度表面粗糙度的限制。本文介绍了在开发 SiC MEMS 技术平台以用于机械 Q 值达到100 M。

SiC MEMS 作为技术平台的发展面临多重障碍,包括 (a) 绝缘体上 SiC (SiCOI) 基板的高开发成本(例如,裸 SiC 晶圆成本、制备、键合和精确厚度控制的研磨)和小批量生产,(b) SiCOI 基板在晶圆级和纳米级精度上的微加工挑战,以及 (c) 有限的加工热预算。虽然成本

100 毫米 n 掺杂 4H-SiC 基板的成本接近 850 美元,这是厚单晶 SiC MEMS 发展的不可否认的障碍,SiC 晶圆成本一直在稳步下降;由于蓬勃发展的电动汽车行业的需求不断增长,预计这一趋势将继续下去。然而,专用于 SiC 晶圆级加工的高密度干法蚀刻机的部署基础有限,严重阻碍了基础研究。也就是说,很少有论文关注 SiC 的深反应离子蚀刻 (DRIE) (4),甚至更少关注用于超高 Q MEMS 应用 (6) 的 SiCOI 基板 (5) 的 DRIE。

本文重点介绍在开发用于需要超低功耗的应用的 SiC MEMS 技术平台时所面临的挑战。这里简要回顾了设计考虑和最近发表的结果 (3) 的主要结果,以证明开发具有纳米级精度的厚单晶 SiCOI 基板的深度反应离子蚀刻以制造具有超低耗散的体声波谐振器的合理性。

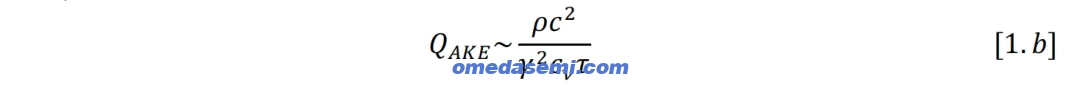

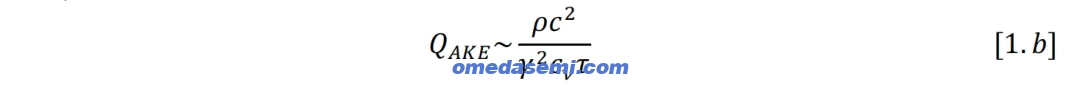

具有超低耗散的 SiC Lamé 谐振器的设计

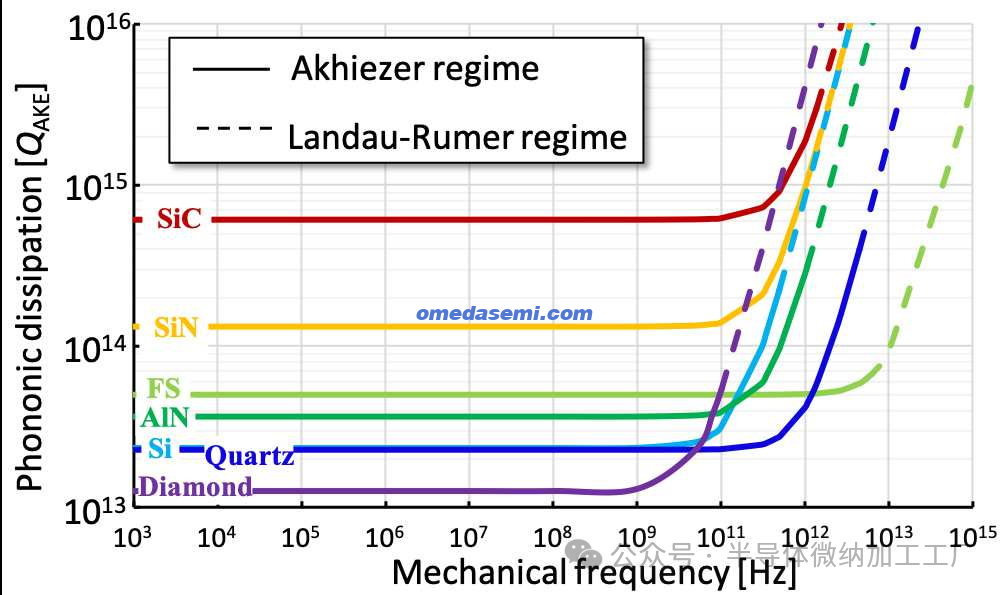

SiC 的原始材料特性共同限制了 Akhiezer 状态下的非谐波声子-声子散射。所有相关的材料特性 - 低声子弛豫时间 (t = 2.2 ps)、高德拜速度 (c = 8.8 km/s)、小的 Grüneisen 参数 (y = 0.3)、高密度 (p = 3.2 kg/m3) - 有助于最大限度地减少 SiC 中的声子-声子散射,使其成为相对于晶圆级普通微加工基板 (7,8) 具有声学优越性的基板(图 1)。然而,需要充分的设计和完美的制造来将耗散与 SiC 微机械谐振器中的 Akhiezer 阻尼结合起来:

图 1. 在可微加工基板中,SiC 有望支持超高 Q 谐振器。

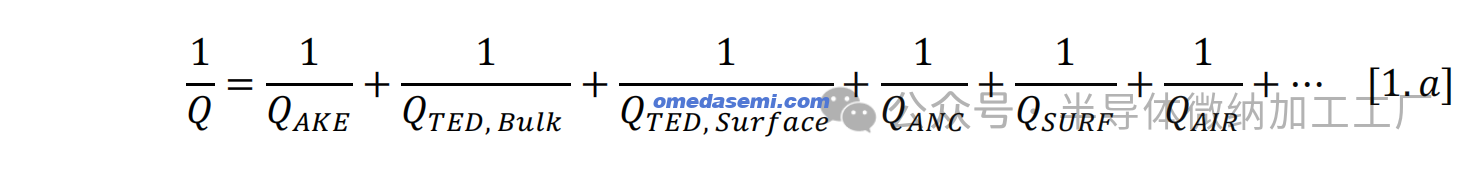

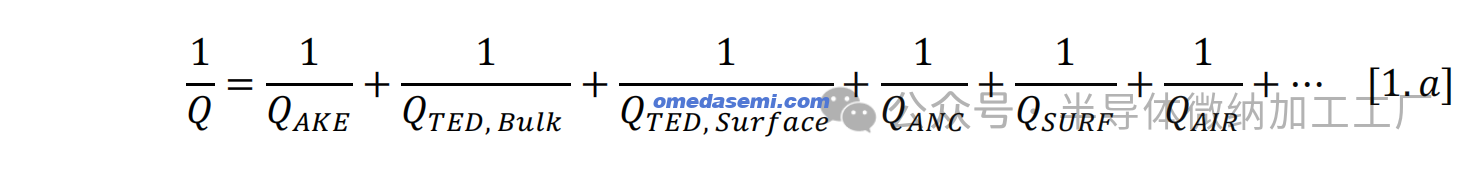

在方程式 [1] 中,AKE 表示 Akhiezer 阻尼,TED 表示由于表面粗糙度而导致的材料本体和表面的热弹性阻尼 [9],ANC 表示锚定损耗,SURF 表示表面损耗 (10),AIR 表示粘性阻尼。粘性阻尼在本研究中可以忽略不计,因为设备在 µTorr 真空水平下运行。与弯曲谐振器不同,BAW 谐振器可以在 mTorr 真空水平的封装环境中保持性能 (11)。表面损耗可能在未封装 SiC 谐振器的 Q 因子随时间下降中发挥作用,本文不讨论这一问题。

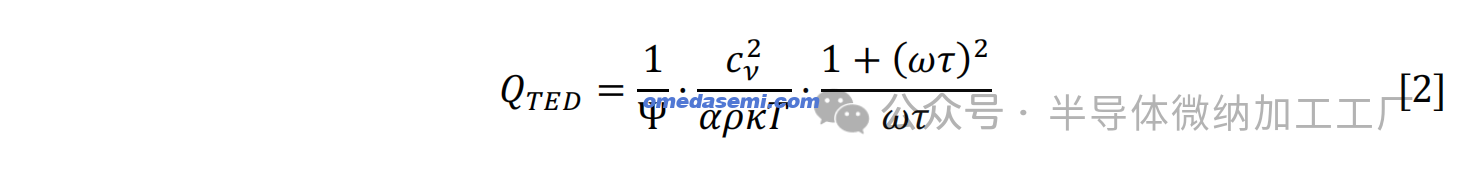

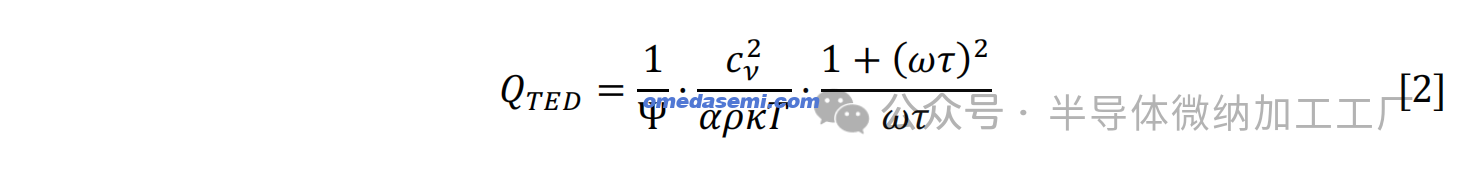

由于表面粗糙度导致 SiC 谐振器中的热弹阻尼。较高的热导率 (k = 370 W/(m·K))、较高的热膨胀系数 (a = 4.3 ppm/°C) 和较高的密度使 SiC 产生的 TED 比 Si 多 10 倍。幸运的是,TED 不仅与材料有关,还与模式和频率有关,如方程 [2] 所示。

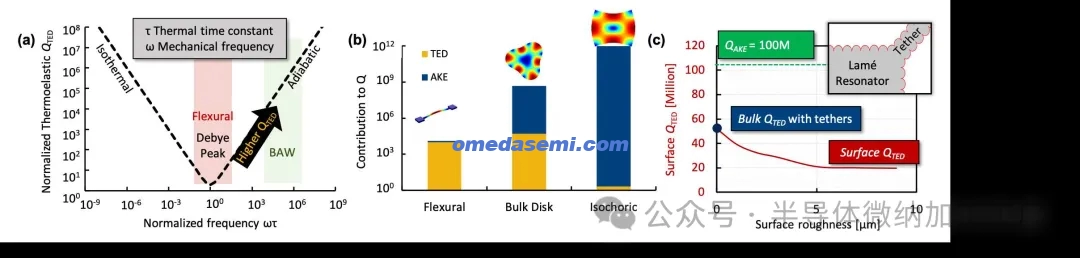

在方程 [2] 中,cv 表示比热,Ψ 表示模式相关因子,w 表示角频率,t 表示本征热模式的时间常数 (12)。洛伦兹项定义了三个独立的工作状态:等温 (wt << 1)、德拜峰 (wt ~1) 和绝热 (wt >> 1),如图所示。在第一个和最后一个状态下,热机耦合效率较差,导致 QTED 较高。具有毫米级平面频率设定尺寸的体声波 (BAW) 谐振器在绝热状态下运行。相比之下,TED 在弯曲谐振器通常工作的德拜峰附近加剧,使其不足以达到超高 Q 值。在 BAW 谐振器中,方形谐振器是理想的选择,可以避免 SiC 相对于 TED 的劣化材料特性,因为它们的恒容 Lamé 模式表现出接近 10 亿 (B) 的 QTED。工作频率接近 6.27 MHz 的完美方形谐振器(例如,没有释放孔或系绳)的声能量耗散与内部 Akhiezer 阻尼有关,估计 QTOTAL 约为 106 M。但是,支撑系绳中的位移会产生一些 TED,并将 QTOTAL 限制在 ~30-60 M,具体取决于系绳的尺寸(图 2)。最后,假设锚定损耗可忽略不计,设备侧壁上的表面粗糙度将产生表面 TED,以及体积 TED,并将 QTOTAL 限制在 ~16-30 M(3)。数值模拟预测具有 1 个晶胞的 Lamé 谐振器的 QANC 约为 47 M,而具有 2 个晶胞的 Lamé 谐振器的 QANC 约为 9 B。考虑到 Akhiezer 阻尼、体积和表面 TED 以及锚定损耗,预测的 1 个晶胞 Lamé 的 QTOTAL 为 17 M,2 个晶胞 Lamé 的 QTOTAL 为 26 M。具有量子限制耗散的 SiC Lamé 谐振器需要对基板进行完全的声聋处理,并通过深反应离子蚀刻减轻表面热弹阻尼,纳米级 RMS 表面粗糙度接近 50 nm。

图 2. 在绝热状态下操作 BAW 谐振器可减轻 TED。(a) 与在德拜峰附近工作的弯曲谐振器相比,绝热状态下的 BAW 谐振器表现出更高的 QTED (b) 除此之外,没有系绳的恒体积 Lamé 模式几乎完全避开了 TED (c) 然而,Lamé 谐振器会因为系绳应变和粗糙度而产生 TED。

绝缘体基板上碳化硅的纳米精度深反应离子蚀刻

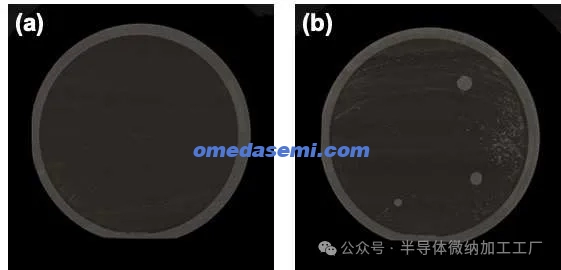

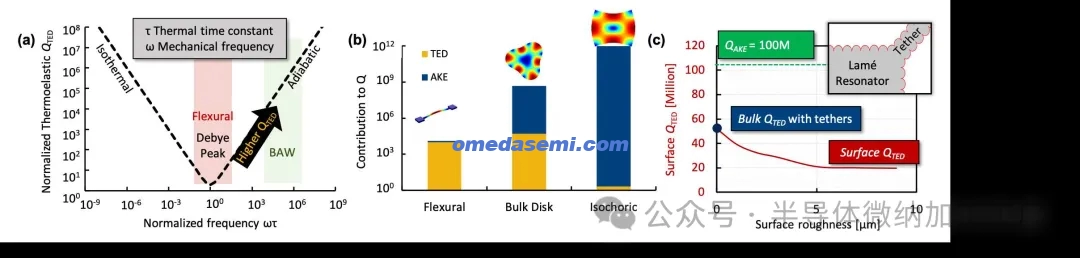

在本节中,我们将介绍 SiCOI 基板加工以及使用 STS AOE Pro 对 SiCOI 基板进行纳米精度高纵横比 DRIE 的双管齐下方法。在进行 MEMS 加工之前,我们与 Disco® 合作制造了 100 毫米 SiCOI 基板,用于边缘修整和研磨,并与 Entrepix® 和 EVG® 合作,分别用于 400°C 下的抛光和熔合。40 µm 厚 SiCOI 基板的高开发成本和小批量制造(图 3)加上不可靠的 SiCOI DRIE 结果使我们无法自信地加工完整的 SiCOI 晶圆。相反,晶圆被切成四分之一,每个四分之一单独加工,因此需要使用镀镍载体晶圆。

图 3. 100 毫米 SiCOI 基板的定制熔融键合表明,在退火过程中 (a) 需要施加压力,以避免形成 (b) 高压滞留气泡。5 毫米边缘修整预键合可提高研磨产量。

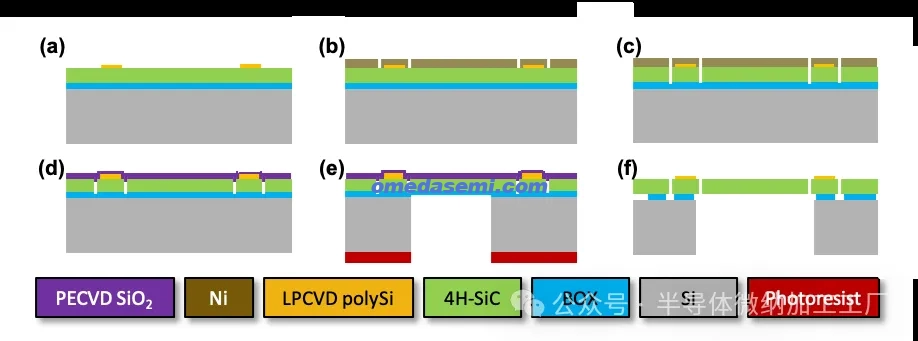

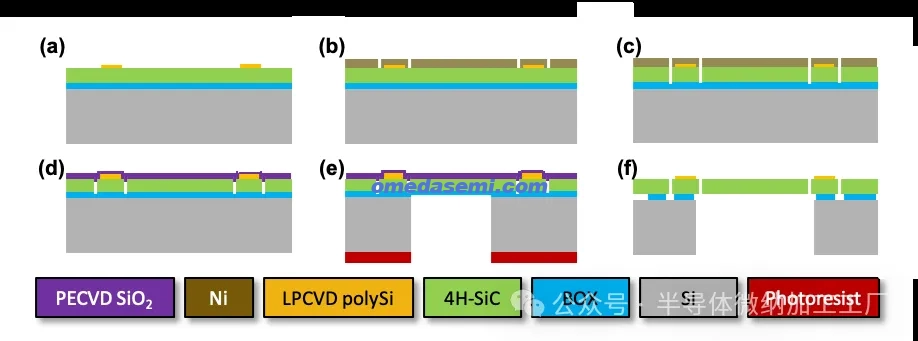

图 4 显示了我们的低温制造工艺流程,其热预算受到 Si 和 SiC 之间 CTE 不匹配的限制。异质 SiCOI 衬底无法在远高于 700°C 的温度下在晶圆级退火,否则晶圆会严重翘曲或开裂。但是,在 1,100°C 下进行长达一小时的退火是必要的,以使 BOX 致密化,并使其在暴露于 HF 时能够均匀蚀刻,而不是一分为二。同样,SiC 的高功函数需要沉积和高温退火导电薄膜,以在铝线键合和 SiC 之间形成欧姆接触。封装和其他需要在晶圆级实施这些步骤的高级处理可能需要开发同质 SiCOI 衬底(例如,SiC-on-Insulator-on-SiC)以限制热应力。在这项工作中,所有高温步骤都在芯片级实现,以避免处理翘曲的 SiCOI 衬底。

图 4. 单晶 SiC 微加工工艺流程示意图。(a) n 掺杂 LPCVD

多晶 Si 图案化 (b) 通过 LIGA 工艺进行 Ni 图案化 (c) SiC 的 DRIE (d) PECVD SiO2 (e) Si 腔 (f) 通过退火和 HF 释放激活欧姆接触。

我们首先沉积 n 掺杂的 LPCVD 多晶硅 (polySi),以与 n 掺杂的 4H-SiC 形成欧姆接触(图 4.a)。打破强 Si-C 键需要高自偏置直流电压,而光刻胶和二氧化硅 (SiO2) 则无法成为合适的掩模材料,其选择性接近或低于 4:1。我们使用电镀镍作为 SiCOI 基板 DRIE 的硬掩模(图 4.b)。电镀镍的优势包括相对于其他镍沉积方法的低应力、在 SF6 等离子体化学中对 SiC 的高选择性以及垂直和平滑的轮廓,这对于以纳米级精度蚀刻 SiC 至关重要。掩模锥化、不均匀的镍电镀速率以及有时晶圆之间的大厚度变化实际上将 Ni 的有效掩模选择性限制在 ~15:1。低电流虚拟电镀运行用于去除由于金属溶解和光亮剂和添加剂积累而产生的污染,而主运行需要高电流密度以利于低应力 Ni 的沉积。SiCOI 四分之一晶片通过低熔点晶体键合粘合到镀镍硅晶片上,以方便蚀刻后清洁。我们用剃须刀片去除多余的晶体键合,以防止溅射以及气泡形成,因为气泡会降低 SiCOI 四分之一晶片和镀镍硅载体晶片之间的热接触。干蚀刻 SiC(图 4.c)后,在稀 HNO3、Piranha 和 EKC 265 中清洁晶片。沉积 PECVD SiO2 层以通过背面处理保留原始 SiC 沟槽(图 4.d-e)。将 SiCOI 四分之一晶片切成小块,在 1,100°C 下退火 15 小时,在 N2 环境中在 1,200°C 下退火 4 分钟,然后在 HF 中释放(图 4.f)。在这些温度下退火对于激活 SiC 欧姆接触上的多晶硅是必要的;然而,N2 不再是惰性气体,当流速超过 0.1 slm 时,可能会与多晶硅形成 SiN,从而降低 SiC 电极的表面质量。

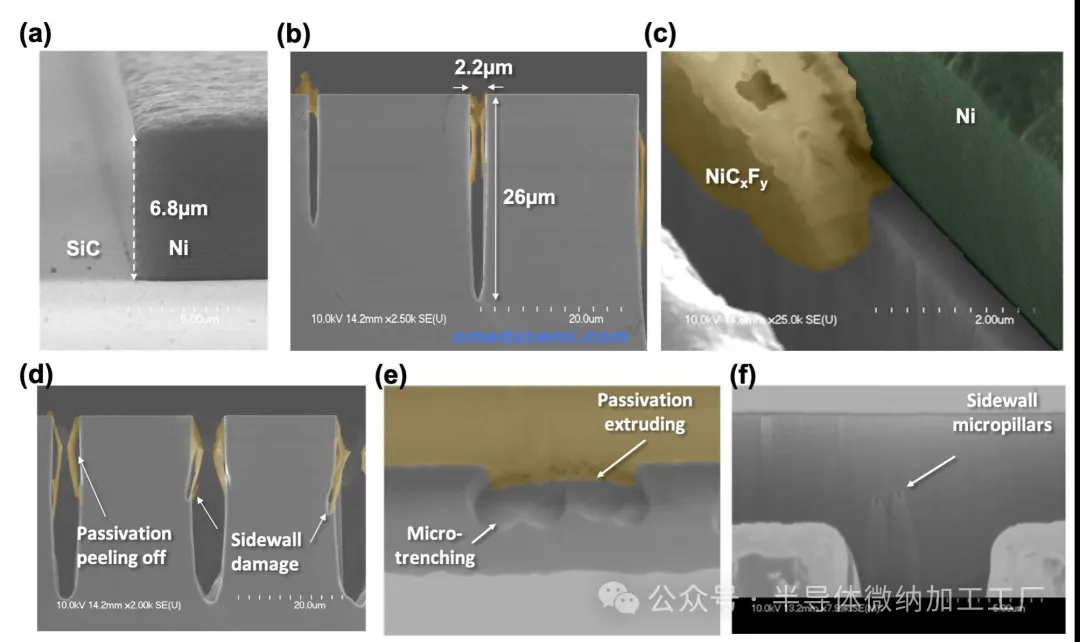

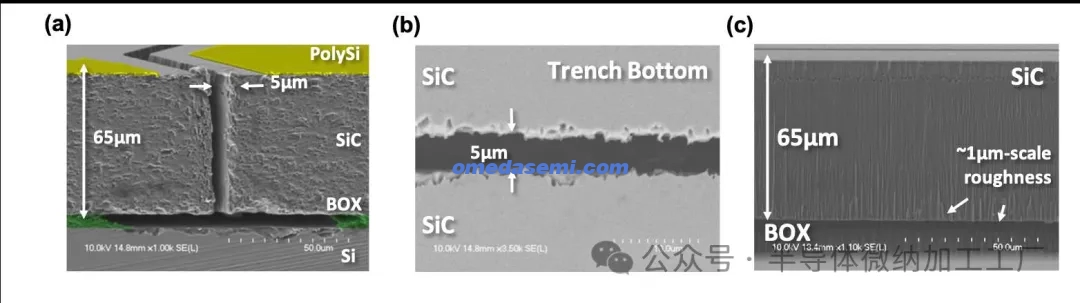

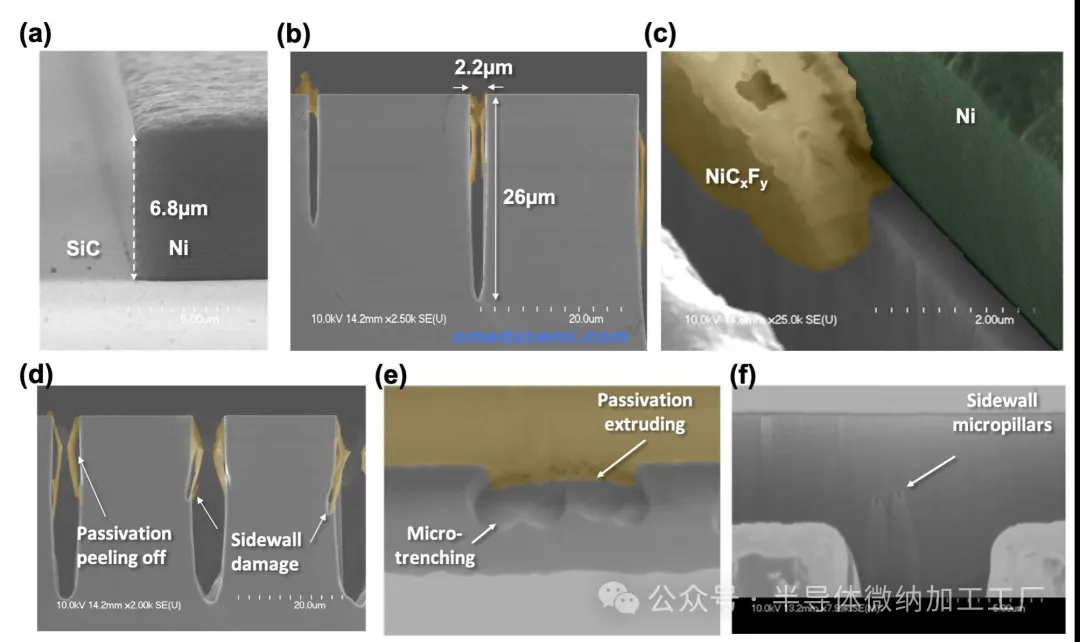

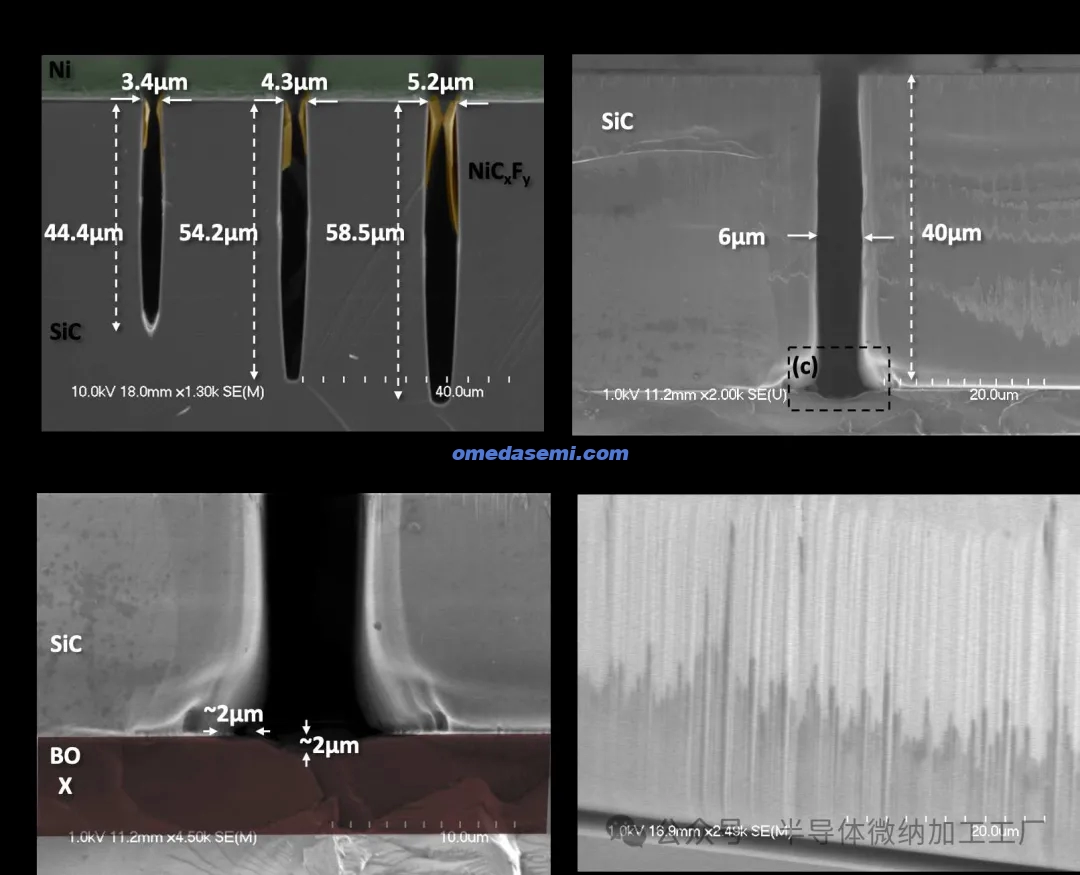

尽管 Ni 对 SiC 具有足够的选择性并且可以高保真地进行图案化,Ni 不仅具有垂直和光滑的侧壁(图 5.a),还对 SiC 作为 MEMS 平台技术的实施提出了多重挑战(图 5.b-c)。在蚀刻过程中,溅射的 Ni 粒子会聚合挥发性 CxFy 蚀刻副产物。目前尚无已知的蚀刻化学方法可以去除金属氟碳 NiCxFy 钝化层,因此这种钝化层会逐渐在腔体的侧壁上堆积。与 Bosch 工艺不同,该工艺通过连续的蚀刻和钝化循环在 Si 中蚀刻高纵横比沟槽,同时保持腔体处于原始状态 (13),而 SiC 的 DRIE 迄今为止是一种肮脏的工艺。每隔约 30 个 RF 小时,使用 Scotch-Brite® 和 IPA 手动去除 NiCxFy 钝化层。出于安全考虑,手动清洁在室温下进行,这会使磁铁经受温度循环,从而慢慢降低磁通量。除此之外,由于等离子体的恶劣条件,O 形圈会极快地降解。随着时间的推移,蚀刻条件会发生变化,干蚀刻配方必须在非为 SiC DRIE 设计的干蚀刻机(例如 STS AOE)中不断优化。我们已将干蚀刻配方迁移到 STSAOE Pro,该配方不使用 O 形圈将晶圆夹在卡盘上,并且观察到相对于 STS AOE 更具可重复性的蚀刻结果。

图 5. 使用低 SF6 配方对 SiC 衬底进行高纵横比深反应离子蚀刻 (a) 具有垂直和光滑轮廓的高保真 Ni 掩模 (b) CxFy 副产物聚合限制了沟槽的纵横比 (c) NiCxFy 沉积在 Ni 掩模上而不会降解。(d) 由于钝化剥落导致的侧壁损坏 (e) 局部微沟槽使钝化挤压成为可能 (f) 侧壁微柱生长并可能导致器件电气短路。

除了降低腔体状态外,NiCxFy 钝化还会引入各种沟槽缺陷(图 5.d-f)。这些缺陷包括沟槽变细、侧壁损坏、侧壁微柱和侧壁粗糙度。高密度的表面缺陷会通过表面热弹性损耗耗散声能,在这项工作中占主导地位。此外,侧壁微柱可能会造成电气短路和原本隔离的区域(例如设备和电极)之间的潜在不平衡,并使微机电谐振器无法运行。

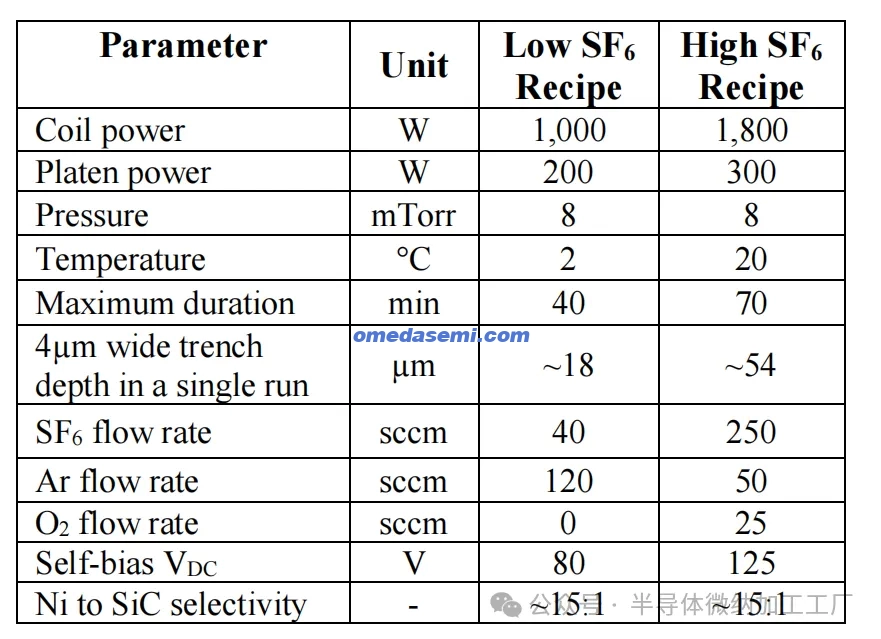

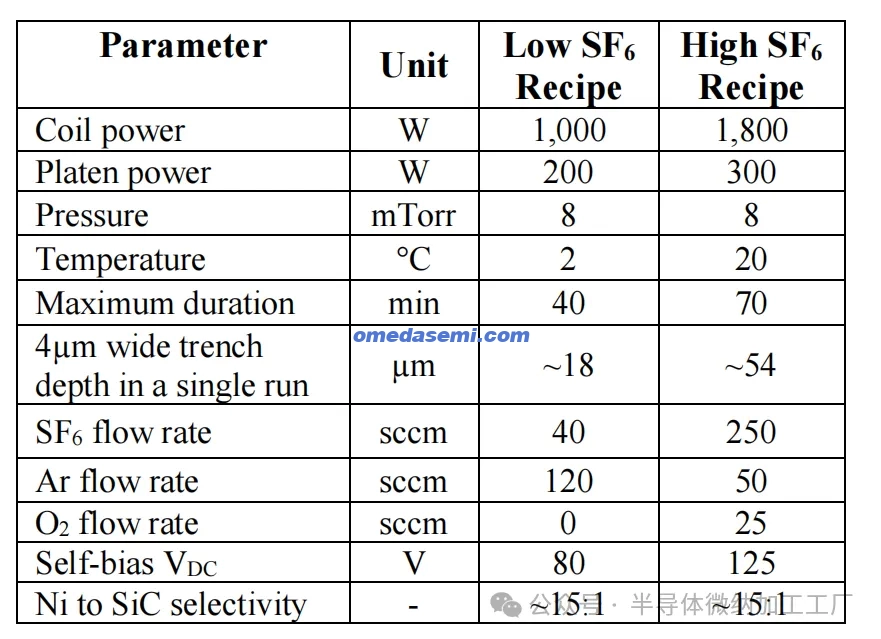

表 1:使用 STS AOE Pro 的高纵横比 SiC 干法蚀刻配方

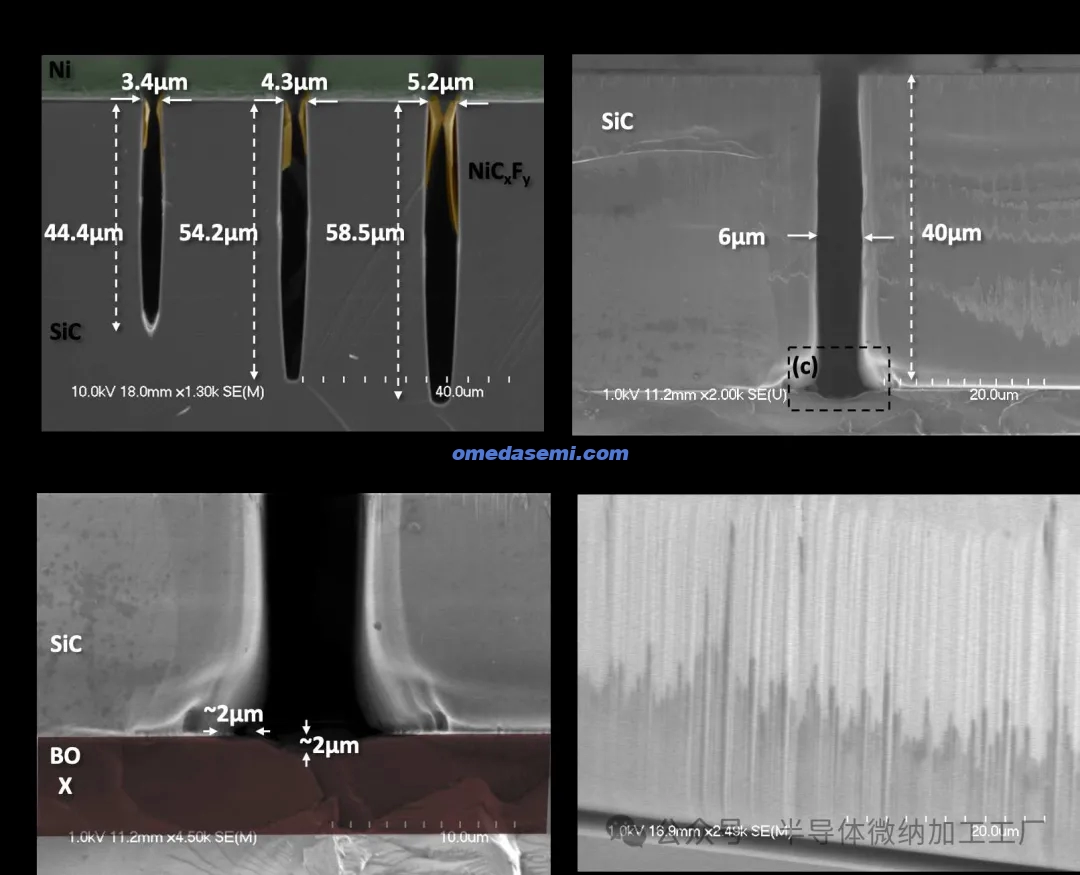

我们开发了两种不同的干法蚀刻配方,以尽量减少侧壁微柱和其他蚀刻缺陷的形成(表 1)。低 SF6 配方旨在通过强调物理蚀刻来最大限度地降低钝化的横向生长速率,而高 SF6 配方则有利于化学蚀刻(表 1)。在低 SF6 配方的 40 RF 分钟后,钝化层厚度约为 400 纳米。进一步蚀刻后,钝化层厚度将增加到 700 纳米以上并剥落。在 40 分钟内,4 µm 宽的沟槽深度为 18 µm,不足以达到 40 至 60 µm 深的 BOX。为了延长蚀刻时间,我们在约 2 小时内用最少的超声处理将钝化层溶解在加热至 80°C 的 EKC 162® 中。在较低的 EKC 温度下,钝化层不会被去除,而在较高的温度下,Ni 在种子层 Cr/Au 上的附着力变差,影响进一步的干法蚀刻。通过这种方法,我们能够蚀刻高纵横比沟槽,仅受 Ni 厚度的限制(图 6)。虽然 EKC 清洗的 SiC 沟槽和 Ni 掩模看起来完好无损,但我们经常观察到使用低 SF6 配方时侧壁微柱的密度要高得多,这使得该配方不可靠,无法蚀刻具有完好侧壁且没有电气短路的高纵横比 SiCOI 沟槽。在其他所有条件不变的情况下,EKC 清洗后继续蚀刻会产生更多的氟碳钝化,因为更多的 SiC 侧壁暴露出来。

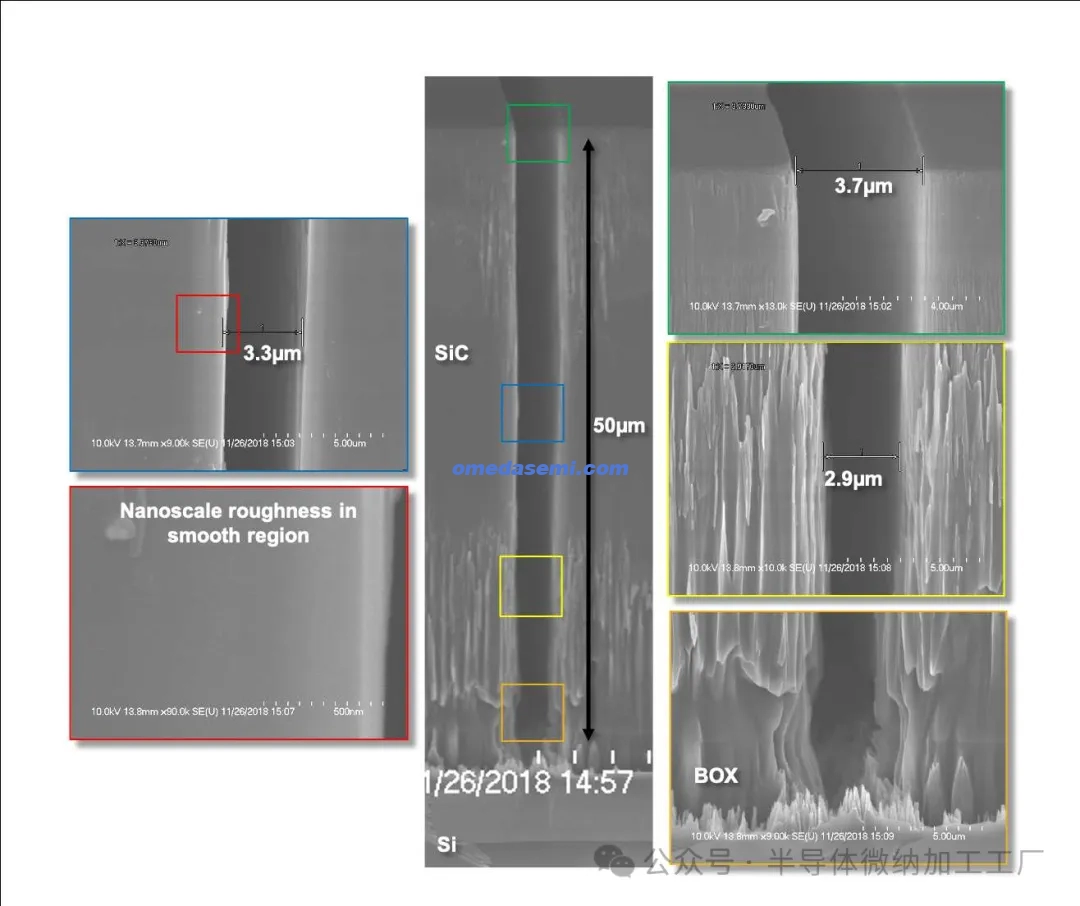

图 6. 使用低 SF6 配方蚀刻三次 SiCOI 沟槽的 SEM 观察结果,其中中间经过两次原位 EKC 清洁步骤。

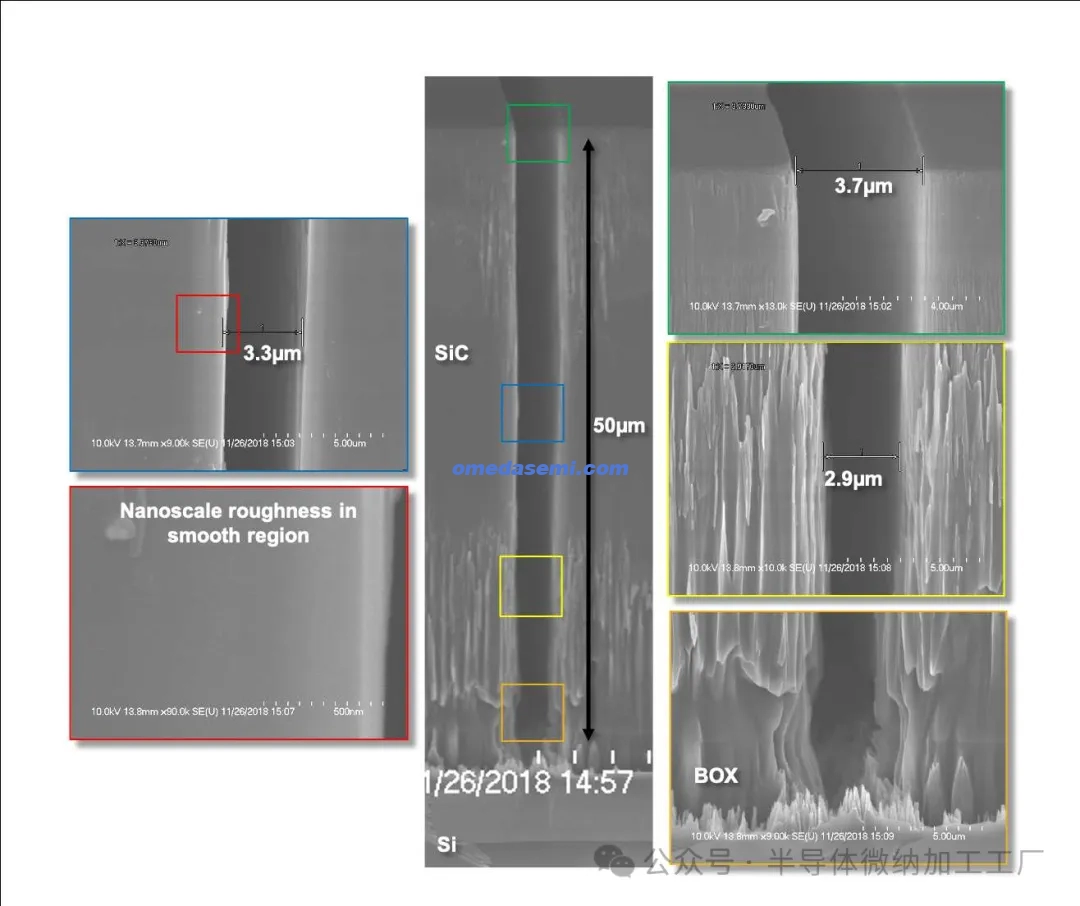

图 7. 使用高 SF6 配方对 SiC 和 SiCOI 衬底进行高纵横比深反应离子蚀刻 (a) CxFy 副产物聚合限制了沟槽的纵横比。(b) 在 SiCOI 衬底中蚀刻高纵横比沟槽会产生 (c) 靠近埋层氧化物 (BOX) 层的切口,以及 (d) 光滑且垂直的侧壁轮廓

或者,高 SF6 配方通过一次蚀刻达到 BOX 来绕过中间的原位湿法清洗步骤,使其成为比低 SF6 配方更可靠的干法蚀刻配方。高 SF6 配方的主要挑战是能够蚀刻垂直沟槽而不会弯曲,如图 7 所示。除此之外,SiCOI 沟槽的整体质量仍然不如 SOI:纵横比限制在 20:1 以下,并且埋层氧化物层 (BOX) 附近的凹口很明显,这对于使用侧壁上的牺牲层来实现非常高纵横比电容间隙 (14) 的先进 HARPSS 类工艺来说是不够的。

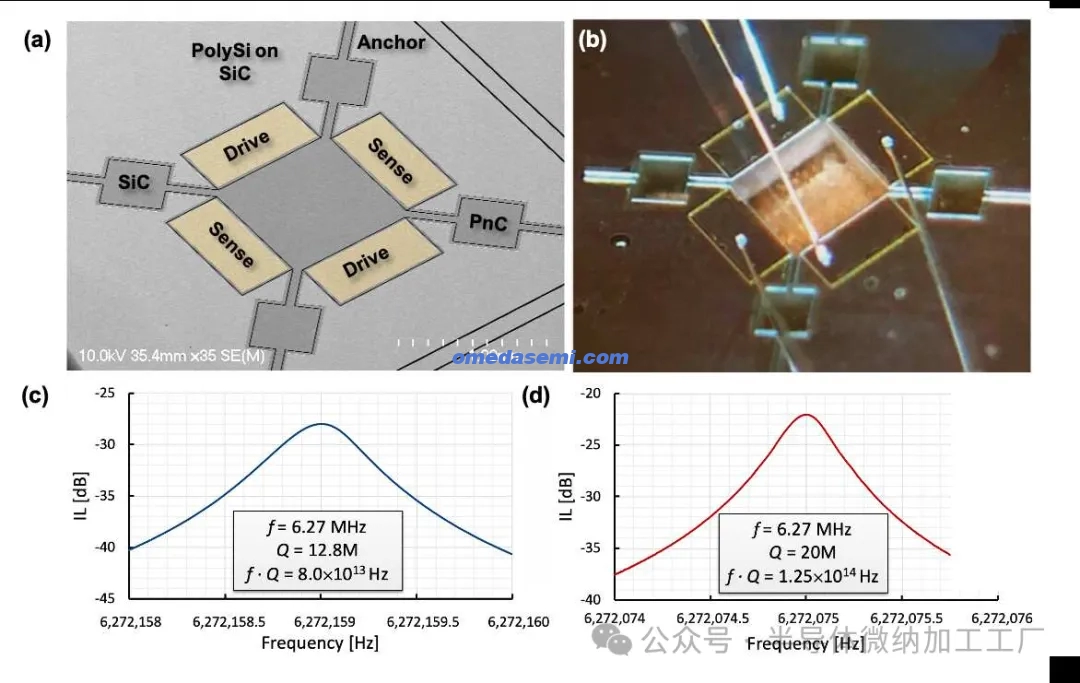

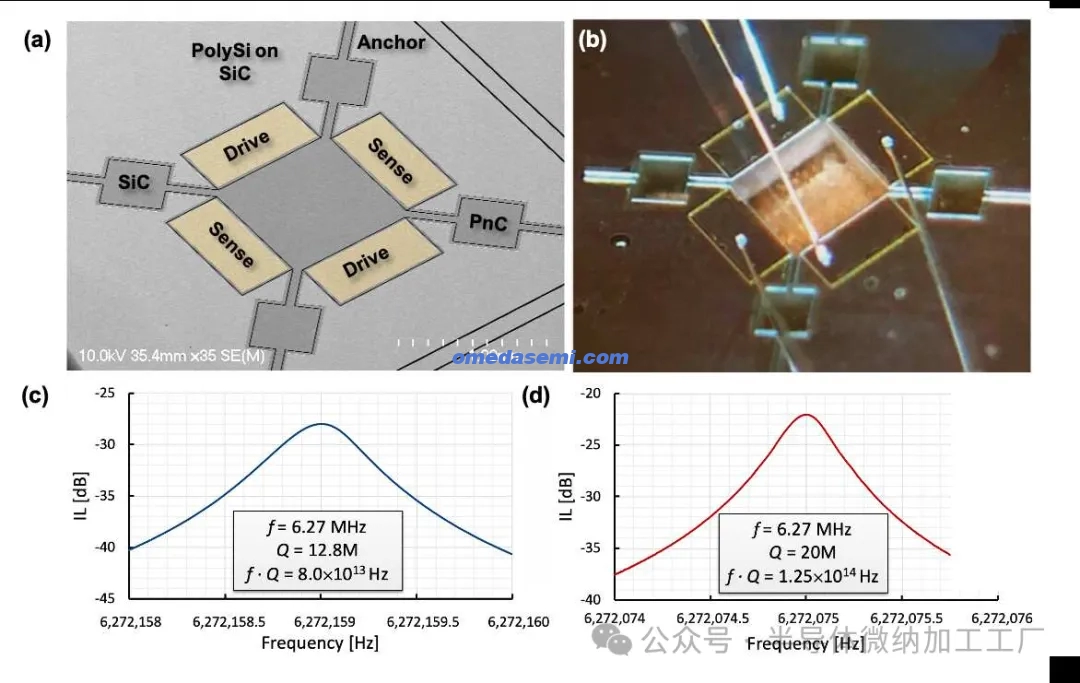

图 8. (a) 使用低 SF6 配方制造的超高 Q 值第二代 SiC Lamé 谐振器的 SEM(b-c) 第二代 SiC Lamé 模式谐振器表现出有史以来在 Lamé 微机械谐振器中报告的最高 Q 值 20 M,并突破了 ƒ·Q = 1´1014 Hz 的障碍,与模拟结果高度一致 (6)。

超高 Q SiC Lamé 模式谐振器的电容测量

图 8.a-b 显示了通过定制 SiCOI 基板的 DRIE 制造的 Lamé 模式谐振器。本节将先讨论与 SiC 谐振器静电传导相关的具体制造细节,然后再介绍实验结果。6.5 mm × 8 mm SiCOI 芯片使用铜带固定在带有跨阻放大器 (TIA) 的 PCB 板上,铜带可通过透明 SiC 层和 Si 腔体观察到。使用经过校准以消除馈通的网络分析仪记录 900 µm 宽的 6.27 MHz Lamé 谐振器的频率特性。尽管传导间隙宽 5 µm,但由于谐振器的超高 Q 值在 1000 万到 2000 万范围内,接近 15 V 的极化电压 Vp 足以观察到清晰的峰值。驱动功率保持在 - 20 dBm 附近,PCB 和设备有 30 分钟的稳定时间以达到热平衡。180° 相对电极在 PCB 上短路,以电容驱动和感应 SiC Lamé 谐振器的运动。

图 8.b-c 显示了 6.27 MHz Lamé 谐振器,其具有一个 PnC 晶胞,Q = 12.8 M 和 ƒ·Q = 8×1013 Hz,非典型 Q 因子范围在 10 到 12 M 之间。具有两个 PnC 晶胞的 6.27 MHz Lamé 谐振器显示高达 20 M 的更高 Q 值和 ƒ·Q = 1.3×1014 Hz。第二种设计的多个双晶胞 Lamé 谐振器显示 Q 值接近 15 M。与模拟结果一致,第二种设计测得的 Q 值高于第一种设计。由于根据 COMSOL 模拟,额外的系绳长度对 TED 没有贡献,因此排除了 TED 来解释测量的差异。我们怀疑锚损失是第一种设计的主要损失机制,而第二种设计可以忽略不计。此外,在-50°C至85°C的温度范围内,测得的轴上n掺杂4H-SiC Lamé谐振器的频率温度系数(TCF)为-12 ppm/°C,比(100)Si(6)的温度系数低约3倍。

电容式 SiC Lamé 微机械谐振器首次在兆赫频率范围内表现出超过 1×1014 Hz 的 ƒ·Q 乘积,超越了之前研究取得的性能 (3)。迄今为止,SiC 机械谐振器大多使用沉积在 Si 或 SiO2 上的多晶 SiC (15、16) 或在德拜峰附近运行低频弯曲模式 (17),这使得它们对晶粒间损耗机制和体 TED 都很敏感,在单晶 SiC 的 BAW 模式下几乎可以忽略不计 (18)。

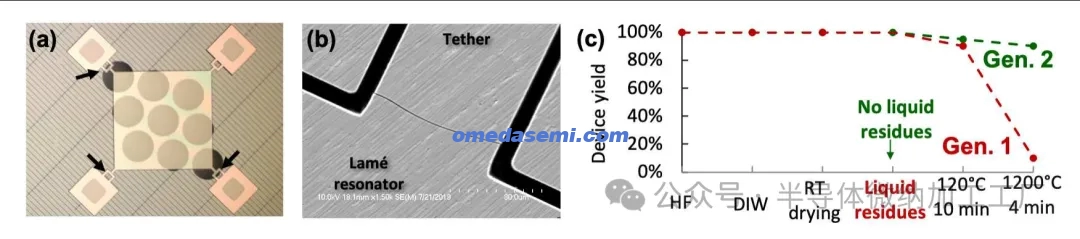

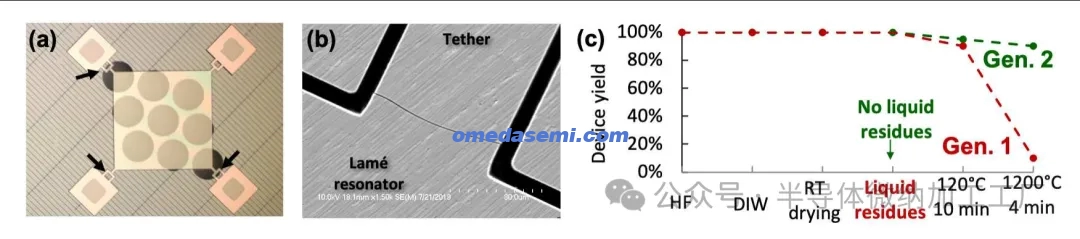

图 9. (a) 带有虹吸晶体的 Gen.1 Lamé 谐振器和 (b) 破裂的系绳,(c) 可以通过仔细干燥芯片、形成 Si 腔体和增加系绳宽度来避免

第一代 SiC Lamé 谐振器(Gen. 1,图 9)具有通过四分之一波长匹配的 380 µm 厚 Si 手柄层蚀刻的声子晶体 (PnC),其声学带隙以 Lamé 模式的 6.27 MHz 谐振频率为中心。设计细节已在其他地方公布,主要是声学隔离中心支撑的固体磁盘,Qs 在 5 MHz 时高达 18 M (3)。然而,这种方法对侧面支撑的 Lamé 谐振器效果不佳。在释放过程中,几乎所有设备都会在正方形和一个或多个系绳的交界处出现裂缝。释放过程中的表面张力可能足以产生或传播预先存在的裂纹,从而导致器件故障(图 9)。第二代 SiC Lamé 谐振器(Gen. 2,图 10)旨在减少释放过程中的表面张力并加宽系绳以提高结构完整性。系绳的宽度增加到 30 µm,Si 手柄层中的腔体位于谐振器下方,以消除释放过程中的表面张力。我们观察到释放过程中的良率约为 90%;一些器件在快速热退火 (RTA) 期间仍然破裂,这表明由于 SiC 和 Si 之间的热膨胀系数 (CTE) 不匹配,在切割或退火过程中可能会产生一些初始裂纹。

虽然本文报告了迄今为止 SiC 谐振器中的最高 Q 值,但仍有很大的改进空间,因为理论 Q 值与 Si 谐振器之间的系数接近 5 倍

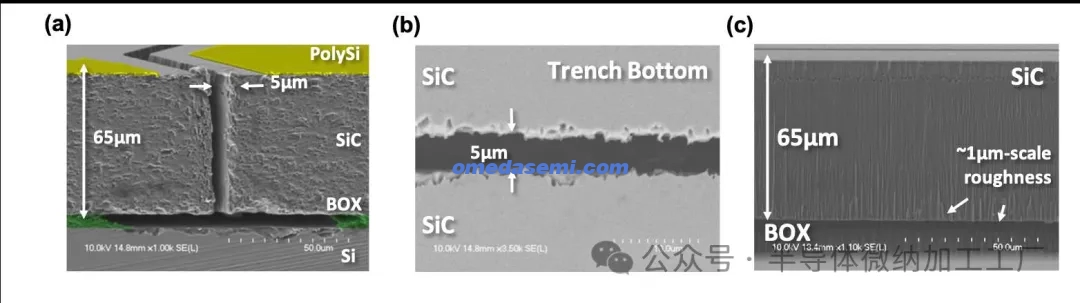

图 10. (a) 环绕 Lamé 谐振器的电容传导间隙的横截面 SEM。(b) 底视图和 (c) 侧视图显示粗糙表面限制了机械 Qs。ƒ·QAKE = 6.6´1014 Hz Akhiezer 极限和我们测量的最高 ƒ·QMeas. = 1.3´1014 Hz 仍然保持不变。如果表面粗糙度可以保持在 50 nm 以下,我们预计使用 Gen. 2 设计可以实现接近 50 M 的 Qs(图 10)。需要进行补充研究来验证 Grüneisen 参数 g 的理论值,因为 SiC 的 Akhiezer 极限尚未通过实验观察到。我们目前假设 g 为各向同性值,而已经证明 g 是各向异性的,并且 Akhiezer 极限与模式有关。

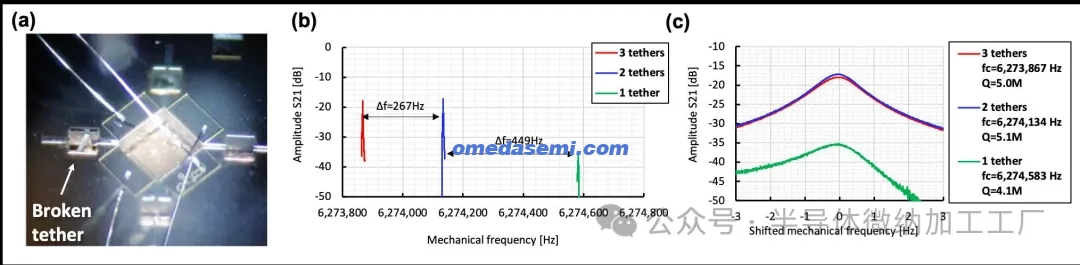

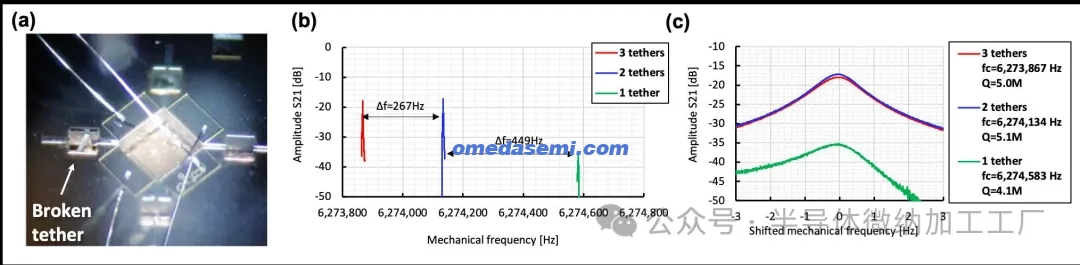

然而,Lamé 模式是纯剪切的,具有最低的 g,接近假设各向同性晶体的预测值。相反,我们的数值模拟表明,混沌表面粗糙度会产生表面 TED,这与体积 TED 和 Akhiezer 阻尼一致,从而将具有两个单元 PnC 单元的 Lamé 谐振器的 Q 限制在 26 M 附近。我们观察到,最高测量 Q 20 M 与预期 Q 26 M 之间具有极好的一致性。事实上,异常 Lamé 谐振器的 Q 因子可以低至 5 M(图 11)。我们怀疑这些异常谐振器中的表面粗糙度更为明显。尽管这些异常谐振器的 Q 值较低,但它们在声学上与基板分离,因为它们的耗散与安装条件无关。逐个断开它们的系绳或使用引线键合中的张力悬挂芯片不会显着改变 Q。

图 11. (a-c) 选择性地断开系绳可发现残余压缩应力很小,接近 50 MPa,并且 Qs 与系绳无关,表明低 Qs~5 M 是 TED 限制。

此外,我们观察到 Q 因子会随着时间的推移而下降约 20-30%。与 Si 类似,我们怀疑原生 SiO2 的形成、大颗粒和应力松弛会共同降低 Q。本研究中的 SiC Lamé 谐振器未封装在惰性环境中。需要进一步研究以估计封装设备中耗散的长期漂移行为,并严格控制和保持环境 (19)。