本文小编分享一篇文章,本文来自马普所,本文的特点是在氮化硅薄膜的制造上,不同于以往的PECVD和LPCVD工艺,本文提供了一种在fab厂更便于生成Si3N薄膜的薄膜沉积方式,利用磁控溅射沉积Si3N4+CMP+炉退火来得到具有低损耗和较高质量的薄膜。

前面我们已经分享了利用LPCVD和PECVD制造高质量Si3N4的方法,但是前面各种方式各有其优缺点

LPCVD+CMP+炉内回火:(有工艺平台)

优点:薄膜质量最好

缺点:高温沉积和退火工艺会导致掺杂剂扩散并损坏预制的温度敏感器件。对于后端 (BEOL) 制造工艺、协同集成等应用来说非常具有挑战性具有前端生产线 (FEOL) 硅光电电路和代工兼容工艺。

PECVD/ICP-PECVD+CMP+炉内回火:(有工艺平台)

优点:可以实现低温沉积

缺点:由于 Si─H 和 N─H 键的吸收,电信波长下沉积薄膜内的光学损耗通常很高(通常为 200 dB m −1 )对光学应用提出了挑战。为了解决这个问题,使用氘化硅烷 (SiD 4 ) 作为沉积前驱体,而不是传统的 SiH 4 、显示 10 dB m −1 传播损耗。然而,SiD 4 前驱体在铸造厂中并不常见,而且价格昂贵,这可能会使这种沉积方法对于大规模低损耗波导制造缺乏吸引力。

PVD+CMP+炉内回火:(有SIN靶材)

本文介绍的就是这种工艺,易于获取的SiN靶材,较低的沉积温度,经过后到工序得到的相对较好的薄膜质量。

划重点:

针对氮化硅光波导--我们可以提供

1.Si+Sio2(湿法热氧)+Si3N4(PECVD/LPCVD/ICP-PECVD/PVD)晶圆(LPCVD最大12寸)2.CMP+快速退火/炉退火3.一站式服务

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜方式(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束直写等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

EBL代工(非晶硅,TiO2,SiO2,GaN,Ta2O5,Al,Au,GaAs(PCSEL)...更多材料体系),母版制作,铬版销售,纳米压印,DUV光刻超结构服务,

激光器芯片/探测器芯片/PIC芯片封装耦合服务"芯片类型:激光器/探测器/PIC芯片(硅光,铌酸锂,氮化硅)"封装形式:TO封装/BOX封装/蝶形封装/COB封装/PIC芯片封装"应用市场:光通信/激光雷达/量子通信/陀螺仪/生物传感/量子计算等其他,独特优势:封装技术人员具有10+年的封装经验,具有成熟的封装研发及量产经验,参与过多款铌酸锂、硅光,窄线宽激光器等产品的量产同时能够提供热仿真,光学仿真等技术支持,提供全套的封装解决方案。同时基于我们在业内10+年的行业经验,对于供应链,原材料(热沉,透镜棱镜,光纤阵列,陶瓷管壳等)的选型,采购,使用,具有极其成熟的经验,可以有效地解决封装过程中遇到的各种问题,大大降低试错成本。

请联系小编免费获取原文,也欢迎交流半导体行业,工艺,技术,市场发展!

低温溅射超低损失硅氮化物用于混合光子集成

摘要

硅氮化物-绝缘体(Si3N4)光子电路在许多应用中取得了巨大进展,例如芯片上的频率梳、激光雷达、通信和光谱学。

到目前为止,最佳的薄膜质量是通过低压化学气相沉积(LPCVD)和高温退火(1200°C)实现的。然而,高加工温度对Si3N4与预处理的硅电子和光子器件、绝缘体上的锂铌酸盐(LNOI)以及硅上的锗光电二极管的共集成提出了挑战。这限制了LPCVD作为前端线路的工艺。

在这里,基于室温反应溅射的超低损失Si3N4光子学被证明是可行的。经过400°C和800°C退火后,传播损耗分别达到了5.4 dB m^−1 和 3.5 dB m^−1,使得环形谐振器的光质量因子达到了超过1000万,并且平均质量因子为750万。据我所知,这是利用低温Si3N4获得的最低传播损耗。这种超低损耗使得微腔谐振器孤子频率梳的阈值功率达到了1.1 mW。引入的溅射工艺与前端硅电子和光子学完全兼容。这可以实现低损耗波导与集成激光器和绝缘体上的锂铌酸盐的混合三维集成。

1.导言

受微电子行业推动的互补金属氧化物半导体(CMOS)制造的成熟性、低成本性和可扩展性的影响,硅集成光子学在过去十年中为电信应用、激光雷达、集成光子传感器和量子计算等领域取得了显著进展。如今,通过与不同材料的混合集成,例如III-V-on-Si集成激光器、Ge-on-Si光电二极管、高速调制器和(去)复用器,硅光子集成电路已经展示出多样的光学功能。然而,硅的一些固有材料特性在特定工作模式下对硅光学器件的性能构成挑战。特别是硅在1550 nm处的双光子吸收限制了其高功率处理能力,高热光系数使得器件对温度变化敏感。

硅氮化物(Si3N4)在绝缘体上引起了极大的关注,作为具有超低传播损耗的光子集成电路的介质材料平台。

1.它具有宽广的透明度窗口,覆盖了可见光到中红外范围,

2.相对较高的非线性(比二氧化硅高出十倍),低热光系数,以及与CMOS兼容的制造工艺。

随着其显著的进展,它已经在芯片尺度的频率梳、激光雷达、光学通信、光谱学、芯片延迟线、传感等多个应用领域实现了广泛的应用。在这些应用中,除了需要低传播损耗外,色散工程和光学模式的高限制是至关重要的,通常需要波长超过600纳米的薄膜厚度。高Si3N4厚度导致了波导核心中模式的严格限制,并提供了各种优势,包括可忽略的弯曲损耗(占用空间小)、色散工程能力和高有效的Kerr非线性。这些特性在非线性光子应用中具有重要意义。

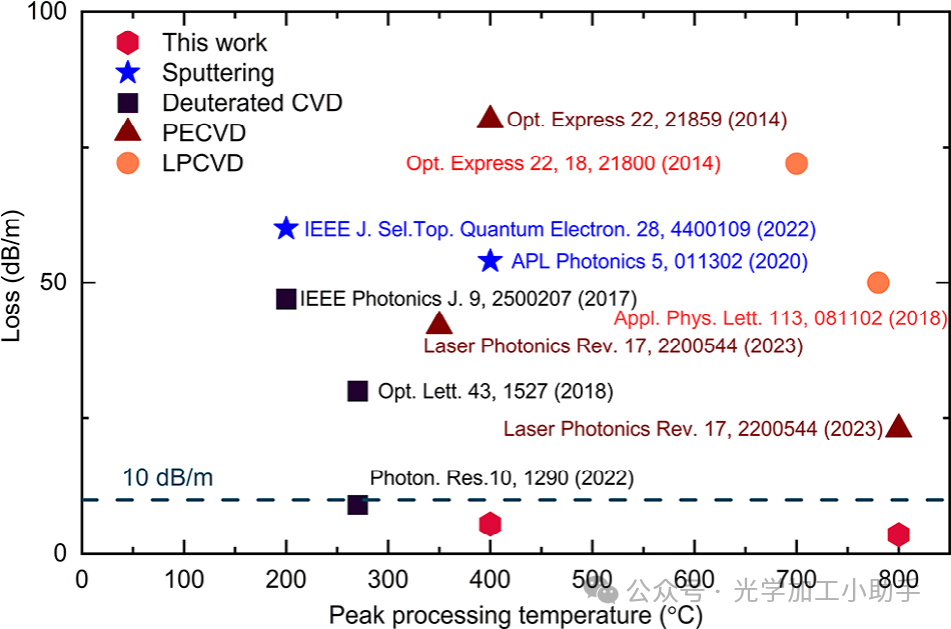

制备厚Si3N4薄膜有几种方法,例如LPCVD、等离子增强化学气相沉积(PECVD)、感应耦合等离子化学气相沉积(ICP-CVD)、反应溅射和原子层沉积(ALD)。到目前为止,通过高温(约800°C)的LPCVD沉积获得的Si3N4薄膜具有最佳的光学质量。

然而,由于LPCVD过程产生的高膜应力导致了致命的裂纹,并阻止了具有高光学质量的厚膜(>400纳米)的制备。因此,已经开发了几种巧妙而复杂的工艺,例如图案裂纹障碍、多步沉积和光子达马斯克工艺。特别是,长时间的高温退火(1200°C,持续>3小时)是必不可少的,以减少材料损耗并实现超低传播损耗(≈1 dB m−1)。这种超低损耗使得芯片上的Si3N4谐振器的光学品质因子超过1000万。然而,高温沉积和退火过程可能导致杂质扩散,并损坏预制的温度敏感器件。

因此,LPCVD Si3N4在后线(BEOL)制造工艺、与前线(FEOL)硅光电路的共整合以及晶圆厂兼容的工艺中的应用非常具有挑战性。

近年来,低温沉积的Si3N4薄膜越来越受到人们在Si3N4与其他材料的3D混合集成中的关注。

在不同的低温沉积方法中,PECVD和ICP-CVD作为低温(<400°C)和CMOS兼容工艺被广泛使用,提供了不会出现裂纹的高厚度Si3N4薄膜(>1 µm)。

然而,由于Si─H和N─H键的吸收,沉积薄膜在通信波长处的光损耗通常很高(通常为200 dB m−1),这对光学应用构成了挑战。为了解决这个问题,已经开始使用重氢硅烷(SiD4)作为沉积前体,而不是传统的SiH4,显示出10 dB m−1的传播损耗。然而,SiD4前体在晶圆厂并不常见且昂贵,这可能使得这种沉积方法在大规模低损耗波导制造方面不太具有吸引力。最近,通过包含化学机械平坦化步骤,采用PECVD工艺而无需后热退火的状态下实现的最先进的传播损耗为42 dB m−1。另一种潜在的后线(BEOL)方法是低应力低温反应溅射制备低损耗Si3N4薄膜。在1550 nm处,波导损耗为80 dB m−1,并且具有6×105的内在光学品质因子的微环谐振器已经通过在环境气氛中进行400°C热退火而实现。

在这里,我们报告了利用室温反应溅射实现高厚度超低损耗Si3N4光子器件的结果。我们研究了溅射Si3N4薄膜在O波段、C波段和L波段波长范围内以及不同退火温度下的光传播损耗。在室温溅射和波导制造之后,Si3N4薄膜的损耗为32 dB m−1,没有经过热退火,而制造的微谐振器的内在光学品质因子(Q)为1580 nm处的110万。在400°C的CMOS兼容热退火步骤后,传播损耗显著降低到5.4 dB m−1,谐振器的Q在1580 nm处提高到620万。通过在800°C进行额外退火,薄膜质量进一步提高,实现了3.5 dB m−1的损耗,最高的Q因子超过1000万,平均Q因子为750万。为了证明谐振器在光子应用中的可行性,我们展示了在1310 nm处的阈值功率下的参数振荡。作为对硅氮化物薄膜光学性质的进一步验证,我们展示了在1.3 µm和1.5 µm波长处产生的耗散性克尔孤子频率梳。我们相信,具有超低光学损耗的低温溅射Si3N4将对可扩展的晶圆光子学和3D光子电路的混合集成产生重大影响。

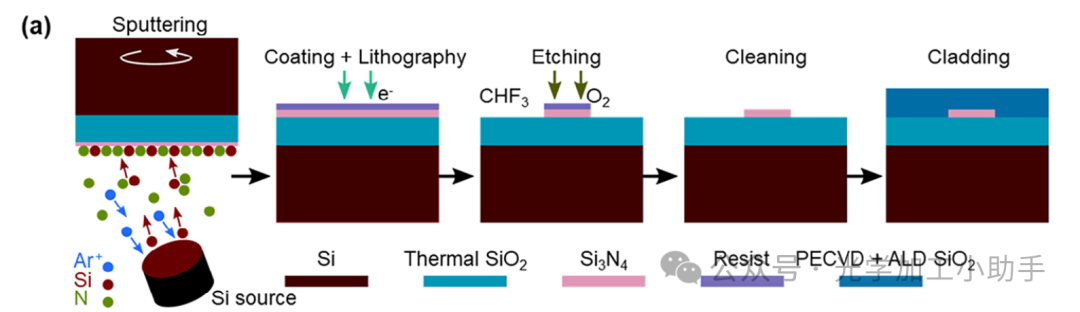

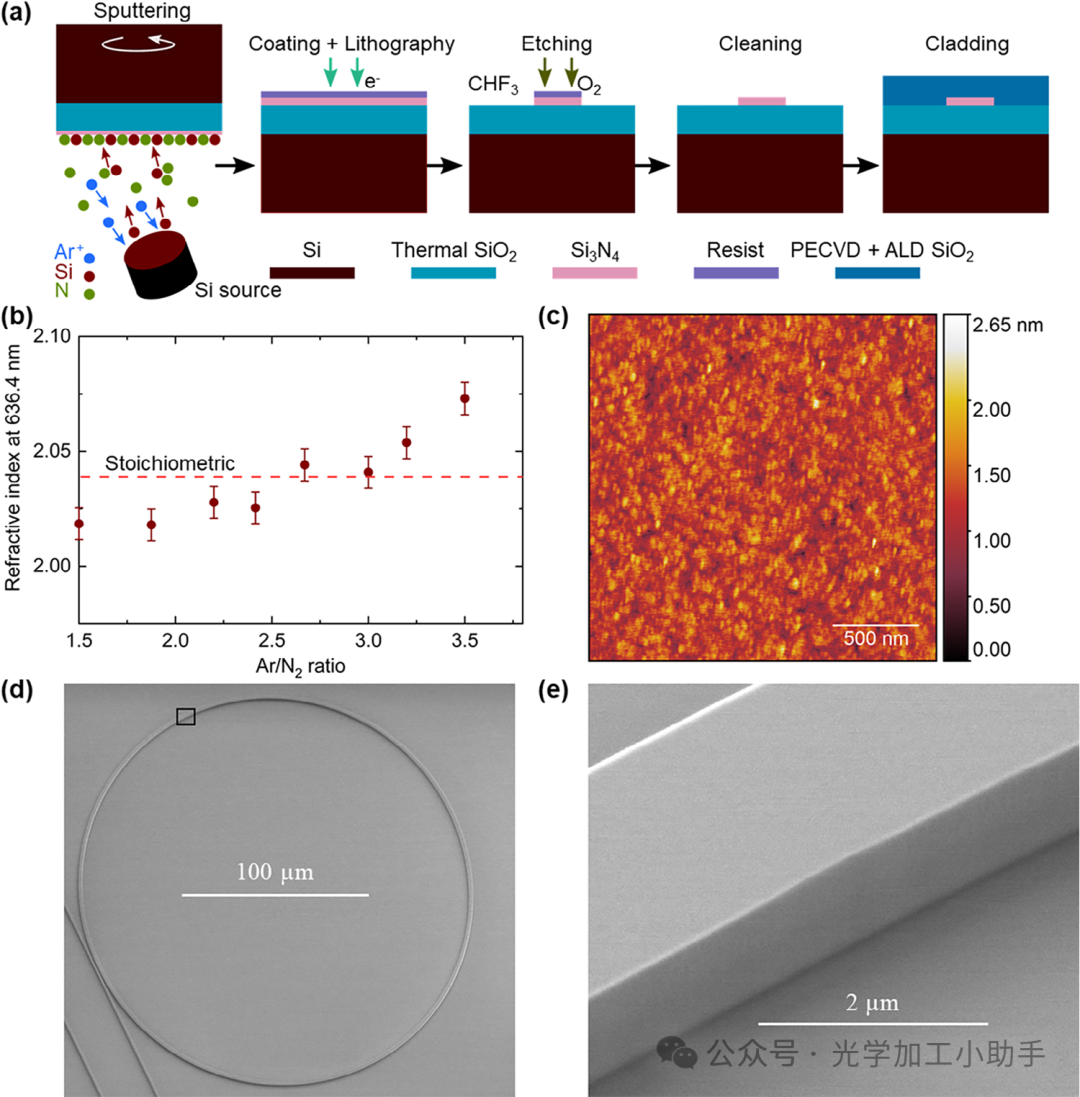

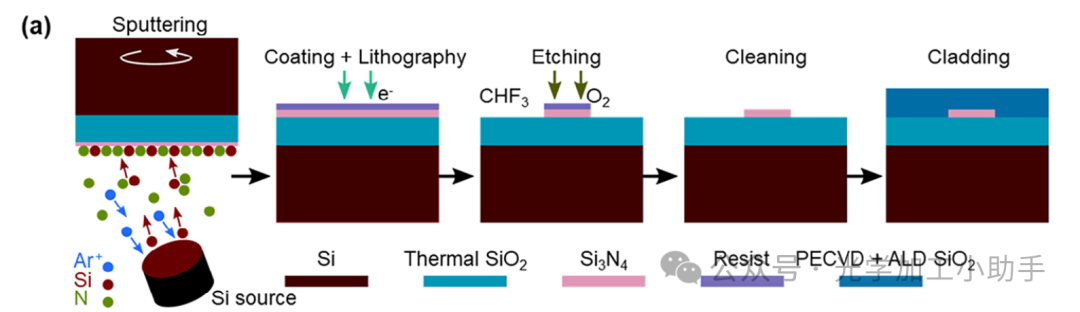

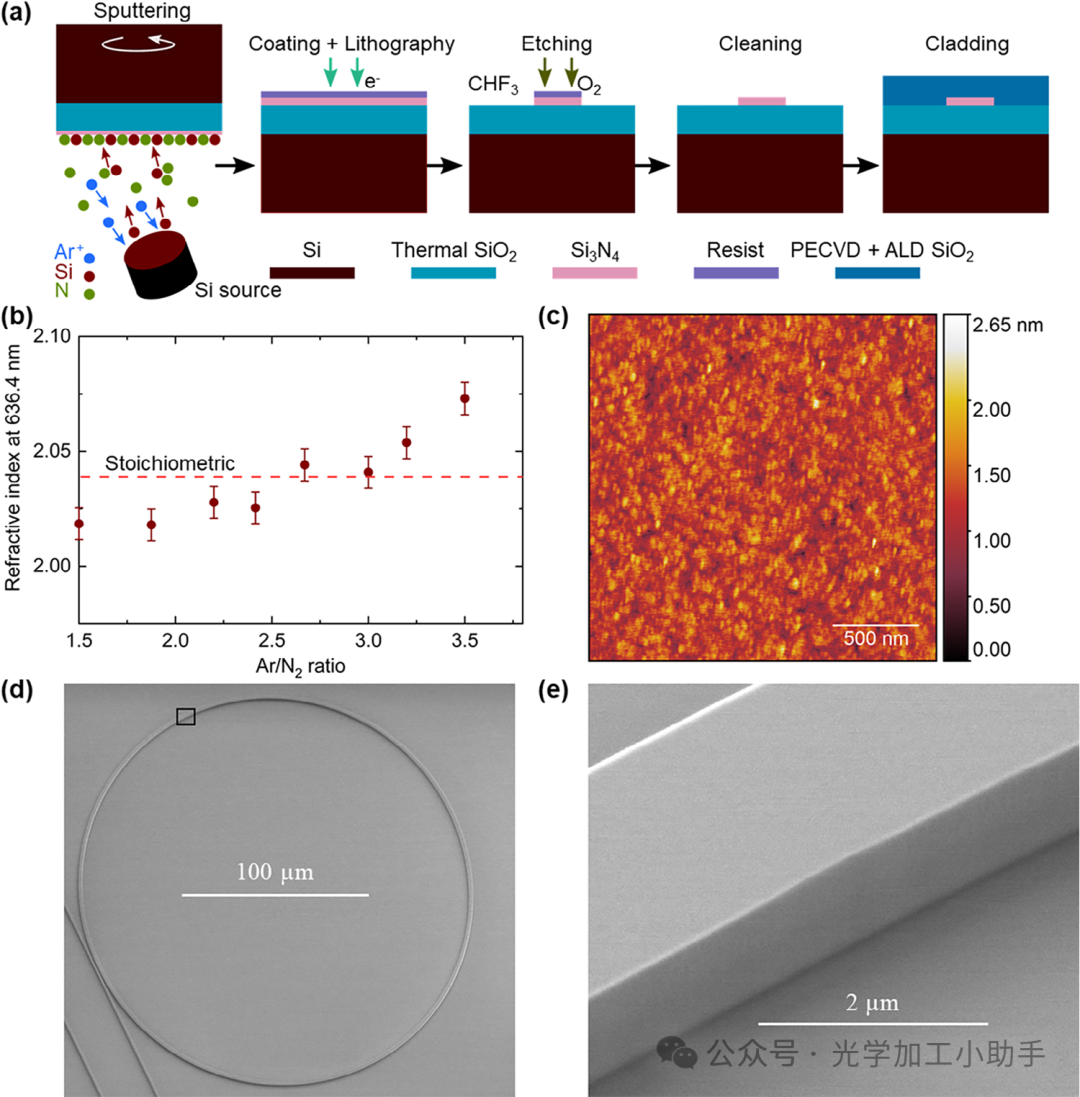

2 薄膜沉积和波导制备

图1a显示了从4英寸硅晶片开始的制备流程,其上有3µm厚的热氧化硅(SiO2)层。采用商业反应磁控溅射系统,在室温下沉积Si3N4薄膜,该系统配备了一个非对称双极脉冲直流源。使用直径为2英寸的磷掺杂硅靶作为溅射源。用于Si3N4沉积的是脉冲功率(100瓦直流),脉冲频率为50 kHz,占空比为75%。溅射过程发生在包含氩气(Ar)和氮气(N2)混合物的等离子体环境中。氩气以恒定的流量(15 sccm)作为溅射气体,有助于通过与靶表面高能碰撞,将硅原子喷射到环境中。在整个溅射过程中,腔室压力控制在3 mTorr,样品晶片的温度未稳定,保持在≈22°C(详见支撑信息第S1节)。需要注意的是,该过程本质上不含氢,从而避免了通过N─H或Si─H键的光学损耗(详见支撑信息第S2节)。图1b显示了溅射SiNx膜的折射率在636.4 nm处随Ar/N2比例的变化,以及一条虚线表示的化学计量Si3N4的折射率。根据目标折射率的不同,可以广泛调节Ar/N2比例,从而使SiNx的折射率从2.07(富硅)变化到2.01(富氮)。折射率是用棱镜耦合器(Metricon 2010 m)在636.4 nm处测量的。对于此处展示的制备样品,气体比例设置为≈2.7,以获得化学计量Si3N4,其结果折射率在636.4 nm处为≈2.04,沉积速率为130 nm/h。图1c显示了厚度为750 nm的溅射Si3N4膜的顶部表面粗糙度,通过原子力显微镜测量。均方根粗糙度为0.26 nm,与衬底的水平相同。溅射Si3N4膜用于制备微环谐振器,以通过测量谐振的光学品质因子来研究波导传播损耗,并探索在非线性光子学中的潜在应用。采用负性光阻(ma-N 2405)通过电子束光刻来图案化光学波导和微环。在显影后,采用含有CHF3(50 sccm)和O2(5 sccm)的蚀刻混合物,在15 mTorr和直流偏压240 V的条件下,通过感应耦合等离子体反应离子蚀刻完全蚀刻图案化的样品。图1d显示了100µm半径微环谐振器的扫描电子显微镜(SEM)图像,波导横截面为750 nm×1.8 µm。图1e显示了一个放大的环形波导的SEM图像,未见到侧壁粗糙度。不同波长范围下的不同耦合条件下,母线波导和环之间的间隙被调节。Si3N4蚀刻过程结束后,使用过氧化氢溶液去除残留的光刻胶。在此步骤之后,通过两个步骤沉积了一层3µm厚的SiO2层来封装样品。为了填充母线波导和微环之间的间隙而不产生气孔,首先采用温度为45°C的ALD沉积400 nm厚的SiO2层,然后采用PECVD在300°C的温度下沉积2.5µm厚的SiO2层。由于在Si3N4核心内有着严格的模式限制,PECVD SiO2层与光学模式的相互作用不显著,从而产生可忽略的损耗,同时具有成本效益和高沉积速率的优势。样品被切割成小片,以进行末端耦合来表征其光学特性,例如光学Q值、传播损耗和微谐

图1溅射Si3N4光子器件。a)溅射Si3N4光子器件的制备流程图。b)在636.4 nm处测量的溅射SiNx膜的折射率随Ar/N2比例的变化。c)750 nm厚的溅射Si3N4顶部表面粗糙度测量。d)100 µm半径微环谐振器的扫描电子显微镜(SEM)图像。e)环形波导的放大(d中的黑框)SEM图像。

3. 溅射硅氮化物薄膜和微腔谐振器的表征

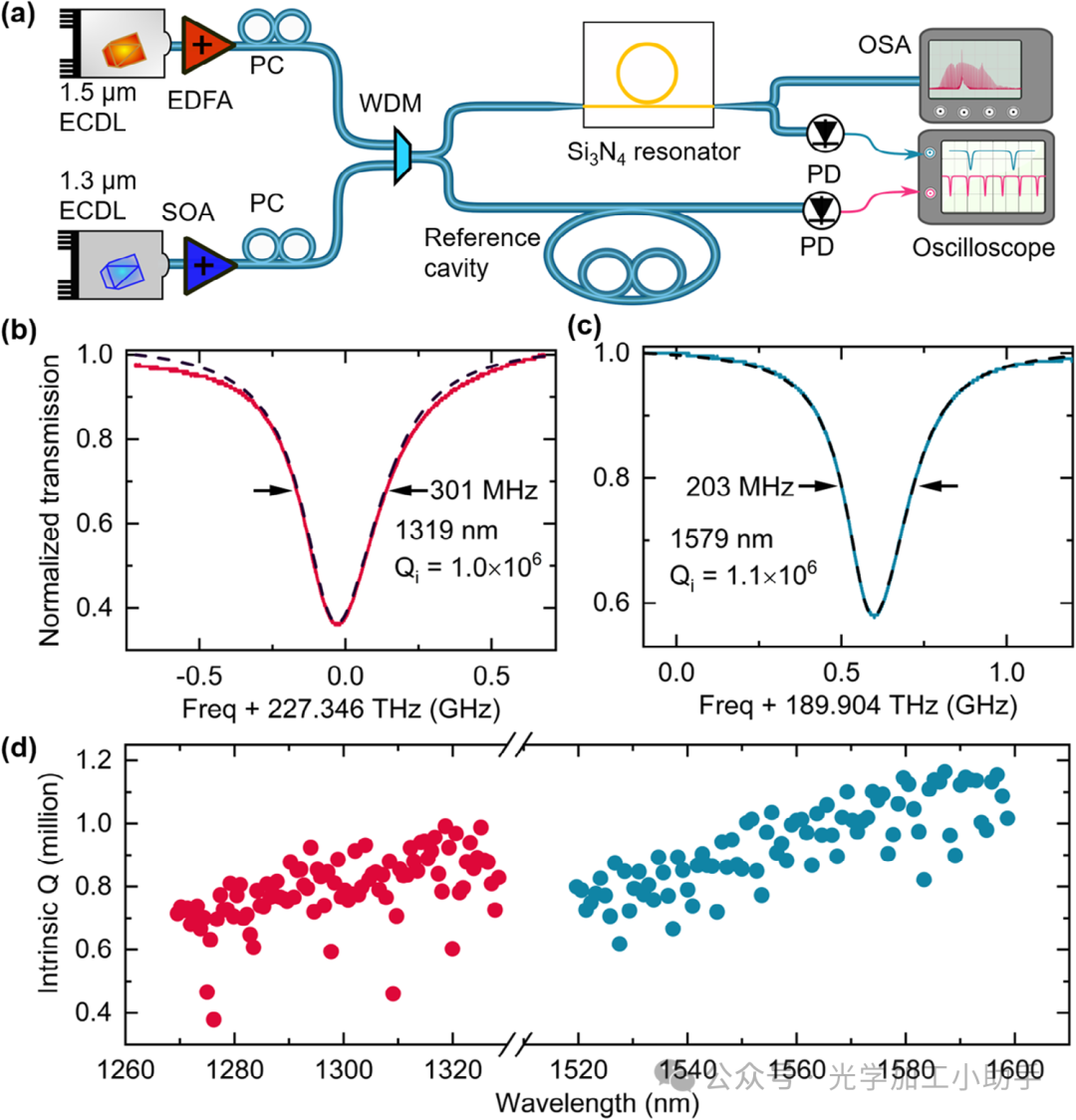

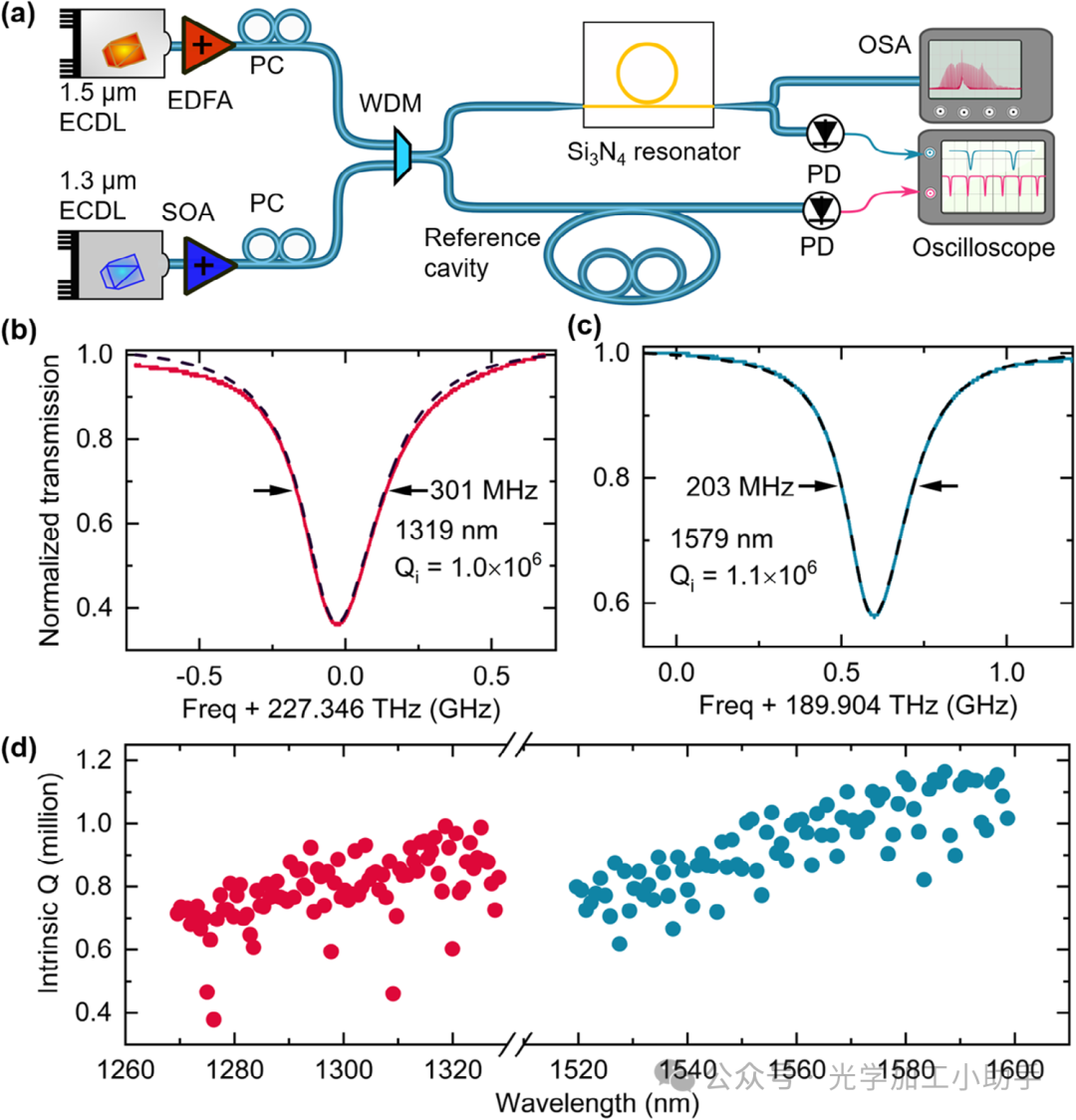

如图2a所示,使用两台可调连续波(CW)外腔二极管激光器在O波段和C-/L波段对溅射Si3N4微腔谐振器的光传输进行表征,并产生耗散克尔孤子微梳。CW光的偏振通过光纤偏振控制器进行调整,以探测Si3N4谐振器的准横电场(TE)或准横磁场(TM)模式。光通过两根带有透镜的光纤耦合进入和从谐振器中耦出。为了实现从光纤到波导的低耦合损耗,Si3N4波导的宽度锥形缩小至约200 nm(详见支持信息第S4节)。我们的实验中每个端面的耦合损耗小于2 dB。为了表征谐振器,两个CW激光器的光功率被设定为较低水平,以避免由热效应和克尔效应引起的谐振频移。两个CW激光器的频率以约1 THz/s的速度广泛扫描10 THz范围。为了在扫描过程中确定激光器的频率,我们使用高精度的校准光纤环腔提供频率标记。Si3N4谐振器和参考光纤腔的透射光谱同时由示波器记录。进一步的数据分析用于提取谐振器的光学品质因子、传播损耗和色散。

图2 对未进行后热处理的溅射Si3N4谐振器进行表征。a)用于表征Si3N4谐振器透射光谱、谐振器线宽、光学品质因子和色散的实验设置。在1318 nm处未进行热处理的Si3N4环谐振器的归一化透射光谱b)和1578 nm处c)。d)在激光波长范围内所有谐振的固有Q值测量。

3.1 未进行热处理的器件图2b展示了一个直径为200微米的Si3N4谐振器在1318.7 nm共振波长处的谐振光谱,图2c展示了另一个直径为200微米的Si3N4谐振器在1578.6 nm波长处的谐振光谱。这两个谐振器都是直接从室温溅射膜中制备而成,具有二氧化硅包层,但没有进行后热处理。图2b、c中的虚线是使用扩展耦合模理论拟合的谐振轮廓,显示在1319和1579 nm处的谐振线宽分别约为300和200 MHz,对应于1319 nm处的加载品质因子(Ql)为75万,1579 nm处为94万。考虑到这两个谐振器都是欠耦合的,计算得到的固有品质因子(Qi)分别为1319 nm处的100万,1579 nm处的110万。可以使用Qi来估计传播损耗α,其中α = f0/(Qi×R×FSR),其中f0是谐振频率,R是环谐振器的半径,FSR是微谐振器的自由光谱范围。在没有进行后热处理的情况下,制备的溅射Si3N4在O波段和L波段分别已经实现了42 dB m−1和32 dB m−1的传播损耗。这种传播损耗已经低于780°C下进行热处理的LPCVD Si3N4薄膜的传播损耗。图2d显示了在测量波长范围内谐振的Qi的分布,O波段的平均Qi为0.79 ± 0.11百万,C-和L波段为0.94 ± 0.13百万。

3.2 经过400°C热处理的器件

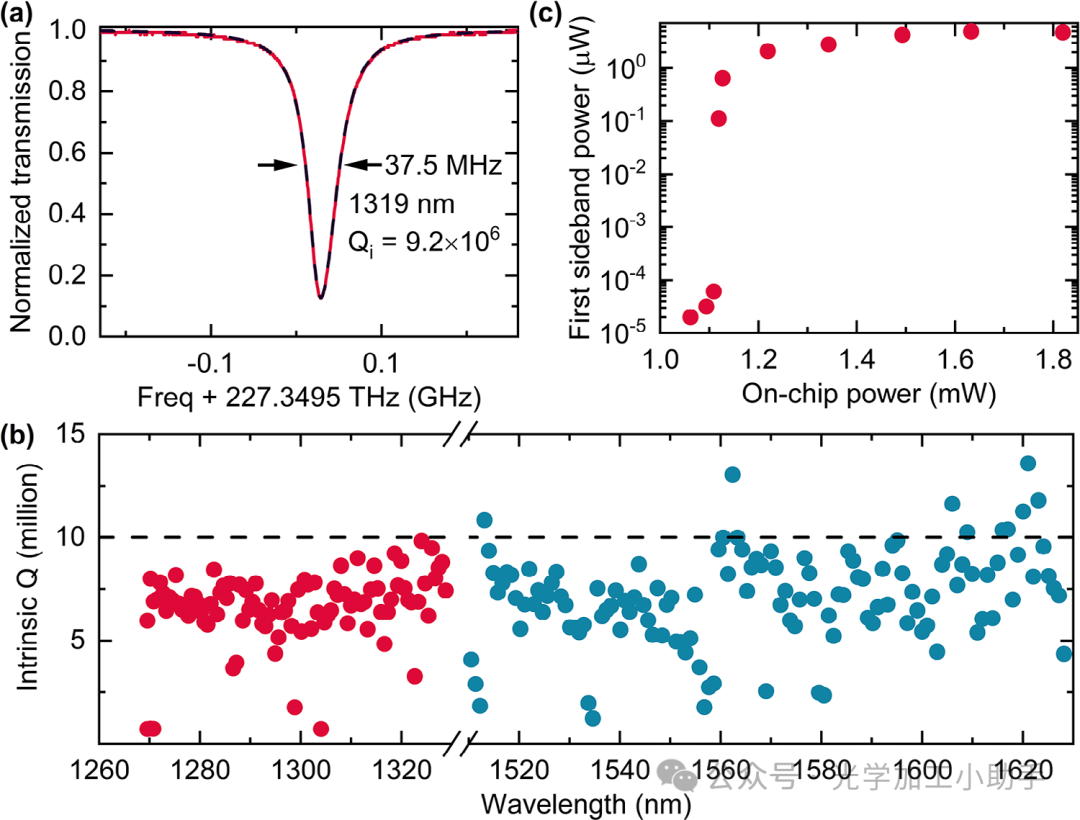

为了减少材料损耗,Si3N4器件在SiO2封装后进行了热处理。首先,我们在常温氛围中以400°C的温度处理器件8小时。选择400°C处理温度是因为它与CMOS兼容且与BEOL工艺兼容,可以用于将Si3N4与预加工的CMOS电子器件、III-V材料和预制的光子电路集成,例如铌酸锂在绝缘体上、硅上的锗光电二极管和活性硅调制器。图3a,b展示了直径为200微米的Si3N4谐振器在共振波长1328和1610 nm处的两个基本TE模式的归一化谐振透射光谱,以及与拟合线形状(虚线)一起。与图2b,c相比,经过400°C退火后,载荷谐振线宽明显缩窄至约55 MHz。考虑到该器件在整个测量范围内设计为欠耦合,因此在1328和1610 nm处计算得到的固有Q值分别为460万和620万,相应的传播损耗分别为1328 nm处的9.0 dB m−1和1610 nm处的5.4 dB m−1。与没有热处理相比,这是传播损耗的约五倍改善。图3c显示了被测谐振器的基本TE模式的固有Q值分布,涵盖了O波段和C+L波段的波长范围。O波段中的固有传播损耗保持大致稳定,平均Qi为3.8 ± 0.7百万。我们观察到一些低Q模式,这是由于模式交叉造成的(有关详情,请参阅支持信息第5节)。相比之下,C波段中的固有损耗略高于L波段,我们推测这是由于材料中残余损耗造成的(有关详情,请参阅支持信息第2节)。在C波段和L波段之间的平均Qi为3.6 ± 1.3百万。据我们所知,这是报道的使用最高处理温度为400°C的Si3N4传播损耗最低的情况。

图3 经过400°C热处理后的直径为200微米的Si3N4环谐振器的Q值测量。a)在1328 nm处的基本TE模式和b)在1610 nm处的基本TE模式的归一化透射光谱,均为直径为200微米的环谐振器。c)O波段和C/L波段内基本TE模式的固有Q值测量。

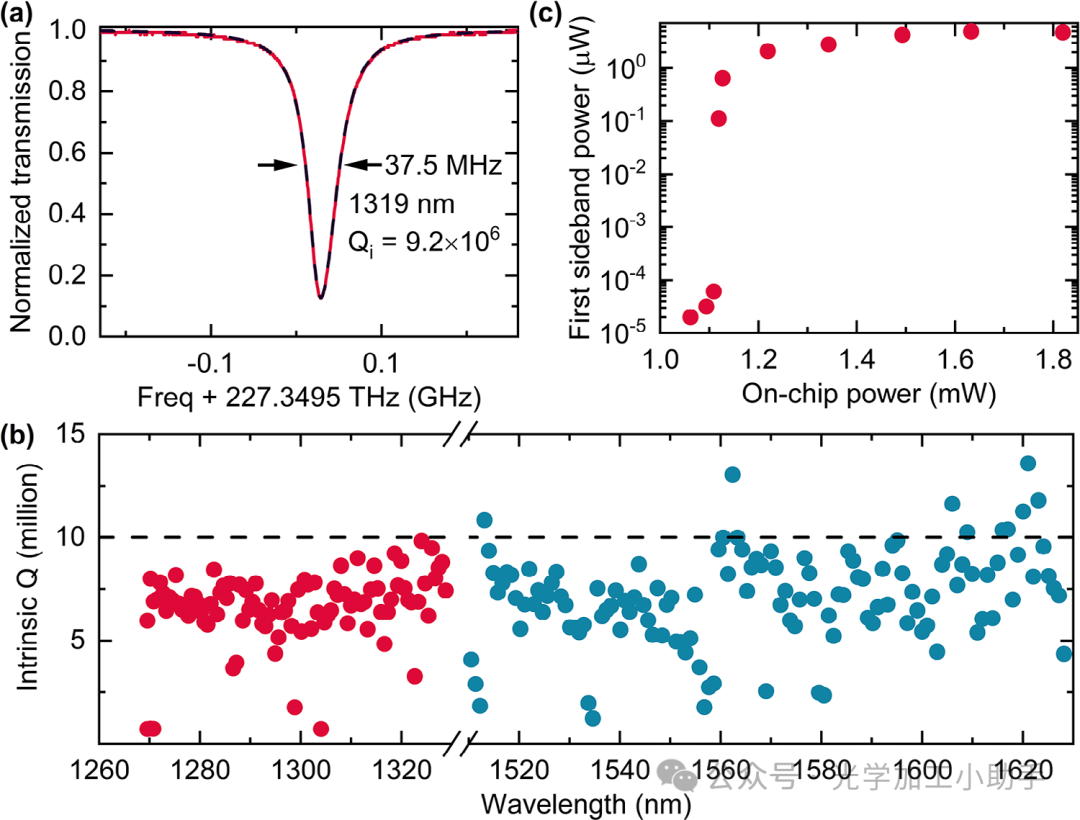

3.3 经过800°C热处理的器件

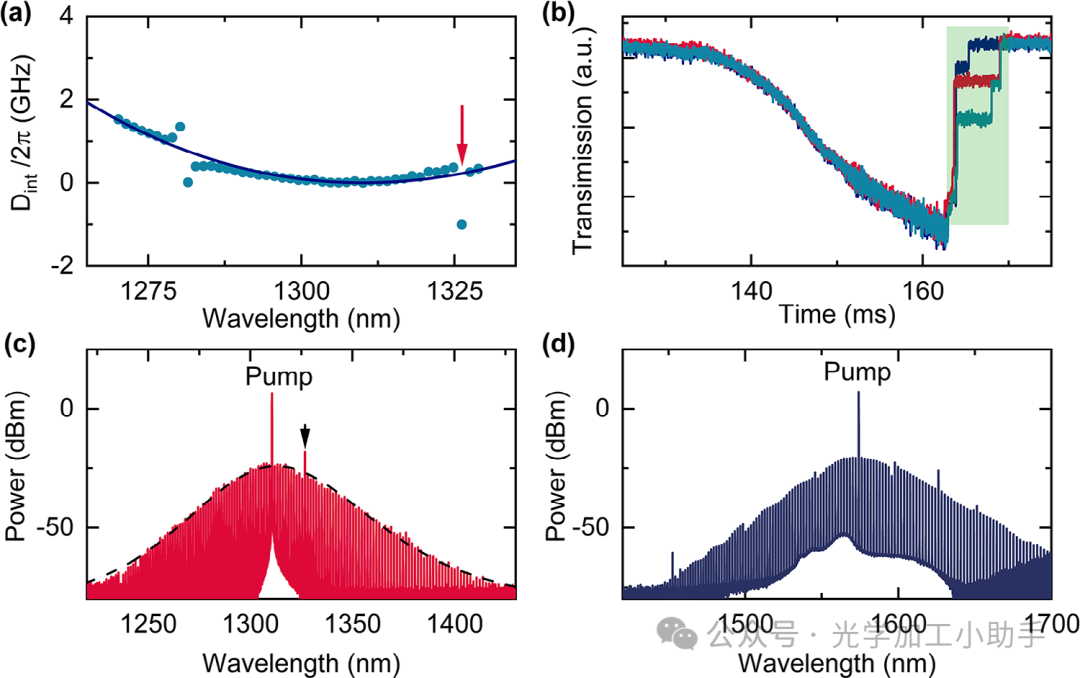

为了进一步减少喷射Si3N4膜的材料损耗,我们以更高的800°C温度对器件进行退火。这种处理温度可以实现未来将喷射Si3N4与硅集成光子学的集成,例如Si调制器[43]和硅锗光电二极管[44]。在封装后,器件在800°C下进行了8小时的后退火处理。图4a显示了一个直径为200微米的Si3N4谐振器在共振波长1319 nm处的归一化谐振透射光谱,其中谐振接近临界耦合但仍处于欠耦合状态,以及一个拟合的线形状(虚线)。载荷谐振线宽约为37.5 MHz。计算得到的载荷和固有Q值分别为610万和920万,相应的传播损耗为4.5 dB m−1。与400°C热处理后的损耗相比,1319 nm处的损耗约减半。图4b显示了谐振器基本TE模式的固有Q值在不同波长范围内的分布。从图4b可以看出,L波段中一些模式的固有Q值超过1000万,相应的传播损耗小于3.5 dB m−1。有关L波段的归一化谐振透射,请参阅第6节(支持信息)。与图2c类似,O波段中的固有传播损耗保持几乎不变,平均固有Q为7.0 ± 1.8百万,除了一些由于模式交叉而导致的低Q模式。C波段和L波段中的固有Q分布与图3c中的Q分布明显不同。经过800°C热处理后,C波段和L波段的固有损耗在图4b中呈现出大致恒定的趋势。这表明800°C退火可以有效地减少C波段中的材料损耗。穿越C波段和L波段的平均固有Q为7.5 ± 2.2百万。在图5中,我们将我们的结果与其他最新的高膜厚(> 600 nm)低温Si3N4沉积方法进行了比较。据我们所知,这是以800°C的峰值处理温度报道的Si3N4传播损耗最低的情况。为了进一步验证我们Si3N4环谐振器的超高光学Q值,我们测试了Kerr非线性光参量振荡(OPO)的阈值光功率。阈值功率是通过在芯片上光功率变化时测量两个生成的光侧带之一的光功率来确定的。图4c显示了在一个直径为130微米、载荷Q为550万和固有Q为900万的环谐振器中抽运1312 nm波长的光模式时的实验结果,显示了一个约为1.1 mW的阈值功率。通过有效面积Aeff = 0.99 µm2(从COMSOL Multiphysics模拟获得)和Kerr非线性系数n2 = 2.4×10−19 m2 W−1[27],计算得到的阈值功率为1.06 mW,与观察到的1.1 mW的阈值功率相吻合。

图4 经过800°C热处理的器件的Q值测量。a)直径为200微米的环谐振器中1319 nm基本TE模式的归一化透射光谱。b)O波段、C波段和L波段中基本TE模式的固有Q值测量。c)130微米半径环谐振器的光参量振荡阈值功率测量。

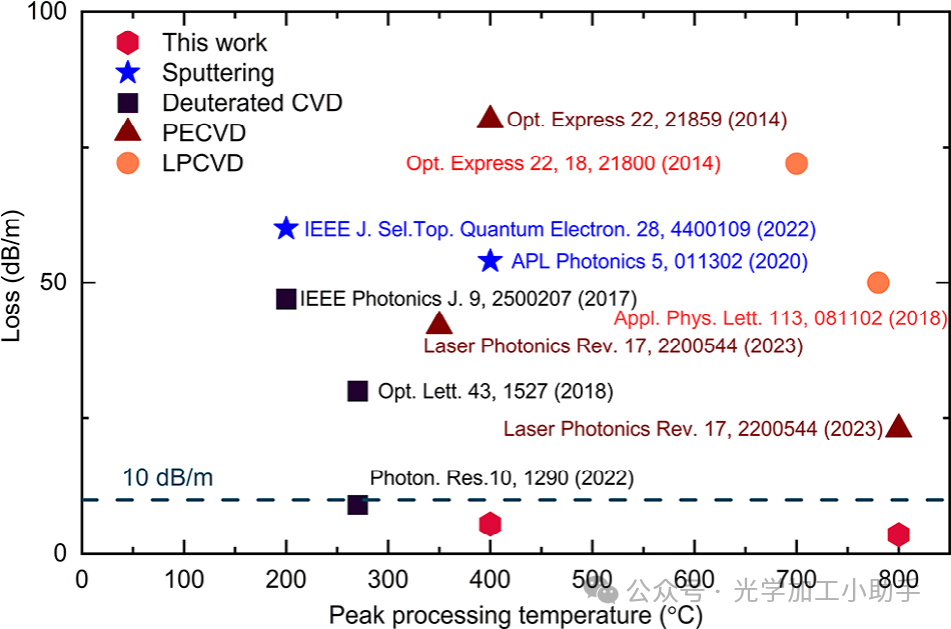

图5 与其他最新技术的传播损耗比较,基于低温硅氮化物沉积技术,薄膜厚度较高(>600纳米),包括无退火的LPCVD、PECVD、溅射和基于ICP-CVD的氘化硅氮化物。我们的结构在常温下在环境大气中退火8小时。

除了OPO阈值功率测量外,我们采用最近开发的一种方法[45]来探索经过800°C热处理后溅射微腔的材料损耗限制的Q因子。我们进行了测量,以研究共振频率随腔内光功率循环变化和微腔温度变化的响应。此外,我们还测量了克尔效应和光热效应之间的共振频率变化比率。基于有限元方法模拟的结果(COMSOL Multiphysics),我们确定了我们的谐振器在1550 nm波长下在800°C退火后的材料损耗限制的Q因子约为20.5 ± 1.9百万。有关详细的实验和模拟,请参阅支持信息的第7节。此值超过了所呈现的内在光学品质因子。因此,我们预期表面粗糙度的降低可以进一步减少我们Si3N4结构中的光损耗。这与现有文献的发现一致。[27, 45]我们的测量表明,散射损耗对光学品质因子的限制约为1000万。鉴于低温下的退火过程不能有效地减轻散射损失,尤其是考虑到我们研究中使用的相对温和的热处理(<400°C),远远低于Si3N4的软化温度(1900°C),我们假设在温度低于400°C时,品质因子主要受材料损耗的限制。

4 溅射Si3N4中的孤子频率梳生成

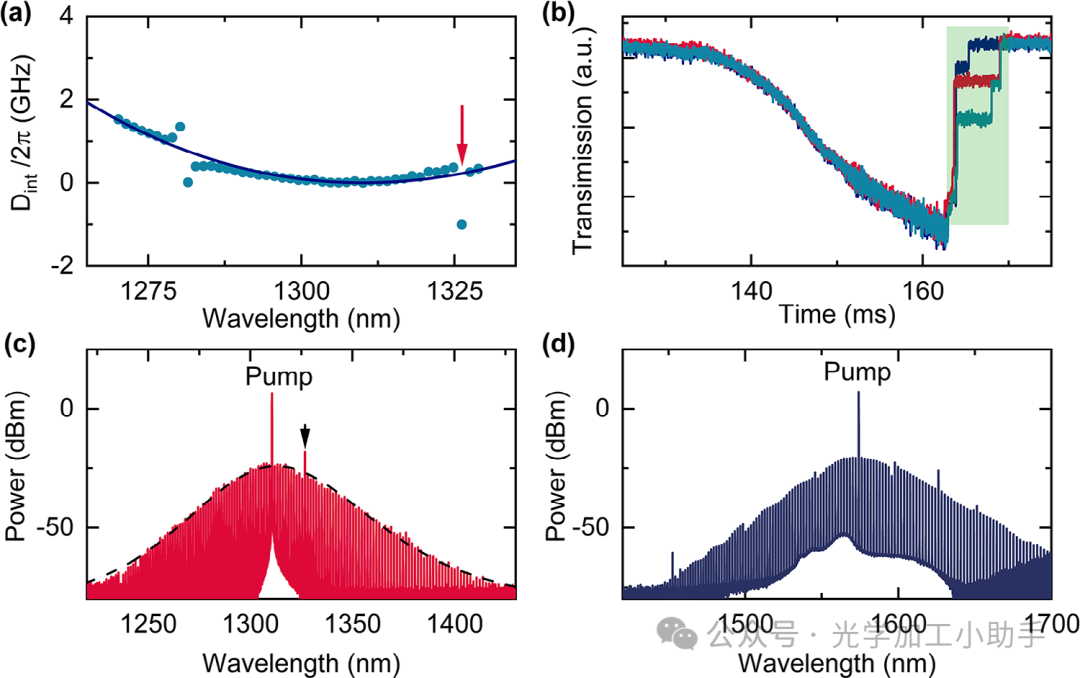

在本节中,我们使用制造的Si3N4微腔来生成孤子频率梳。我们首先测量了一个截面为750 nm × 1.8 µm的100 µm半径谐振器的色散。谐振器中一个模式族的共振频率可以用泰勒级数描述为[26,46]

图6 溅射Si3N4谐振器中的孤子频率梳生成。a)在泵浦波长为1310 nm时测得的集成色散曲线(蓝色圆圈),以及二阶多项式拟合曲线(蓝色轨迹)。b)当从共振的蓝失谐侧向红失谐侧扫描1.3 µm泵浦激光频率时测得的传输轨迹。c)在1310 nm处泵浦的溅射Si3N4谐振器中生成的孤子频率梳的光谱,以及sech2包络拟合(黑色虚线轨迹)。d)在1574 nm处泵浦的孤子频率梳的光谱。

结论

总的来说,我们报道了利用室温反应溅射制备高膜厚的超低损耗Si3N4光子学器件。在无后续热退火的情况下,测得的传播损耗为32 dB m−1。经过CMOS兼容处理温度(400°C)的热退火后,膜损耗显著降低至5.4 dB m−1,使得在L波段制备的Si3N4环形谐振器具有620万的内在Q值。沉积过程本质上是无氢的,这可以防止光学损耗较高的氢键的形成。低温热退火后的超低损耗集成Si3N4器件可以与预处理的CMOS电子器件、硅集成光子学[7]和LNOI[49]实现完全单片后线集成。经过进一步的800°C热退火,膜损耗进一步降低至3.5 dB m−1,相应的微谐振器光学品质因子可超过1000万。这种性能也是报告的最低Si3N4传播损耗,其峰值处理温度为800°C。我们相信,我们低温溅射的Si3N4是向硅光子学的混合单片集成迈出的重要一步,可应用于电信系统、非线性光学、频率梳生成以及量子计算系统的扩展。